verilog

Verilog는 HDL(하드웨어 설명 언어) 유형입니다. Verilog는 교육 및 비즈니스에서 FPGA 및 ASIC을 설계하는 데 사용하는 두 가지 언어 중 하나입니다. FPGA 및 ASIC의 작동 방식에 익숙하지 않은 경우 이 페이지에서 FPGA 및 ASIC에 대한 소개를 읽어야 합니다. Verilog와 VHDL은 가장 널리 사용되는 두 가지 HDL입니다. Java 또는 C와 같은 기존 소프트웨어 언어와 비교할 때 Verilog는 매우 다르게 작동합니다. 간단한 예를 보고 시작하겠습니다.

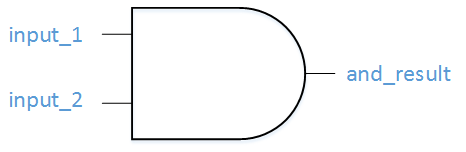

먼저 설명하는 Verilog 파일을 생성합니다. 앤 게이트. 간단히 말해서 And Gate에는 두 개의 입력과 하나의 출력이 있습니다. 두 입력이 모두 1일 때만 출력이 1이 됩니다. 아래는 Verilog로 설명할 And Gate의 사진입니다.

앤드 게이트

앤드 게이트 가자! Verilog의 기본 단위 중 하나를 와이어라고 합니다. 지금은 와이어가 0 또는 1만 될 수 있다고 가정하겠습니다. 다음은 몇 가지 기본 와이어 로직입니다.

wire and_temp; assign and_temp = input_1 & input_2;

코드의 첫 번째 줄에 and_temp라는 와이어를 만들고 있습니다. 코드의 두 번째 줄에서 우리는 우리가 만든 와이어를 취하고 할당합니다. 와이어. 이를 할당하기 위해 Verilog에서 앰퍼샌드(&)인 부울 AND 함수를 사용하고 있습니다. 위에 표시된 코드를 설명한다면 "signal and_temp get input_1과 input_2를 AND 연산했습니다."

Input_1과 Input_2는 Verilog 코드의 이 부분에 대한 입력입니다. 입력 및 출력의 전체 목록을 보여 드리겠습니다. 이것은 모듈에서 수행됩니다. 정의. Module은 정의된 입력 및 출력으로 코드 블록 생성을 보여주는 Verilog의 예약된 키워드입니다.

module example_and_gate

(

input_1,

input_2,

and_result);

input input_1;

input input_2;

output and_result;

이것은 기본 모듈입니다. example_and_gate라는 모듈과 3개의 신호, 2개의 입력 및 1개의 출력을 정의합니다. 모든 것을 모아 파일을 완성합시다. 우리가 놓치고 있는 유일한 것은 출력 and_result의 할당입니다. . 또 다른 참고 사항은 // Verilog에서 주석으로 사용됩니다.

///////////////////////////////////////////////////////////////////////////////

// File Downloaded from http://www.nandland.com

///////////////////////////////////////////////////////////////////////////////

module example_and_gate

(

input_1,

input_2,

and_result);

input input_1;

input input_2;

output and_result;

wire and_temp;

assign and_temp = input_1 & input_2;

assign and_result = and_temp;

endmodule // example_and_gate

축하합니다! 첫 번째 Verilog 파일을 만들었습니다.

바보 같은 게이트를 만들기 위해 많은 코드를 작성해야 했던 것 같습니까? 우선, 게이트는 바보가 아닙니다. 둘째, 맞습니다. HDL은 비교적 간단한 작업을 수행하기 위해 많은 코드를 사용합니다. Verilog가 VHDL보다 최소한 덜 장황하다는 사실에서 약간의 위안을 얻을 수 있습니다. 소프트웨어에서 매우 쉬운 작업을 수행하면 Verilog 또는 VHDL과 같은 HDL에서 훨씬 더 오래 걸린다는 사실에 익숙해지십시오. 그러나 일부 소프트웨어 담당자에게 Conway의 Game of Life를 표시하는 VGA 모니터에 이미지를 생성하도록 요청하고 그들의 머리가 놀라움에 회전하는 것을 지켜보십시오! 그건 그렇고, 그 비디오는 FPGA로 생성됩니다. 당신은 곧 그렇게 할 수 있을 것입니다!

verilog

Verilog는 하드웨어 설명 언어이며 설계자가 RTL 설계를 시뮬레이션하여 논리 게이트로 변환할 필요가 없습니다. 시뮬레이션이 필요한 이유는 무엇입니까? 시뮬레이션은 RTL 코드가 의도한 대로 동작하는지 확인하기 위해 다른 시간에 다른 입력 자극을 설계에 적용하는 기술입니다. 기본적으로 시뮬레이션은 설계의 견고성을 검증하기 위해 잘 따라야 하는 기술입니다. 또한 가공된 칩이 실제 세계에서 사용되는 방식과 다양한 입력에 반응하는 방식과 유사합니다. 예를 들어, 위의 디자인은 출력 pe 보여진 바와 같이. 시뮬레이션을 통해

디자인 module pr_en ( input [7:0] a, input [7:0] b, input [7:0] c, input [7:0] d, input [1:0] sel, output reg [7:0] out); always @ (a or b or c or d or sel) begin if (sel == 2b00) out <= a; else if