verilog

모든 행동 코드는 module 안에 작성됩니다. 및 endmodule . 따라서 생성하려는 디지털 디자인이 무엇이든 module 차단하다. 포트가 정의되어 있을 수도 있고 없을 수도 있습니다. 신호가 input로 블록에 들어가는 것을 허용합니다. 또는 블록을 output로 이스케이프 처리하십시오. .

아래 예에서 빈 모듈을 testbench라고 합니다. . 영숫자여야 하고 '_'를 포함할 수 있다는 점을 제외하고 원하는 대로 이름을 지정할 수 있습니다.

<노스크립트>

module testbench;

endmodule

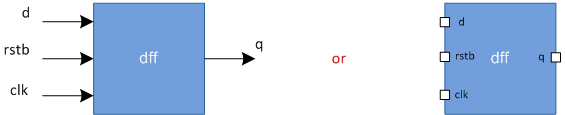

다른 모듈을 살펴보겠습니다. 몇 가지 신호(d, clk, rstb ) 입력으로 선언되고 q 출력으로 선언되었습니다.

<노스크립트>

module dff (input d,

clk,

rstb,

output q);

endmodule

모듈이 어떻게 생겼는지 보았으므로 이제 테스트벤치 모듈을 다시 한 번 살펴봄으로써 모듈 내부에 무엇이 들어갈 수 있는지 봅시다. Verilog에는 주로 두 가지 유형의 데이터 유형이 있습니다.

reg 데이터 유형은 변수와 같은 값을 유지하는 데 사용되는 반면 wire 지속적으로 구동되어야 하는 전선과 유사합니다. 따라서 일반적으로 wire 여러 모듈 및 기타 신호를 연결하는 데 사용됩니다.

module testbench;

reg d;

reg rst_b;

reg clk;

wire q;

endmodule

Verilog에는 세 가지 기본 블록이 있습니다.

always @ (상태 ) | 조건이 충족될 때 항상 실행 |

initial | 시뮬레이션이 시작될 때 한 번만 실행됩니다. |

assign [좌측] =[우측] | RHS가 변경될 때마다 LHS 값이 업데이트됩니다. |

Verilog를 작성할 때 명심해야 할 몇 가지 규칙이 있습니다:

reg initial에만 할당할 수 있습니다. 및 always 블록wire assign을 통해서만 값을 할당할 수 있습니다. 성명서begin .. end로 래핑되어야 합니다.

module testbench;

reg d;

reg rst_b;

reg clk;

wire q;

initial begin

d = 0;

rst_b = 0;

clk = 0;

#100 $finish;

end

always begin

#10 clk = ~clk;

end

endmodule

참고 위에 표시된 예에서 다음:

initial에 여러 줄이 있기 때문에 차단, 시작 그리고 종료 사용됩니다reg 유형이므로 초기 블록 내에서 할당됩니다. always에 대한 조건이 없기 때문에 차단하면 C에서 무한 루프처럼 실행됩니다.clk = ~clk; 시계 값을 토글합니다. #10 가 명령문 앞에 있으면 시계는 10시간 단위마다 토글됩니다.$finish 시뮬레이션을 종료하는 방법입니다. 이 경우 100시간 단위로 실행되고 종료됩니다.verilog

매개변수는 다른 사양으로 모듈을 재사용할 수 있도록 하는 Verilog 구성입니다. 예를 들어, 4비트 가산기는 비트 수에 대한 값을 허용하도록 매개변수화될 수 있으며 모듈 인스턴스화 중에 새 매개변수 값이 전달될 수 있습니다. 따라서 N비트 가산기는 4비트, 8비트 또는 16비트 가산기가 될 수 있습니다. 함수 호출 중에 전달되는 함수에 대한 인수와 같습니다. parameter MSB = 7; // MSB is a parameter with a constant value 7 paramet

Verilog는 하드웨어 설명 언어이며 설계자가 RTL 설계를 시뮬레이션하여 논리 게이트로 변환할 필요가 없습니다. 시뮬레이션이 필요한 이유는 무엇입니까? 시뮬레이션은 RTL 코드가 의도한 대로 동작하는지 확인하기 위해 다른 시간에 다른 입력 자극을 설계에 적용하는 기술입니다. 기본적으로 시뮬레이션은 설계의 견고성을 검증하기 위해 잘 따라야 하는 기술입니다. 또한 가공된 칩이 실제 세계에서 사용되는 방식과 다양한 입력에 반응하는 방식과 유사합니다. 예를 들어, 위의 디자인은 출력 pe 보여진 바와 같이. 시뮬레이션을 통해