verilog

산업 제조

<노스크립트>

module johnson_ctr #(parameter WIDTH=4)

(

input clk,

input rstn,

output reg [WIDTH-1:0] out

);

always @ (posedge clk) begin

if (!rstn)

out <= 1;

else begin

out[WIDTH-1] <= ~out[0];

for (int i = 0; i < WIDTH-1; i=i+1) begin

out[i] <= out[i+1];

end

end

end

endmodule

module tb;

parameter WIDTH = 4;

reg clk;

reg rstn;

wire [WIDTH-1:0] out;

johnson_ctr u0 (.clk (clk),

.rstn (rstn),

.out (out));

always #10 clk = ~clk;

initial begin

{clk, rstn} <= 0;

$monitor ("T=%0t out=%b", $time, out);

repeat (2) @(posedge clk);

rstn <= 1;

repeat (15) @(posedge clk);

$finish;

end

endmodule

시뮬레이션 로그 ncsim> run T=0 out=xxxx T=10 out=0001 T=50 out=0000 T=70 out=1000 T=90 out=1100 T=110 out=1110 T=130 out=1111 T=150 out=0111 T=170 out=0011 T=190 out=0001 T=210 out=0000 T=230 out=1000 T=250 out=1100 T=270 out=1110 T=290 out=1111 T=310 out=0111 Simulation complete via $finish(1) at time 330 NS + 0

verilog

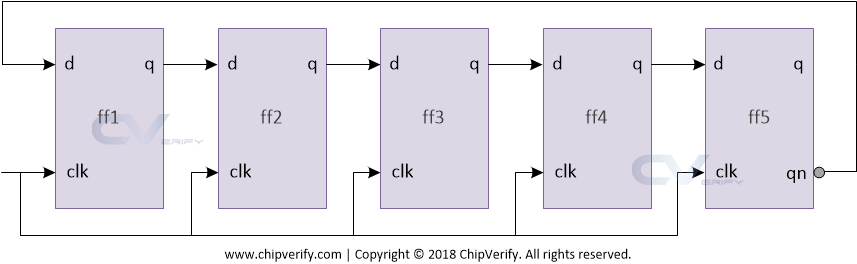

리플 counter는 첫 번째 플롭을 제외한 모든 플롭이 이전 플롭의 출력에 의해 클럭되는 비동기식 카운터입니다. 디자인 module dff ( input d, input clk, input rstn, output reg q, output qn); always @ (posedge clk or negedge rstn) if (!rstn) q <= 0; else

디자인 module ring_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= out[0]; for (int i = 0; i < WIDTH-1; i=i+1) begi