나노물질

산업 생산을 위한 비정질 인듐 갈륨 아연 산화물(a-IGZO) 기반 디스플레이 백플레인의 기술적, 경제적 장애물을 극복하기 위해 CL-ES(clean etch-stopper) 공정을 개발하여 a-IGZO 기반 박막을 제조합니다. 8.5세대 유리 기판(2200mm × 2500mm)에서 균일성과 재현성이 개선된 필름 트랜지스터(TFT) BCE(back-channel-etched) 구조의 a-IGZO 기반 TFT와 비교하여 새로 형성된 ES 나노층(~ 100nm)과 a-IGZO 나노층(30nm) 및 소스-드레인 동시 식각 전극층은 CL-ES 구조의 a-IGZO 기반 TFT 소자에 먼저 도입되어 대면적 디스플레이용 소자의 균일성과 안정성을 향상시킵니다. 8.05cm 2 의 포화 전자 이동도 /V 및 V 번째 0.72V의 균일성은 CL-ES 구조의 a-IGZO 기반 TFT 장치에서 구현됩니다. 3600초 동안 a ± 30V 바이어스에서 음의 바이어스 온도 조명 응력 및 양의 바이어스 열 응력 신뢰성 테스트에서 측정된 V 번째 CL-ES 구조화 소자의 이동은 - 0.51 및 + 1.94 V로 크게 감소했으며, 이는 BCE 구조화 소자(- 3.88 V, + 5.58 V)보다 훨씬 낮습니다. CL-ES 구조의 a-IGZO 기반 TFT 소자의 전기적 성능은 LCD 제조를 위해 실리콘 기반 TFT 공정에서 금속 산화물 반도체 기반 공정으로의 경제적 전환이 매우 실현 가능함을 의미합니다.

<섹션 데이터-제목="배경">더 높은 해상도와 더 큰 패널 크기를 가진 박막 트랜지스터(TFT) 백플레인은 평면 디스플레이 산업에서 매우 요구됩니다. 전자 이동도가 높은 반도체 재료는 TFT 백플레인의 성능을 향상시키는 데 중요합니다. 특히, 금속 산화물 반도체 기반 TFT 백플레인은 기계적 유연성 및 전자 이동성 측면에서 실리콘 기반 TFT 백플레인의 한계를 극복할 수 있는 유망한 후보로 간주됩니다[1,2,3,4]. 금속 산화물 반도체 기반의 TFT 백플레인은 유망한 특성을 보여주지만 산업적 응용을 위한 대규모 증착 모두를 위한 저비용 공정의 공정 방법이 여전히 필요합니다[5].

비정질 인듐 갈륨 아연 산화물(a-IGZO)은 높은 포화 전자 이동도(~ 5–10cm 2 )를 가진 우수한 금속 산화물 반도체입니다. /V s) 및 낮은 오프 전류(<10 pA) [6,7,8,9,10]. a-Si:H 기반 TFT 백플레인의 일반적인 산업 생산 방법은 5마스크 백 채널 에칭(BCE) 공정입니다. 그러나, a-IGZO 나노 필름은 현재 BCE 공정에서 사용되는 일반적인 에칭제에 대한 내화학성이 매우 낮습니다. 특히, a-IGZO 나노 필름은 인산, 질산 및 아세트산으로 구성된 Al 에칭액에 노출되면 몇 초 안에 완전히 에칭됩니다[11,12,13]. 이 제어할 수 없는 빠른 에칭은 -IGZO 기반 TFT 백플레인을 위한 BCE 프로세스의 채택을 방해합니다. BCE 구조의 백플레인에서 a-IGZO를 활용하기 위해 H2 기반의 Cu 배선 공정에 사용되는 etchant로 Cu 배선 기술이 개발되었습니다. O2 는 Al 배선에 사용되는 것보다 a-IGZO 나노필름에 훨씬 더 부드럽습니다[11, 13]. 불행히도 a-IGZO 나노 필름은 순한 에칭액을 사용하더라도 Cu 배선 공정 중에 여전히 손상됩니다. 더 순한 에천트는 TFT 장치의 후면 채널을 형성하는 a-IGZO 나노 필름의 표면에 손상을 줍니다. 이러한 손상은 a-IGZO 나노필름 표면 근처의 화학양론적 분자 조성비의 붕괴를 일으켜 대면적 디스플레이의 균일성 및 TFT 소자의 신뢰성을 악화시킨다. 현재까지, 기존의 6마스크 식각 스토퍼(CV-ES) 공정이 ESL(etch-stopper-layer) 구조의 a-IGZO 기반 TFT 백플레인을 제작하기 위해 개발되었습니다[14, 15]. 그러나 이 6마스크 ES 공정은 경제성에 부정적인 영향을 미칠 수 있다. 더욱이, 이렇게 증가된 박막 층 수는 층간 중첩 영역을 증가시키고 기생 정전 용량을 증가시키고 개구율을 감소시킨다[16,17,18]. 최근 하프톤 및 리프트오프 기술을 사용하여 TFT 백플레인을 생산하는 5마스크 ES 공정이 보고되었지만 활성층 표면이 여전히 노출되어 있기 때문에 이 공정은 a-IGZO 기반 TFT 백플레인 생산에 접근할 수 없습니다. 마지막 단계에서 스트리퍼 및 포토레지스트와 같은 공정 화학물질은 a-IGZO에 상당한 오염을 일으켜 장치 품질과 생산 수율을 감소시킬 수 있습니다[19,20,21]. 따라서, 균일성과 안정성이 높은-IGZO 기반 TFT 백플레인의 산업적 생산 방법은 여전히 어려운 과제로 남아 있습니다.

이 논문에서는 a-IGZO 기반 TFT 백플레인 제조를 위한 ESL 도입을 통한 깨끗한 5마스크 ES 공정(CL-ES)을 제안합니다. 이번에 새로 개발된 CL-ES 공정은 기존 BCE 장치 공정과 호환성이 높다. 이 CL-ES 공정은 BCE 공정과 동일한 마스크를 갖도록 설계되어 기존 AM-LCD TFT 백플레인 FAB의 생산성 손실을 무시할 수 있습니다. CL-ES 공정으로 제작된 a-IGZO 기반 백플레인은 게이트 절연체, IGZO 나노층, ES 나노층을 차례로 증착한 후 건식 식각 방식으로 새로운 ESL 마스크를 형성한다. 이것은 에칭액, 스트리퍼 및 용매로부터-IGZO 나노층 및 계면의 오염을 방지할 수 있다. 이 새로 형성된 나노 마스크는 TFT 장치의 균일성과 안정성을 향상시키는 데 도움이 됩니다. 기존의 BCE 구조의 소자에 비해 CL-ES 구조의 a-IGZO 기반 소자는 향상된 전기적 성능, 즉 더 높은 포화 전자 이동도, 높은 개구율 및 낮은 전력 소비를 나타냅니다.

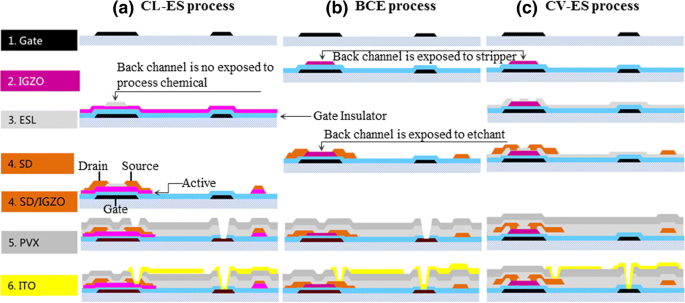

CL-ES 공정으로 제작된 ES 구조의 a-IGZO 기반 TFT 백플레인은 다음과 같았다(그림 1).

<그림>

(온라인 색상) a의 개략도 CL-ES, b 기원전 및 c CV-ES 프로세스

먼저 게이트 전극은 저항이 비교적 낮아 이중층(Mo/Cu:30nm/250nm)을 사용했습니다. 그런 다음 게이트 절연체인 질화규소(SiNx)/산화규소(SiOx)(300nm/100nm)를 플라즈마 강화 화학 기상 증착(PECVD) 방법으로 증착했습니다. 이 SiNx 필름은 Cu 금속화의 산화 및 Cu 이온이 게이트 절연체로 확산되는 것을 방지하도록 설계되었습니다. 이어서, SiOx 박막을 증착하였다. PECVD SiOx 필름의 증착 조건은 17-KW RF 전력, 1000mTorr 압력, 1:55 SiH4였습니다. /N2 O 가스 비율 및 350°C 온도. 그런 다음 dc 회전 마그네트론 스퍼터를 사용하여 a-IGZO 나노 필름을 30nm로 증착했습니다. 대상의 직경은 171mm이고 구성은 In2입니다. O3 :가2 O3 :ZnO =1:1:1 mol%. a-IGZO 나노 필름의 스퍼터링 매개변수는 5~ 9 × 10 -7 의 시스템 기본 압력이었습니다. Torr, 10KW의 rf 스퍼터링 전력, 5mTorr Ar/O의 스퍼터링 압력2 가스 혼합물(85% Ar-15% O2 ). 증착 온도는 실온입니다. 제작된 a-IGZO 필름은 깨끗하고 건조한 공기 환경에서 330°C에서 1시간 동안 어닐링됩니다.

둘째, PECVD 방법을 이용하여 ES(etch-stopper) 나노층(SiOx)을 증착하였다. ES 나노층을 동시에 증착하여 a-IGZO층의 오염을 방지합니다. BCE 공정과 마찬가지로 S/D 전극 패터닝 공정 이전에 a-IGZO 나노막에 대한 보호층이 없기 때문에 표면 오염, TFT 채널 형성 시 S/D etchant에 의한 a-IGZO 나노막 손상은 불가피하다. CL-ES 공정의 ES nano-layer는 TFT 채널을 외부 오염 및 손상으로부터 효과적으로 보호할 수 있습니다. ES 나노층은 100nm의 두께로 증착되었습니다. SiOx 박막의 증착 조건은 17-KW RF 전력, 1000mTorr 압력, 1:66 SiH4였습니다. /N2 O 가스 비율 및 240°C 온도. 제작된 ES 나노마스크는 건식 식각과 패터닝으로 식각되었다. 에칭 과정에서 CF4 및 O2 가스는 2000sccm/800sccm의 비율로 공급되었습니다.

셋째, S/D 전극에도 Mo/Cu/Mo를 사용하였다. -IGZO TFT의 S/D 전극을 선택하기 위해 금속과 a-IGZO의 일함수 차이를 고려하여 Ohmic contact와 저저항 물질을 형성하였다. Etch-stopper 공정에서 설명한 바와 같이 ES nano-mask의 패터닝 과정에서 Etch-stopper layer에 의해 보호되지 않은 a-IGZO nano-film은 이미 CF4 혈장. 따라서 Mo/Cu/Mo와 자연적으로 Ohmic 접촉이 형성된다[22]. S/D 층은 게이트 전극과 동일한 스퍼터링 조건으로 30nm/300nm/30nm의 두께로 증착되었습니다. 또한, Mo/Cu/Mo 및 a-IGZO의 다중 박막 층은 "H2를 사용하여 일괄 식각되었습니다. O2 S/D 전극을 완성하기 위해 "불화물 첨가제를 포함하는 기반 Cu 에천트". Cu 위에 추가된 30nm의 Mo는 패시베이션 홀 형성을 위한 건식 식각 시 다음 공정에서 패시베이션막(SiOx)에 의한 Cu 표면의 산화를 방지하고 Cu 표면의 플라즈마 손상을 방지하기 위해 형성되었습니다.

넷째, PECVD법을 이용하여 두 종류의 박막으로 분리된 패시베이션막을 증착하였다. 첫 번째 패시베이션은 SiOx 박막으로 만들어졌습니다. 박막의 두께는 250nm였습니다. 두 번째 패시베이션은 SiNx 박막으로 구성됩니다. 박막의 두께는 200nm였다.

다섯째, 화소전극으로 디스플레이 산업에서 가장 많이 사용되는 ITO(Indium Tin Oxide)막을 사용하였다. ITO 필름의 두께는 40nm였으며 증착에는 dc 스퍼터링이 사용되었습니다. 그런 다음 열풍 오븐을 사용하여 230°C의 깨끗한 건조 공기 환경에서 1시간 동안 최종 어닐링을 수행했습니다. 제조된 a-IGZO TFT의 전기적 특성은 키사이트 4082A 파라메트릭 테스트 시스템을 사용하여 측정되었습니다. 이 공정은 양산에 널리 사용되는 BCE 공정과 같은 수의 마스크(TN 제품 기준:5마스크)를 얻게 된다.

비교를 위해 BCE 구조의 a-IGZO 기반 TFT 백플레인을 BCE 공정으로 제작했습니다.

TFT의 I-V 측정은 반도체 특성 분석기를 사용하여 상온에서 수행되었습니다. NBTIS(Negative Gate Bias Temperature Illumination Stress) 하에서 TFT의 안정성을 평가하기 위한 분석 조건은 다음과 같다. V gs 및 V ds 각각 - 30 및 15V로 고정되었고 기판의 온도는 60°C로 유지되었습니다. NBITS의 휘도는 5000cd/m 2 로 설정되었습니다. . 평가 스트레스 기간은 3600초 동안 지속되었습니다[23]. 포지티브 게이트 바이어스 열 응력(PBTS)은 V에서 테스트되었습니다. gs 30V 및 V ds 15V이며 기판 온도는 60°C로 설정되었습니다. 평가를 위한 스트레스 기간은 3600초 동안 지속되었습니다[24].

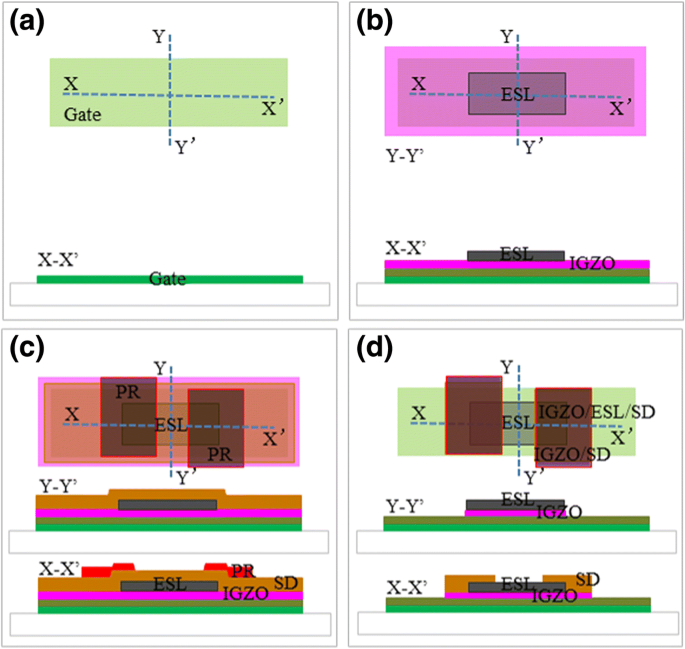

CL-ES 공정으로 제작된 a-IGZO 기반 TFT는 BCE 공정과 동일한 마스크 번호를 나타냅니다(그림 1). BCE 구조의 a-IGZO 기반 TFT와 비교하여 CL-ES 구조의 a-IGZO 기반 TFT는 두 가지 장점을 보여줍니다. (1) CL-ES 공정을 사용하여 생성된 a-IGZO 기반 백플레인은 게이트 절연체, a-IGZO nano -layer, ES nano-layer 순으로 형성한 후 건식 식각 방식으로 ESL nano-mask를 형성한다. 새로 형성된 100nm의 ESL 나노 마스크는 a-IGZO 나노 필름이 식각액, 스트리퍼 또는 포토레지스트에 노출되는 것을 방지할 수 있습니다. 따라서 층간 계면의 오염이 효과적으로 방지됩니다[25]. (2) 동시에, a-IGZO 나노필름은 ES층에 의해 보호되지 않고 CF4에 의해 충격을 받습니다. ESL 나노마스크 형성 동안 플라즈마는 전도체가 된다. 이는 다음 공정의 S/D 전극과 a-IGZO 반도체 사이에 자연스럽게 Ohmic contact를 형성하게 된다. 다른 부분의 경우, S/D 및 a-IGZO 나노층의 동시 에칭은 ESL-(a-IGZO+S/D 금속화) 층의 오버레이 허용 한도가 될 수 있으며, 이는 a-의 두 오버레이 공정 오류를 줄일 수 있습니다. 기존 ESL 공정의 IGZO-ESL 및 ES-S/D 금속화 레이어(그림 2). a-IGZO, ES, S/D 레이어의 오버레이 수를 줄임으로써 기생 커패시턴스를 낮추는 TFT 소자의 크기를 줄였다. 결과 평면 구조는 BCE 구조와 유사합니다(그림 3a, b).

<그림>

(Color online) CL-ES 공정에서 TFT 채널과 S/D 전극 동시 형성 방법의 개략도. 아 게이트 전극을 형성하는 첫 번째 단계. ㄴ 에칭 스토퍼 층을 형성하는 두 번째 단계. ㄷ S/D 포토 패턴을 형성하는 세 번째 단계입니다. d S/D 전극과 액티브 패턴을 형성하는 네 번째 단계

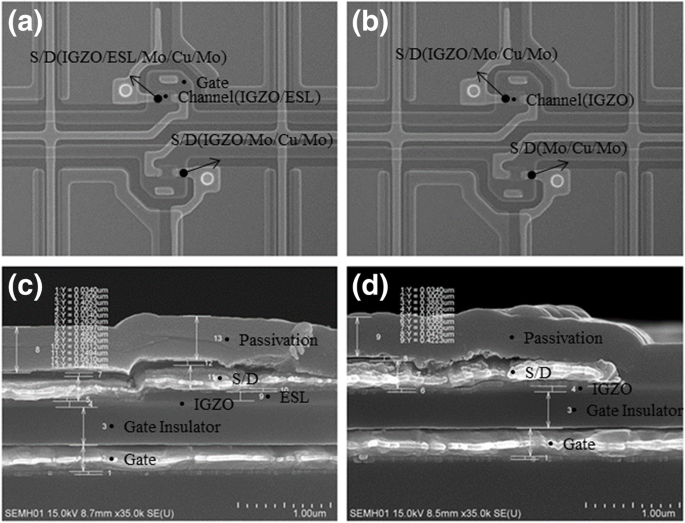

<사진>

(Color online) -IGZO TFT의 SEM 이미지(a , b 평면도; ㄷ , d 측면도) CL-ES 구조(a , ㄷ ) 및 BCE 구조(b , d )

그림 3은 CL-ES 구조(그림 3a, c)와 BCE 구조(그림 3b, d)를 가진 a-IGZO 기반 TFT의 SEM 이미지를 보여줍니다. 평면도에서는 CL-ES 구조와 BCE 구조의 차이점을 식별하기 어렵습니다(그림 3a, b). 측면에서 보면 CL-ES 구조에서 a-IGZO 나노층과 S/D 전극층 사이에 ES 나노층이 있음을 알 수 있다(그림 3c). 한편, BCE 구조에서 a-IGZO 나노층의 상부에는 보호층이 발견될 수 있다(그림 3d). 제시된 CL-ES 공정에서 두께가 30nm인 a-IGZO 나노층이 증착됩니다. 또한, 습식 에칭 중 손상은 무시할 수 있습니다. BCE 공정의 경우 a-IGZO 층은 식각 손실에 대한 보상이 필요하기 때문에 70nm a-IGZO 나노 층이 증착됩니다. CL-ES와 BCE 구조에서 a-IGZO 나노층의 두께 차이는 SEM 이미지에서 관찰할 수 있습니다(그림 3c, d).

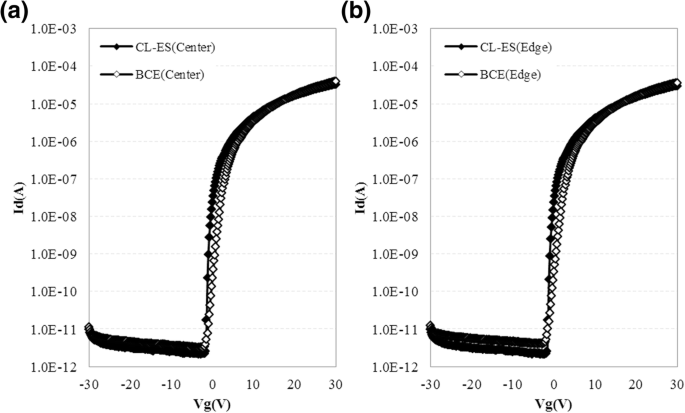

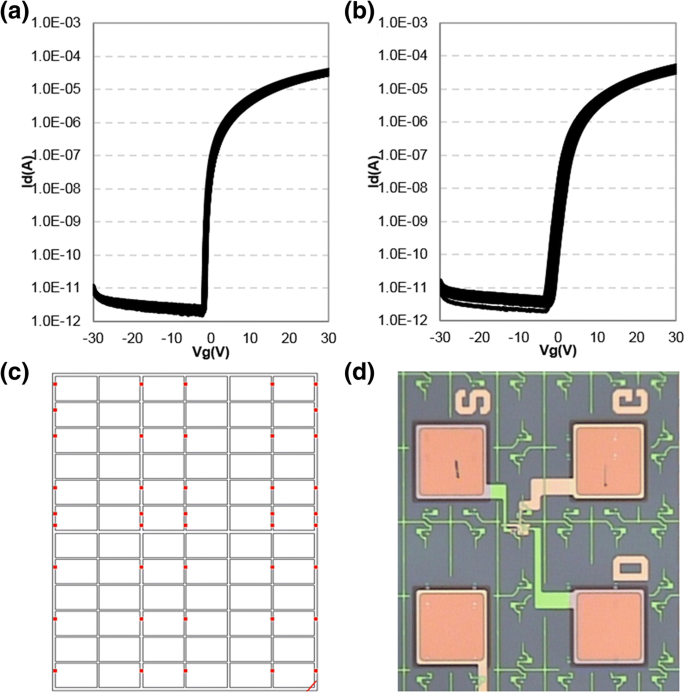

CL-ES 구조와 BCE 구조의 a-IGZO 기반 TFT의 I-V 특성을 비교합니다(그림 4). 포화 전자 이동도, 문턱 전압, SS(subthreshold voltage swing) 값 및 기타 특성 값은 표 1에 요약되어 있습니다. 표 1에 요약된 값은 8.5세대 유리 기판의 중심과 가장자리에서 파생된 평균 값입니다. . CL-ES 구조의 a-IGZO 기반 TFT는 V 구현 번째 − 0.8V, SS 값 0.18V/dec, 포화 전자 이동도 8.05cm 2 /V s. BCE 구조의 a-IGZO 기반 TFT에서 해당 결과는 V 번째 + 0.5V, SS 값 0.77V/dec, 포화 전자 이동도 6.03cm 2 /V s. BCE 구조와 비교하여 CL-ES 구조는 향상된 장치 성능을 보여줍니다. 그러나 CL-ES 구조의 a-IGZO 기반 TFT 소자의 온-전류 특성은 BCE 구조의 소자보다 낮습니다. 이는 CL-ES 및 BCE 구조에서 TFT 채널 구조가 다르기 때문입니다. 일반적으로 BCE 구조의 TFT 채널 길이는 S/D 금속 전극 사이의 거리이며, 본 연구에서 측정된 채널 길이는 5um이다[21]. CL-ES 구조에서 전극은 ESL 나노마스크 측면에서 늘어나는 a-IGZO 나노필름과 접촉한다. 따라서 채널 길이는 etch-stopper 측면에 정의된 a-IGZO 사이의 거리로 결정되지만 전극 사이의 거리로는 결정되지 않습니다. 현재 CL-ES-구조 장치의 채널 길이는 10um으로 측정됩니다.

<그림>

(Color online) 중앙에 CL-ES 및 BCE 구조가 있는 a-IGZO TFT의 I-V 특성 비교(a ) 및 가장자리(b ) 8.5세대 유리 기판

I의 측정값은 표 1과 같이 켜기 /나 꺼짐 비율(~ 10 6 , 표 1 참조)는 일반적인 값(> 10 7 )보다 약 10배 작습니다. ) a-IGZO 기반 TFT. 여기에 사용된 측정장비는 8.5세대 양산을 위한 장비이기 때문이다. 산업용 장비의 크기가 크기 때문에 이러한 측정에는 긴 케이블이 필요합니다. 긴 케이블은 측정 노이즈를 증가시켰습니다. 다음의 신뢰성 테스트에서는 보다 작은 규모의 측정 장비를 사용하고 개별 TFT 소자를 측정용 표본으로 사용합니다. 이러한 방식으로 측정된 I 켜기 /나 꺼짐 비율은 모두 상위 10 7 입니다. (아래 참조).

CL-ES 공정은 a-IGZO 채널 레이어가 식각액, 포토레지스트 또는 스트리퍼에 노출되는 것을 방지하도록 신중하게 설계되었습니다. CL-ES 공정, gate insulator, a-IGZO nano-layer, ES nano-layer를 생산하는 과정에서 각 층간 계면은 세정을 위해 DI water에만 접촉됩니다. 따라서 절연체층과 a-IGZO 나노층의 화학적 오염은 무시할 수 있다[25, 26]. 그러나 BCE 공정은 채널 층을 화학 물질에 노출시킬 뿐만 아니라 a-IGZO 채널이 Cu 금속에 직접 노출되기 때문에 Cu 이온 확산 오염을 수반합니다. 이것은 CL-ES 구조의 장치에서도 피할 수 있습니다. a-IGZO 나노 필름의 채널 영역은 ESL 나노 마스크로 잘 보호됩니다. CL-ES 공정에서 낮은 화학적 오염은 a-IGZO 나노층과 절연층 사이의 계면에서 낮은 캐리어 트랩 밀도로 이어져 우수한 SS 값을 초래할 수 있습니다. CL-ES 공정을 통한 a-IGZO 기반 TFT 소자의 낮은 화학적 오염은 또한 산업 생산에서 매우 중요한 a-IGZO TFT의 균일성과 재현성을 향상시키는 데 도움이 됩니다[27, 28].

그림 5는 8.5세대 기판의 42개 측정 지점에서 파생된 CL-ES 구조 및 BCE 구조를 가진 TFT의 측정된 I-V 특성을 보여줍니다. CL-ES 구조의 a-IGZO 기반 TFT는 V 번째 범위는 0.72V인 반면 BCE 구조의 기기는 2.14V입니다(표 1). 즉, CL-ES 구조에 의해 장치 성능의 균일성이 크게 향상됩니다.

<그림>

(온라인 색상) a CL-ES 구조. ㄴ BCE 구조의 TFT I-V 전달 특성. ㄷ 42개의 측정 포인트. d TFT님의 사진. 모두 8.5세대 기판에서 측정됨

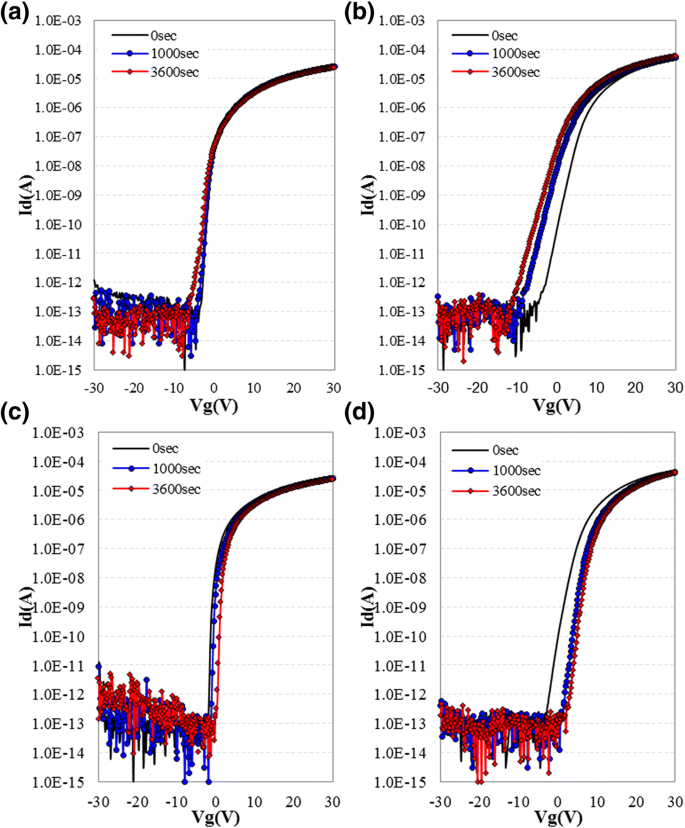

그림 6a, b는 NBTIS 테스트에서 얻은 CL-ES 구조화 장치와 BCE 구조화 장치의 I-V 특성 이동을 각각 보여줍니다. NBTIS 테스트 결과는 표 2에 요약되어 있습니다. 표 2에 설명된 스트레스 조건에서 V 번째 CL-ES 구조화 소자와 BCE 구조화 소자의 시프트는 각각 − 0.51 및 − 3.88V입니다. 또한, CL-ES 구조의 소자의 on-current shift, off-current shift, SS 값 변동은 모두 BCE 구조의 소자보다 낮습니다(표 2). CL-ES 구조의 a-IGZO 기반 소자는 a-IGZO의 오염을 효과적으로 방지하고 a-IGZO TFT 채널의 캐리어 트랩 밀도를 낮출 수 있기 때문이다. 특히, 처음 1000초의 응력 결과를 보면 CL-ES 구조의 소자에서 SS 값의 변화가 관찰되지 않습니다. 이 현상은 CL-ES TFT 백채널을 구성하는 a-IGZO 나노필름 표면에 캐리어 트랩을 형성할 수 있는 결함 부위가, 전기 및 조명 스트레스에 의해 추가로 생성되지 않습니다. 이러한 결과는 CL-ES 구조의 장치가 BCE 구조의 장치보다 훨씬 더 안정적임을 완전히 증명합니다. 그림 6c, d는 PBTS 테스트에서 얻은 CL-ES 및 BCE 구조 TFT의 I-V 곡선 이동을 보여줍니다. 자세한 PBTS 테스트 결과는 표 3에 요약되어 있습니다. CL-ES 구조의 TFT와 BCE 구조의 TFT는 모두 PBTS 평가 동안 이온 전류가 감소했습니다. 이것은 V의 이동으로 인해 발생합니다. 번째 긍정적인 방향으로. PBTS 평가 중 상대적으로 작은 V를 갖는 CL-ES 구조 TFT의 잔류 이온 전류 비율[(마지막 이온/초기 이온) × 100] 번째 양의 이동(+ 1.94 V)은 88.2% 수준입니다. BCE 구조의 TFT의 잔류 이온 전류 비율이 41.3%인 것과 비교할 때 CL-ES 구조의 TFT가 훨씬 우수합니다. 이는 GOA(Gate Drive On Array) 회로 설계 시 중요한 용량 차이를 보여줍니다. NBTIS와 달리 CL-ES 구조의 TFT의 SS 값은 BCE 구조의 TFT와 같이 큰 변화가 없거나((∆SS 0.06V/dec), 오히려 감소(∆SS − 0.86)합니다. 이는 아마도 캐리어는 양의 게이트 바이어스에 의해 게이트 절연체와 a-IGZO 나노막 사이의 내부 공간 및 계면에 축적되어 초기에 캐리어 트랩 사이트를 채워 캐리어 트랩 현상을 감소시키고, 문턱 전압 시프트 현상은 게이트 절연체와 a-IGZO 나노 필름 사이의 경계면 근처에 캐리어 전하 트랩 CL-ES 구조의 TFT의 작은 문턱 전압 이동은 a-IGZO의 계면과 내부 공간이 현저하게 깨끗함을 나타냅니다. 결론적으로 PBTS 테스트도 CL-ES 구조와 프로세스가 더 나은 장치 신뢰성으로 이어짐을 시사합니다.

<그림>

(온라인 컬러) CL-ES의 I-V 전달 특성 드리프트(a , ㄷ ) 및 BCE(b , d ) NBITS에서 얻은 TFT(a , b ) 및 PBTS 테스트(c , d )

결론적으로, 새로 개발된 CL-ES 공정은 고급 디스플레이를 위한 5개의 마스크가 있는 a-IGZO 기반 TFT 백플레인을 제작하기 위해 성공적으로 개발되었습니다. CL-ES 공정은 BCE 공정과 동일한 수의 마스크와 유사한 소자 면적을 유지하면서 Etch-stopper-layer 구조의 장점을 가지고 있어 기존의 etch-stopper TFT 소자의 마스크 수 및 점유 면적 증가 문제를 극복 . 새로 형성된 ESL 나노마스크와 a-IGZO 나노층과 S/D 전극 나노층을 동시에 식각함으로써 대면적 디스플레이용 소자의 높은 균일성과 안정성을 가능하게 한다. 전기적 성능과 관련하여 CL-ES 구조의 a-IGZO 기반 TFT의 소자 성능의 재현성과 신뢰성은 BCE 구조의 소자보다 훨씬 우수합니다. a-IGZO 기반 TFT 장치는 V 번째 42개 측정 지점에 대한 분포 0.72V의 8.5세대 유리 기판의 TFT, 8.05cm 2 의 포화 전자 이동도 /V s, SS 값 0.18 V/dec. NBTIS와 PBTS의 신뢰도 평가 결과에 따르면 V 번째 CL-ES a-IGZO 기반 TFT의 스트레스 전후 변화는 각각 3600초의 스트레스 후 - 0.51 및 1.94V입니다. SS 값 편차는 0.33 및 0.06V/dec입니다. 따라서 제시된 CL-ES 기술은 기술적, 경제적 장애물을 극복함으로써 차세대 고해상도 및 대형 패널 디스플레이 제품의 초석이 될 것입니다.

무정형 인듐-갈륨-아연-산화물

액티브 매트릭스 액정 디스플레이

백 채널 에칭

에칭 스토퍼 층

어레이의 게이트 드라이브

네거티브 바이어스 온도 조명 스트레스

포지티브 바이어스 온도 스트레스

질화규소

산화규소

하위 임계값 스윙

박막 트랜지스터

트위스트 네마틱 액정 디스플레이

나노물질

이 작은 데모 프로젝트는 REST API 및 Modbus TCP를 통해 오픈 소스 홈 자동화 소프트웨어 Home Assistant에서 PLCnext 컨트롤러를 스마트 홈 장치로 쉽게 사용하는 방법을 보여줍니다. PLCnext 컨트롤러를 사용하면 자동화에서 Axioline 구성 요소를 사용하여 Raspberry Pi의 GPIO 핀, Pt100과 같은 온도 센서 및 DALI와 같은 버스 시스템보다 더 강력한 출력을 쉽게 추가할 수 있습니다. 작동하는 홈 어시스턴트 설치와 작지만 실행 가능한 PLCnext 프로젝트가 포함된 PLCnext

디스플레이 화면은 오늘날 어디에나 있습니다. 20년 전 TV나 컴퓨터 모니터를 아직도 기억하십니까? 그것들은 사각형이고 거대하고 무거웠습니다. 이제 눈앞의 납작하고 얇고 가벼운 화면을 보겠습니다. 왜 이렇게 큰 차이가 나는지 궁금하지 않으셨나요? 사실 20년 전의 모니터는 CRT였습니다. (Cathode Ray Tube) 디스플레이는 내부 구성 요소를 실행하기 위해 큰 공간이 필요합니다. 이제 여기에 있는 화면은 LCD 입니다. (액정 디스플레이) 화면. LCD란 무엇입니까? 위에서 언급했듯이 LCD는 Liquid Crystal