verilog

module 특정 기능을 구현하는 Verilog 코드 블록입니다. 모듈은 다른 모듈에 내장될 수 있으며 상위 모듈은 입력 및 출력 포트를 사용하여 하위 모듈과 통신할 수 있습니다.

모듈 module 안에 넣어야 합니다. 및 endmodule 키워드. 모듈 이름은 module 바로 뒤에 지정해야 합니다. 키워드 및 선택적 포트 목록도 선언할 수 있습니다. 포트 선언 목록에 선언된 포트는 모듈 본문 내에서 다시 선언할 수 없습니다.

module <name> ([port_list]);

// Contents of the module

endmodule

// A module can have an empty portlist

module name;

// Contents of the module

endmodule

모든 변수 선언, 데이터 흐름 문, 함수 또는 작업 및 하위 모듈 인스턴스(있는 경우)는 module 내에 정의되어야 합니다. 및 endmodule 키워드. 동일한 파일에 이름이 다른 여러 모듈이 있을 수 있으며 임의의 순서로 정의할 수 있습니다.

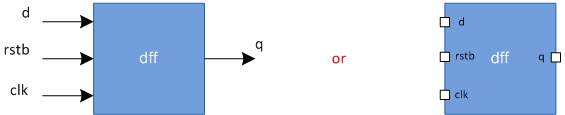

모듈 dff는 3개의 입력 포트 d, clk, rstn 및 1개의 출력 포트 q가 있는 D 플립플롭을 나타냅니다. 모듈의 내용은 D 플립플롭이 다양한 입력 조합에 대해 어떻게 작동해야 하는지 설명합니다. 여기에서 입력 d는 활성 로우 리셋이기 때문에 rstn이 하이인 경우 클록의 양의 에지에서 항상 출력 q에 할당됩니다.

// Module called "dff" has 3 inputs and 1 output port

module dff ( input d,

input clk,

input rstn,

output reg q);

// Contents of the module

always @ (posedge clk) begin

if (!rstn)

q <= 0;

else

q <= d;

end

endmodule

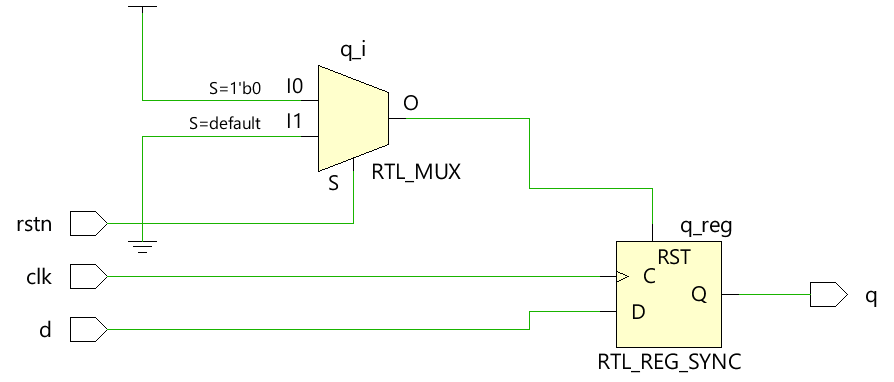

이 모듈은 합성 중에 다음 디지털 회로로 변환됩니다.

<노스크립트>

모듈 외부에는 코드를 작성할 수 없습니다!

모듈은 특정 동작 특성을 구현하고 합성 중에 디지털 회로로 변환되는 설계 단위를 나타냅니다. 입력 조합은 모듈에 제공될 수 있으며 해당 출력을 제공합니다. 이것은 동일한 모듈을 허용합니다. 더 복잡한 하드웨어를 구현하는 더 큰 모듈을 형성하는 데 재사용됩니다.

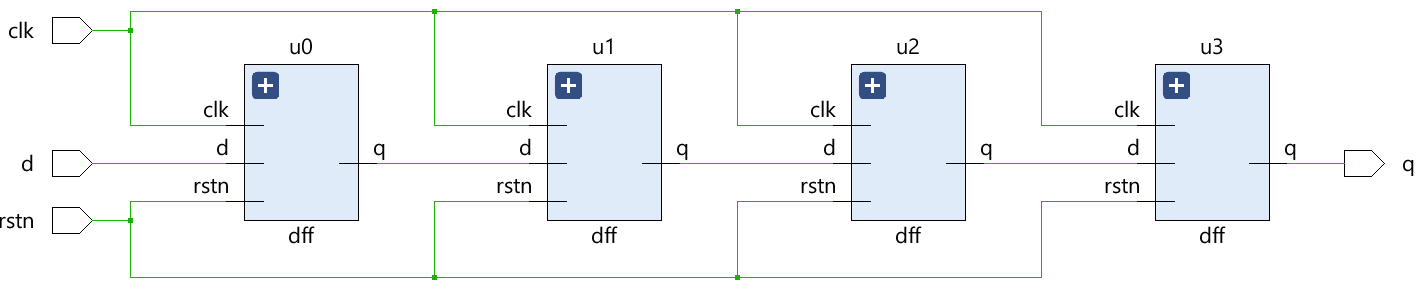

예를 들어, 위에 표시된 DFF를 연결하여 시프트 레지스터를 형성할 수 있습니다.

module shift_reg ( input d,

input clk,

input rstn,

output q);

wire [2:0] q_net;

dff u0 (.d(d), .clk(clk), .rstn(rstn), .q(q_net[0]));

dff u1 (.d(q_net[0]), .clk(clk), .rstn(rstn), .q(q_net[1]));

dff u2 (.d(q_net[1]), .clk(clk), .rstn(rstn), .q(q_net[2]));

dff u3 (.d(q_net[2]), .clk(clk), .rstn(rstn), .q(q));

endmodule

dff 인스턴스는 Verilog RTL 모듈에 설명된 대로 와이어로 함께 연결됩니다.

<노스크립트>

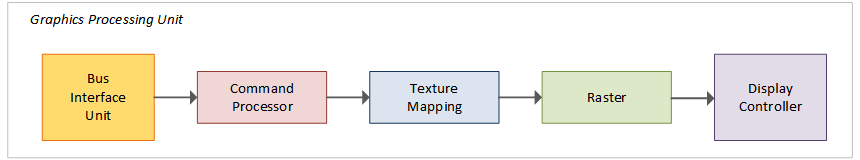

더 큰 디자인 블록을 형성하기 위해 더 작은 블록에서 구축하는 대신 그 반대도 수행할 수 있습니다. 각각이 특정 기능을 구현하는 모듈로 표시될 수 있도록 간단한 GPU 엔진을 더 작은 구성 요소로 분해하는 것을 고려하십시오. 아래 표시된 GPU 엔진은 각각 특정 기능을 수행하는 5개의 서로 다른 하위 블록으로 나눌 수 있습니다. 버스 인터페이스 장치는 외부에서 설계로 데이터를 가져와서 다른 장치에서 처리하여 명령을 추출합니다. 라인 아래의 다른 유닛은 이전 유닛에서 제공한 데이터를 처리합니다.

<노스크립트>

각 하위 블록은 module로 나타낼 수 있습니다. 다른 모듈과의 통신을 위한 특정 입력 및 출력 신호 세트와 각 하위 블록은 필요에 따라 더 미세한 블록으로 더 나눌 수 있습니다.

최상위 모듈은 포함 다른 모든 모듈. 최상위 모듈은 다른 모듈 내에서 인스턴스화되지 않습니다.

예를 들어, 설계 모듈은 일반적으로 최상위 테스트벤치 모듈 내에서 인스턴스화되므로 입력 자극을 제공하여 시뮬레이션을 실행할 수 있습니다. 그러나 테스트벤치는 다른 모든 것을 캡슐화하는 블록이므로 최상위 모듈이므로 다른 모듈 내에서 인스턴스화되지 않습니다. .

아래에 표시된 디자인 코드에는 design이라는 최상위 모듈이 있습니다. 디자인을 완성하는 데 필요한 다른 모든 하위 모듈이 포함되어 있기 때문입니다. 하위 모듈은 mod1 내부의 mod3 및 mod2 내부의 mod4와 같이 더 많은 중첩된 하위 모듈을 가질 수 있습니다. 어쨌든 mod1과 mod2가 인스턴스화될 때 이 모든 것이 최상위 모듈에 포함됩니다. 따라서 디자인은 완전하며 디자인의 최상위 모듈입니다.

//---------------------------------

// Design code

//---------------------------------

module mod3 ( [port_list] );

reg c;

// Design code

endmodule

module mod4 ( [port_list] );

wire a;

// Design code

endmodule

module mod1 ( [port_list] ); // This module called "mod1" contains two instances

wire y;

mod3 mod_inst1 ( ... ); // First instance is of module called "mod3" with name "mod_inst1"

mod3 mod_inst2 ( ... ); // Second instance is also of module "mod3" with name "mod_inst2"

endmodule

module mod2 ( [port_list] ); // This module called "mod2" contains two instances

mod4 mod_inst1 ( ... ); // First instance is of module called "mod4" with name "mod_inst1"

mod4 mod_inst2 ( ... ); // Second instance is also of module "mod4" with name "mod_inst2"

endmodule

// Top-level module

module design ( [port_list]); // From design perspective, this is the top-level module

wire _net;

mod1 mod_inst1 ( ... ); // since it contains all other modules and sub-modules

mod2 mod_inst2 ( ... );

endmodule

테스트벤치 모듈은 설계의 기능을 확인하기 위한 자극을 포함하고 있으며 주로 시뮬레이션 도구를 사용한 기능 검증에 사용됩니다. 따라서 디자인은 인스턴스화되고 테스트벤치 모듈 내에서 d0이라고 불립니다. 시뮬레이터 관점에서 테스트벤치는 최상위 모듈입니다.

//-----------------------------------------------------------

// Testbench code

// From simulation perspective, this is the top-level module

// because 'design' is instantiated within this module

//-----------------------------------------------------------

module testbench;

design d0 ( [port_list_connections] );

// Rest of the testbench code

endmodule

모듈이 서로 내부에서 인스턴스화될 수 있을 때 계층적 구조가 형성되므로 최상위 모듈을 루트라고 합니다. . 주어진 모듈 내의 각 하위 모듈 인스턴스화는 서로 다른 식별자 이름을 가져야 하므로 신호에 액세스하는 데 모호함이 없습니다. 계층적 이름은 점 .로 구분된 이러한 식별자 목록으로 구성됩니다. 계층 구조의 각 수준에 대해 특정 신호에 대한 계층적 경로를 사용하여 모든 모듈 내에서 모든 신호에 액세스할 수 있습니다.

// Take the example shown above in top level modules

design.mod_inst1 // Access to module instance mod_inst1

design.mod_inst1.y // Access signal "y" inside mod_inst1

design.mod_inst2.mod_inst2.a // Access signal "a" within mod4 module

testbench.d0._net; // Top level signal _net within design module accessed from testbench

verilog

디자인 module ring_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= out[0]; for (int i = 0; i < WIDTH-1; i=i+1) begi

디자인 module johnson_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= ~out[0]; for (int i = 0; i < WIDTH-1; i=i+1) b