verilog

산업 제조

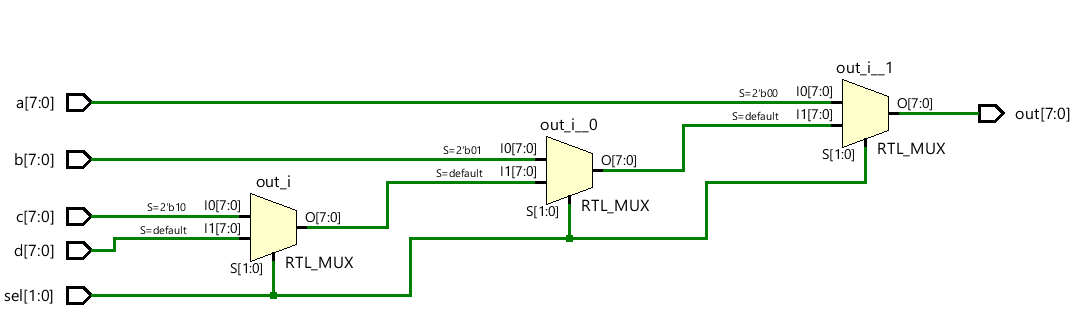

module pr_en ( input [7:0] a,

input [7:0] b,

input [7:0] c,

input [7:0] d,

input [1:0] sel,

output reg [7:0] out);

always @ (a or b or c or d or sel) begin

if (sel == 2'b00)

out <= a;

else if (sel == 2'b01)

out <= b;

else if (sel == 2'b10)

out <= c;

else

out <= d;

end

endmodule

module tb_4to1_mux;

reg [7:0] a;

reg [7:0] b;

reg [7:0] c;

reg [7:0] d;

wire [7:0] out;

reg [1:0] sel;

integer i;

pr_en pr_en0 ( .a (a),

.b (b),

.c (c),

.d (d),

.sel (sel),

.out (out));

initial begin

sel <= 0;

a <= $random;

b <= $random;

c <= $random;

d <= $random;

for (i = 1; i < 4; i=i+1) begin

#5 sel <= i;

end

#5 $finish;

end

endmodule

verilog

Verilog는 하드웨어 설명 언어이며 설계자가 RTL 설계를 시뮬레이션하여 논리 게이트로 변환할 필요가 없습니다. 시뮬레이션이 필요한 이유는 무엇입니까? 시뮬레이션은 RTL 코드가 의도한 대로 동작하는지 확인하기 위해 다른 시간에 다른 입력 자극을 설계에 적용하는 기술입니다. 기본적으로 시뮬레이션은 설계의 견고성을 검증하기 위해 잘 따라야 하는 기술입니다. 또한 가공된 칩이 실제 세계에서 사용되는 방식과 다양한 입력에 반응하는 방식과 유사합니다. 예를 들어, 위의 디자인은 출력 pe 보여진 바와 같이. 시뮬레이션을 통해

디자인 module pr_en ( input [7:0] a, input [7:0] b, input [7:0] c, input [7:0] d, input [1:0] sel, output reg [7:0] out); always @ (a or b or c or d or sel) begin if (sel == 2b00) out <= a; else if