7nm 이상을 위한 재료 혁신의 핵심

NY의 Albany에 있는 반도체 연구 팀은 CMOS 기술을 10nm, 7nm 및 그 이상으로 미래 노드로 계속 확장하고 있습니다. 전류 흐름과 연결 방법을 결정하는 트랜지스터 채널 저항은 칩의 전반적인 성능. 따라서 주어진 미래 반도체 기술의 성능 경쟁력을 확보하기 위해서는 트랜지스터 채널 저항을 줄이는 채널 재료 혁신이 중요한 연구 분야입니다. 이것이 우리가 작년 7nm 칩 발표에서 설명한 전력 성능 이점을 달성하는 데 필요한 요소인 SiGe(실리콘 게르마늄)를 탐색하는 이유입니다.

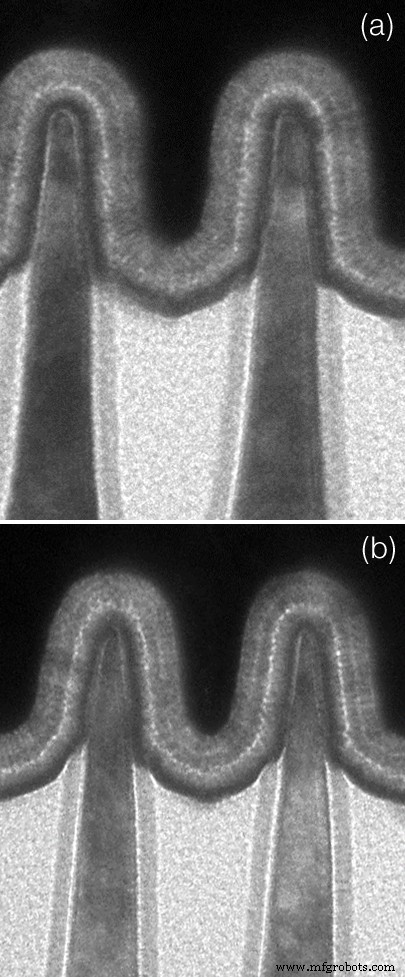

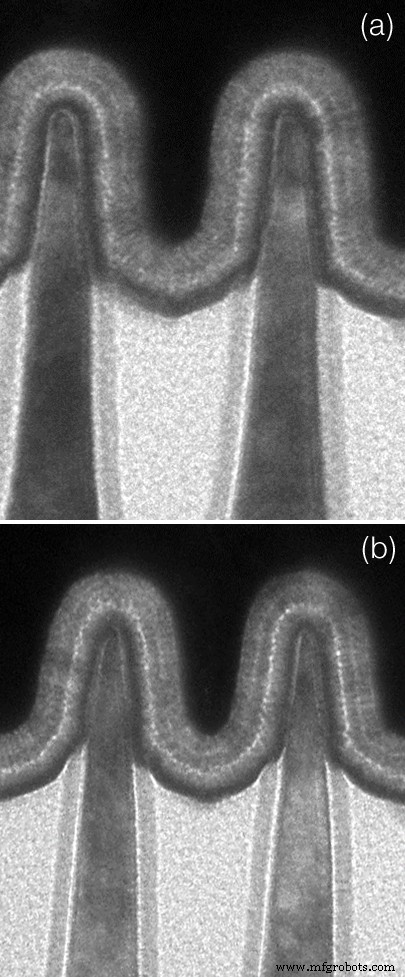

대칭 Si NY, Albany에 있는 SUNY Polytechnic의 NanoTech Complex에서 IBM Research에서 만든 10nm의 FinFET(a) 및 SiGe FinFET(b) 프로파일. 이는 SiGe Fin이 Si Fin보다 우수한 전기적 특성을 제공할 수 있음을 보여줍니다.

오늘날의 14nm 노드 FinFET* 기반 칩은 실리콘 전용 채널을 사용합니다(실리콘은 이 규모 이상에서는 안정적이지 않음). 대안으로 SiGe 기반 FinFET 기술은 10nm 기술 기본 규칙(산업 표준)으로 성능 향상을 보여 실행 가능한 CMOS 기술 옵션에 대한 우아한 솔루션을 제공합니다. 이러한 우아한 SiGe FinFET 솔루션 중 하나는 동일한 칩에서 저전력 및 고성능 장치를 모두 수용할 수 있다는 것입니다. 즉, 한 유형의 장치에서 다른 유형에 비해 성능이나 가변성을 잃지 않으면서 말입니다.

SiGe FinFET 기술은 또한 Si FinFET에 비해 우수한 전기적 신뢰성을 제공합니다. 이는 칩 수명 동안 Si FinFET보다 향상된 칩 수준 성능 안정성으로 이어집니다. 이는 동일한 프로세스 통합 흐름이 모바일 디자인뿐만 아니라 슈퍼컴퓨터 디자인에도 적합하다는 것을 의미합니다.

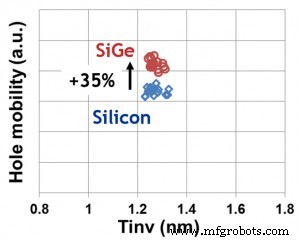

SiGe는 전류가 트랜지스터의 채널을 통과하는 방식을 변경하여 칩 스케일링의 한계를 뛰어 넘습니다. 더 작은 실리콘 원자로 구성된 결정에 더 큰 게르마늄 원자를 추가함으로써 결정이 격자 불일치를 발생시켜 트랜지스터 채널에 변형을 생성한다는 것이 밝혀졌습니다. 이 변형으로 인해 더 낮은 전압에서 채널을 통해 더 많은 전류를 이동할 수 있습니다. 따라서 SiGe를 채널 자료로 사용하여 성능과 성능 사이의 균형을 유지하면서 더 작은 차원으로 로드맵을 작성할 수 있습니다.

앞으로의 노드를 위한 SiGe:10nm 및 7nm 칩 생산 문제 해결

결함 제어와 함께 전체 통합 흐름 전반에 걸친 변형 유지는 10nm 노드 이하에서 SiGe FinFET을 생산하기 위한 두 가지 주요 기술 과제입니다. 트랜지스터 채널은 도펀트를 활성화하고 트랜지스터 무결성을 안정화하는 열 어닐링 프로세스 동안 변형을 잃을 수 있습니다. 또는 Fin의 상단에서 Fin의 하단까지 균일한 접합을 형성하는 소스/드레인 리세스 프로세스 동안; 또는 짧은 길이의 핀이 필요한 특정 디자인의 핀 패턴화도 가능합니다.

CMOS 기술의 대량 생산에서도 결함 제어가 중요합니다. SiGe 채널과 실리콘 웨이퍼 기판 사이의 격자 불일치로 인해 전체 웨이퍼에서 필요한 제조 가능성 결함 수준을 유지하는 것이 어렵습니다. 그러나 고급 에피택시(결정) 성장 관리, 혁신적인 Fin 모듈 프로세스 통합 및 소스/드레인 엔지니어링을 통해 전체 통합 흐름에서 채널의 변형을 보장하는 동시에 10nm 및 7nm 테스트에서 낮은 결함을 유지하는 솔루션을 개발했습니다. 노드.

10nm 기술 기본 규칙에 대한 이 포괄적인 SiGe FinFET 기술 타당성 연구를 통해 우리는 현재 SiGe FinFET 기술을 대량 생산하기 위해 칩 설계자 및 칩 제조업체와 협력하고 있습니다. 저는 SiGe FinFET 기술이 슈퍼컴퓨터에서 모바일 장치에 이르는 컴퓨팅 사용을 위한 차세대 CMOS 기술 노드에서 실리콘 FinFET을 대체할 것으로 기대합니다. 또한 클라우드 및 인지 컴퓨팅의 응용 프로그램과 같이 저전력 공급 및 저전력 소비가 매우 바람직한 "무어 이상의" 응용 프로그램 I 클라우드 및 인지 컴퓨팅에도 사용할 수 있습니다.

추가 읽기

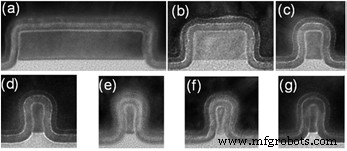

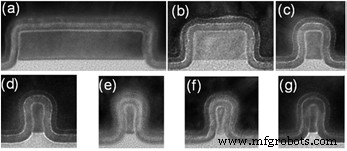

단면 SiGe Fin의 더 높은 Ge 함량을 위해 87nm(a) ~ 3nm(g) 범위의 Fin 너비에 대한 Fin 및 게이트 스택

올해 IEEE VLSI(Very-large-scale integration) 기술 심포지엄에서 우리 팀은 10nm 기본 규칙과 함께 SiGe를 사용하는 데 중점을 두고 스케일링 문제를 해결하기 위한 경로로 여러 새로운 장치, 재료 및 통합 혁신을 발표했습니다. 작년에 제작한 7nm 테스트 노드의 성능 문제

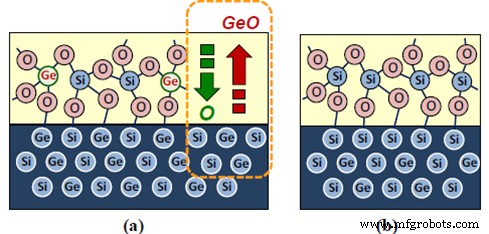

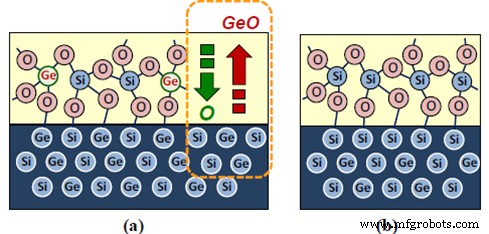

우리의 프레젠테이션은 결함 제어를 위한 중요한 기술적 기능과 근본적인 프로세스 혁신을 다루었습니다. SiGe FIN에 적합한 게이트 스택 및 계면층의 혁신; VLSI 컨퍼런스의 연구 논문 T2.2에 보고된 SiGe FinFET 플랫폼의 고급 접촉 기술. T4.3 연구 논문은 SiGe 채널을 위한 견고한 계면층을 구축하기 위한 독창적인 선택적 산화 게르마늄 소거 공정을 제시했습니다.

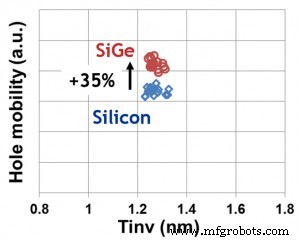

명확한 이동성 Si Fin에 비해 SiGe Fin의 이점으로 인해 칩 수준의 성능이 향상됩니다.

미래의 고성능 노드를 위한 SiGe FinFET 기술의 확장성에 중점을 둔 Dr. Pouya Hashemi가 이끄는 우리의 연구도 VLSI에서 발표되었습니다. T9.3 연구 논문에서 우리는 더 높은 Ge 함량과 더 작은 Fin 너비 및 추가 게이트 스택 확장으로 더 높은 성능을 달성하는 가능성을 보고했습니다. VLSI 심포지엄 참가자는 VLSI 웹사이트에서 이러한 기술 문서를 찾을 수 있습니다. 자세한 내용은 Linkedin Group에 가입할 수도 있습니다.

T2.2:10nm 이상을 위한 이동성 SiGe 채널을 특징으로 하는 FINFET 기술

T4.3:선택적 Geox -Si1-x의 계면층에서 청소 Gex 고이동성 Si/Si1-x용 채널 Gex CMOS 애플리케이션

T9.3:공격적인 EOT ~7Å 및 축소된 치수에서 4nm 이하의 핀 너비로 축소된 높은 홀 이동성과 우수한 SS 및 신뢰성을 갖춘 High-K/Metal-Gate High-Ge-content 변형 SiGe FinFET 교체

T7.2:첨단 기술을 위한 Ti 및 NiPt/Ti 라이너 실리사이드 접점

개략도 본 발명의 선택적 GeOx 소거 공정(a) 및 SiGe 채널이 있는 GeOx가 없는 계면층(b)

*-FinFET는 핀처럼 보이도록 트랜지스터 채널을 높이는 트랜지스터 아키텍처를 나타냅니다.

Dechao Guo는 IBM Research의 연구원이자 최고 발명가이자 고급 장치 설계 및 통합 관리자입니다.