나노물질

현재 연구 영역에서 PDMS(폴리디메틸실록산) 기반 나노유체 소자는 의료, 화학 및 생물학적 응용 분야에서 널리 사용됩니다. 본 논문에서는 PDMS 칩에 나노채널(크기 조절 가능)을 제작하기 위해 AFM 시스템과 압전 액추에이터로 구성된 새로운 나노밀링 기술을 제안했으며, 압전 액추에이터에 입력되는 구동 전압과 주파수에 의해 나노채널 크기를 제어했다. . 또한, UV 리소그래피 및 AFM 팁 기반 나노 밀링으로 마이크로 채널 및 나노 채널 몰드를 각각 제작하고 마지막으로 트랜스퍼 공정을 통해 마이크로/나노 채널이 있는 PDMS 슬래브를 얻었다. PDMS 중량비가 나노채널 크기에 미치는 영향도 조사했습니다. 마이크로채널과 나노채널 슬래브의 접합 공정은 광학 단안 현미경과 정밀 스테이지로 구성된 수제 정렬 시스템에서 수행되었습니다. 또한, 나노채널 크기가 KCl 용액(1 mM 농도)의 전기적 특성에 미치는 영향을 분석하였다. 따라서 제안된 방법으로 100nm 이하 깊이의 다중 나노채널을 갖는 PDMS 나노유체 소자를 효율적이고 경제적으로 제작할 수 있다고 결론지을 수 있습니다.

<섹션 데이터-제목="배경">미세/나노유체 시스템은 화학, 의료 및 생물학 분야에서 상당한 잠재력을 가지고 있기 때문에 DNA 분석[1,2,3,4], 세포 분리[5], 단백질 연구[6,7,8], 식품 안전 [9], 환경 모니터링 [10]. 나노 제조 기술의 급속한 발전으로 100 nm 미만의 1차원 크기를 갖는 나노유체 소자에 대한 수요가 지속적으로 증가하고 있다[11]. 나노유체 칩은 바이러스 검출[12], 나노입자 조작[13], 이온 확산 연구[14]에도 효과적으로 사용될 수 있습니다. 그러나 나노유체 칩의 검출 효율과 감도는 나노채널의 특징 치수와 분포에 따라 달라집니다. 나노유체 기반 무표지 검출을 위해서는 나노채널의 특징 치수를 정확하게 제어하는 것이 필수적입니다. 제어 가능한 기능 치수와 분포를 가진 나노채널을 제조하는 방법은 나노유체 분야의 응용에 여전히 도전 과제입니다.

지금까지 나노유체 칩의 제조에 활용될 수 있는 몇 가지 방법이 있다. 반응성 이온 식각[15], 기존 포토리소그래피[16], 고에너지 빔 처리[17], 간섭 리소그래피[18], 나노임프린팅[19], 핫 엠보싱 기술[20, 21]이 제조에 가장 일반적으로 사용됩니다. 나노유체 소자; 그러나 이러한 모든 방법은 고유한 한계를 나타냅니다. 반응성 이온 에칭과 기존의 포토리소그래피는 마이크로/나노 유체 채널 제작을 위한 주류 방법입니다. 그러나 제작된 채널의 측면 치수는 입사광의 파장에 따라 달라지므로 생성된 채널의 너비는 종종 나노 스케일이 아닌 마이크로미터 스케일에서 발견됩니다[22]. 게다가, 마이크로/나노 구조를 제작할 때 특징이 다른 포토마스크를 교체하는 것은 불편하다. 집속 이온빔 리소그래피(FIB)와 전자빔 리소그래피(EBL)는 모두 고에너지 빔 처리 방법으로, 100 nm 미만의 나노채널을 갖는 고정밀 나노유체 칩을 쉽게 제작할 수 있습니다. 그러나 제조 시설에 대한 투자가 매우 높고 엄격한 환경 요구 사항이 필요합니다[23]. 간섭 리소그래피(IL)는 넓은 영역에 걸쳐 단순한 주기적 구조를 제작하는 데 적합합니다. 그러나 단일 나노채널을 가공하는 것은 적합하지 않습니다[24, 25]. 나노임프린팅의 처리 해상도는 템플릿 속성에 따라 달라지며, 이 접근 방식에서 중요한 문제는 고정밀 나노구조로 템플릿을 제작하는 방법입니다[26]. 또한 마이크로/나노 스케일 장치를 제작하기 위해 희생 몰딩 및 크릭 기반 방법이 채택되었습니다[27, 28]. 그러나 이러한 접근 방식에서는 나노채널 크기의 정확한 제어가 매우 어렵습니다. 따라서, 나노유체 소자의 제조를 위해서는 높은 가공 정밀도, 사용 용이성, 넓은 처리 범위 및 낮은 환경 요구사항의 특성을 가진 보다 실현 가능한 제조 방법이 요구됩니다.

최근에는 높은 가공 정밀도로 인해 나노 밀링, 정밀 연삭, 초정밀 선삭과 같은 초정밀 가공 방법이 미세/나노 구조 제조에 널리 사용됩니다[29,30,31,32]. 또한, 1986년 원자간력현미경(AFM)이 발명된 이후, AFM 팁 기반 나노가공은 나노구조를 제조하는 강력한 방법이다[33]. 기존의 팁 기반 나노스크래칭은 제한된 가공 폭 및 낮은 제조 효율성과 같은 몇 가지 제한 사항을 가지고 있습니다. 이 접근 방식으로 제작된 나노채널의 너비는 AFM 팁의 형상에 따라 달라지며, 이는 액세스할 수 없는 제어 가능한 너비의 나노채널을 의미합니다. 또한, 기존의 팁 기반 나노 스크래칭 공정의 제조 효율은 특히 가공 공정에서 피드를 사용하여 얻은 나노 구조의 깊이와 너비를 확대하는 경우 상대적으로 낮습니다. 제어 가능한 가공 크기 및 높은 제조 효율성과 같은 상당한 이점으로 인해 팁 기반 나노 밀링은 나노 채널을 제조하는 데 널리 채택됩니다. Gozenet al. [34, 35] 나노밀링 공정을 통해 폴리메틸 메타크릴레이트(PMMA)에 나노 구조를 제작했습니다. Zhang et al. [36,37,38]은 원자현미경을 사용하여 3차원 나노구조를 준비하고 다양한 가공 매개변수의 효과를 연구했습니다. Park et al. [39] nanomachining 프로세스의 메커니즘을 조사하고 절삭력의 강도가 크게 감소한다는 것을 발견했습니다. 그러나 제안된 시스템에서는 가공 설비가 상대적으로 복잡하고 재료 제거 공정이 자세히 조사되지 않은 것으로 나타났습니다. 구동 주파수 및 전압을 포함한 가공 매개변수와 얻어진 나노채널의 특징 치수 사이의 관계는 연구되지 않았다. 또한, 그들의 작업은 제작된 나노채널의 적용에 초점을 맞추지 않았습니다. 따라서 이 AFM 팁 기반 나노밀링 접근 방식의 적용 범위를 탐색하려면 더 많은 작업이 필요합니다. 폴리카보네이트(PC)는 우수한 가공성으로 인해 나노 가공에 일반적으로 사용됩니다[40]. 그럼에도 불구하고 나노유체 칩을 제조하는 데는 거의 선택되지 않습니다. 대조적으로, 폴리디메틸실록산(PDMS)은 미세 유체 및 나노 유체 칩을 처리하는 데 널리 사용됩니다. Mata et al. [41]은 인장 응력에 대한 PDMS 중량 비율의 영향을 연구했습니다. Park et al. [42]는 PDMS의 강성을 향상시키는 새로운 방법을 개발했습니다. 라벨이 없는 테스트 분야에서 나노유체 칩의 응용은 주로 나노채널의 전기 전도도에 의존하므로[43], 측정 결과는 종종 나노채널의 치수 크기에 영향을 받습니다[44].

따라서 본 연구에서는 기존의 팁 기반 스크래칭 공정의 단점을 극복하기 위해 나노 밀링 방식을 사용하여 나노 채널의 제조 공정을 수행합니다. 또한, 팁 마모를 완화하고 제조 비용을 줄이기 위해 PC 시트를 실험 샘플로 선택했습니다. 또한, 압전 액츄에이터에 입력되는 구동 전압과 주파수에 의해 PC 시트의 나노채널 크기를 제어하였다. PDMS 중량비가 나노채널 크기에 미치는 영향도 조사했습니다. 또한 다양한 크기가 나노채널의 전기전도도에 미치는 영향을 확인하기 위해 KCl 용액을 사용하여 전류 측정 테스트를 수행했습니다.

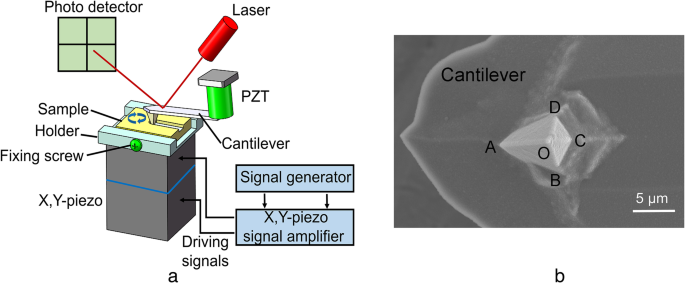

제안된 원자현미경 팁 기반 나노밀링 시스템은 상용 원자현미경(Dimension Icon, Bruker Company, Germany)과 압전 액추에이터(P-122.01, PI Company, Germany)로 구성되었습니다(그림 1a). x 및 y 방향 모두에서 압전 액추에이터의 이동 범위는 1 μm로 제한되었습니다. 또한, 압전 액츄에이터는 신호 증폭기(PZD350A; TREK, Inc., USA)의 증폭 하에 적절한 전압(상업 신호 발생 장치(AFG1022; Tektronix, Inc., USA)에서 생성됨)의 사인파 신호에 의해 구동되었습니다. PC 시트를 홈메이드 홀더(에폭시 수지제)에 고정 나사로 고정했습니다. 나노 가공 작업은 100 nm 두께의 직사각형 피라미드형 다이아몬드 코팅 팁(DT-NCLR, Nanosensors, Switzerland)을 사용하여 수행되었습니다. 팁의 캔틸레버(68 N/m의 정상 스프링 상수)는 실리콘으로 제작되었으며(그림 1b), 실리콘 팁(반경 10 nm)(TESPA, Bruker Company, Germany)을 사용하여 홈을 측정했습니다. 가공.

<그림>

아 나노 밀링 시스템의 개략도. ㄴ 다이아몬드 코팅된 AFM 팁의 SEM 현미경 사진

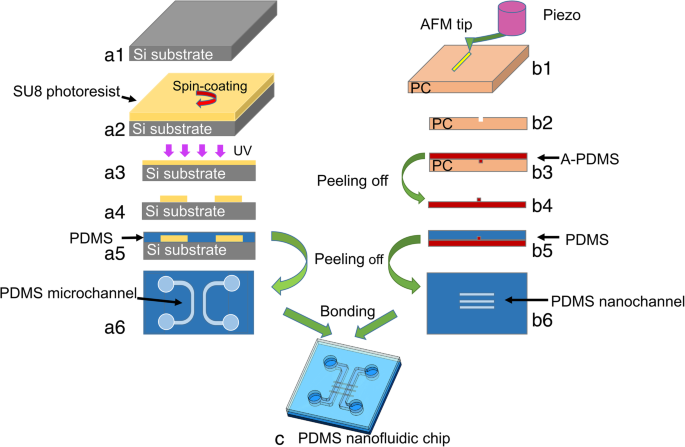

PDMS 칩의 나노채널 제조 경로는 그림 2에 나와 있습니다. AFM 시스템과 압전 액추에이터는 PC 시트에 나노채널 몰드(크기 조절 가능)를 제작하는 데 사용되었습니다. 15 mm × 12 mm × 1 mm 크기의 PC 시트(분자량 35,000)는 Goodfellow에서 구입했습니다. PC 시트의 표면 거칠기(Ra)의 평균 및 표준 편차는 각각 0.6 nm 및 0.2 nm로 측정되었습니다(이 값은 AFM 탭핑 모드에서 샘플의 50 μm × 50 μm 영역을 스캔하여 얻은 값입니다). 원형 운동을 생성하기 위해 압전 액추에이터는 x 및 y 방향에서 90° 위상차를 갖는 정현파 신호에 의해 구동되었습니다. 가공된 나노채널의 너비는 생성된 원형 운동의 진폭에 따라 다릅니다. 압전 액츄에이터에 입력되는 구동 전압의 범위는 30 V ~ 150 V, 간격은 30 V로 설정하였으며, 추가적으로 100 Hz와 1500 Hz의 두 가지 잠수 주파수를 선정하였다. 에지-포워드 방향을 따라 가공하는 동안 재료는 쌓이는 형태로 배출되고 종종 나노 채널의 양쪽에 균일하게 분포되는 것으로 발견되며 [45], 접합 과정에서 나노 유체 칩의 누출을 방지하는 데 도움이 됩니다. 따라서 본 연구에서는 edge-forward 가공 방향을 선택하였다. AFM 시스템의 Nanoman 모듈을 사용하여 80μm 길이의 나노 채널을 제작했습니다. 모든 가공 공정은 이송 값의 영향을 받습니다. 따라서 이러한 영향을 제거하려면 구동 주파수에 따라 이송 속도를 변경해야 합니다. 본 연구에서는 이송값을 10 nm로 설정하였고, 100 Hz와 1500 Hz 주파수에 대한 이송속도는 각각 1 μm/s와 15 μm/s로 계산하였다. 팁의 정상 부하는 위치 감지 광검출기(PSD)에서 생성된 출력 전압에 따라 다릅니다. 따라서 우리 연구에 사용된 다른 정상 부하는 상대 전압(설정점)을 설정하여 달성되었습니다. 우리의 이전 연구[46]에 따르면 가공 정상 하중은 Eq. (1) 구한 힘-거리 곡선의 기울기로부터 감도를 측정하였다[47].

$$ {F}_{\mathrm{N}}={V}_{\mathrm{setpoint}}\times 감도\times {K}_{\mathrm{N}} $$ (1) <그림><소스 유형="이미지/webp" srcset="//media.springerature.com/lw685/springer-static/image/art%3A10.1186%2Fs11671-019-2962-6/MediaObjects/11671_2019_2962_Fig2as=webpng? ">

나노유체 칩 제조 순서도:(a1)-(a6) PDMS 칩에서 마이크로채널 제조 작업 단계; (a1) 리소그래피 기판에 사용되는 실리콘 시트; (a2) Si 기판에 SU8 포토레지스트의 스핀 코팅; (a3) SU8 층을 UV 광에 노출; (a4) 얻어진 볼록 미세구조; (a5) 마이크로채널 몰드 상의 PDMS 코팅; (a6) 마이크로채널이 있는 최종 PDMS 칩; (b1)-(b2) PDMS 칩에서 나노채널 제작 작업 단계; (b1) PC 시트의 AFM 팁 긁힘; (b2) 스크래칭 후 얻은 나노채널 몰드; (b3) 나노채널 몰드 상의 A-PDMS 코팅; (b4) 볼록한 나노구조를 갖는 A-PDMS 칩; (b5) A-PDMS 금형에 일반 PDMS 코팅; (b6) 나노채널이 있는 최종 PDMS 칩; (c) 결합 후 PDMS 나노유체 칩

따라서 나노밀링 공정의 일반 하중은 17μN 및 25μN으로 설정되었습니다. 또한 비교를 위해 PC 시트의 나노 채널 몰드도 진동 없이 제작되었으며 이 방법을 단일 스크래칭이라고 합니다. 단일 스크래칭 공정에 대한 일반 하중은 25 μN, 33 μN, 42 μN, 50 μN 및 58 μN으로 설정되었습니다. 나노채널 몰드 단면의 개략도는 그림 2(b2)에 나와 있습니다.

마이크로 채널 몰드는 UV 리소그래피 공정에 의해 준비되었습니다. 그림 2(a1-a4)의 순서도는 리소그래피 공정의 세부 작업을 보여줍니다. 포토레지스트(SU-82015; MicroChem, USA)는 30 s 동안 500 rps 및 120 s 동안 4000 rps에서 Si 기판에 스핀 코팅되었습니다. 한 쌍의 "U"자형 마이크로채널이 마이크로채널 칩을 형성하고(그림 2(a6)), 나노채널에 의해 연결되어 최종 나노유체 칩을 형성합니다. 마이크로 채널의 너비는 30 μm이고 저장소의 직경은 1 mm입니다. 또한 두 개의 "U"자형 미세 채널 사이의 거리는 50 μm였습니다(추가 파일 1:그림 S1 및 S2).

볼록한 마이크로채널 몰드(그림 2(a4))와 오목한 나노채널 몰드(그림 2(b2))를 PDMS(Sylgard 184, Dow Corining, USA)로 옮겨 최종 나노유체 칩을 제조하였다. 그림 2(b3)-(b6)은 1차 전사와 2차 전사의 두 단계로 구성된 나노채널 몰드 전사의 기술적 과정을 보여줍니다. 나노채널 크기에 대한 단량체 대 경화제의 중량 비율의 영향을 조사하기 위해 세 가지 다른 PDMS 중량 비율(A-PDMS)이 첫 번째 및 두 번째 전달 과정에서 사용되었습니다. 1차 전사 인쇄 공정의 PDMS 중량비는 9:1, 7:1, 5:1로 설정한 반면, 2차 전사 인쇄 공정의 값은 10:1, 9:1, 8:1로 설정하였다. 그림 2(a5) 및 (a6)은 1단계 전사 방식을 사용한 마이크로채널 몰드의 전사 과정을 보여줍니다. 10:1의 PDMS 중량비는 볼록한 마이크로채널의 전달에 사용되었습니다. 모든 전사 인쇄 과정에서 2액형 PDMS 엘라스토머를 먼저 균일하게 교반한 다음 케이스에 부어 금형을 준비했습니다. 그런 다음 케이스를 30분 동안 진공 데시케이터에 보관하고 2-3회 탈기하여 갇힌 기포를 모두 제거했습니다. 준비된 몰드를 80ºC의 가열 오븐에 4시간 동안 보관한 후 최종적으로 PDMS 레플리카를 몰드에서 부드럽게 벗겨냈습니다.

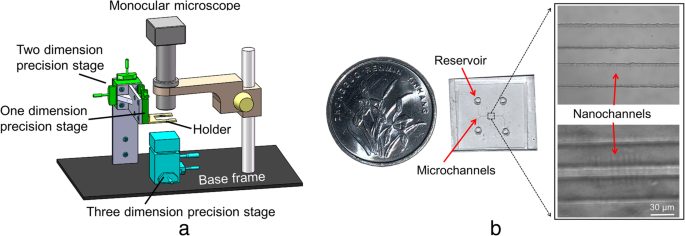

준비된 나노유체 칩을 1.5mbar의 챔버 압력과 81 W의 챔버 전력에서 32초 동안 산소 플라즈마 처리(Zepto, Diener electronic, Germany)로 접합하였다(그림 2(c)). 마이크로 채널과 나노 채널의 표면은 스카치 테이프로 청소되었고 PDMS 마이크로 채널 칩의 4개의 저장소는 접합 전에 펀칭되었습니다. 플라즈마 처리 후 깨끗한 칩을 유지하기 위해 탈이온수를 사용했으며 홀더, 단안 현미경, 1차원 정밀 스테이지(TSDT-401S; SIGMAKOKI, Japan)로 구성된 수제 정렬 시스템을 사용하여 칩을 함께 정렬했습니다. ) (그림 3a). 수제 정렬 시스템에 대한 자세한 내용은 ESI에서 찾을 수 있습니다. 그런 다음 밀폐된 마이크로/나노채널 칩을 얻기 위해 칩을 95°C의 온도에서 20분 동안 접합했습니다(그림 3b).

<그림>

아 수제 정렬 시스템 및 b의 개략도 나노유체 칩

2차원 압전 액추에이터는 AFM 팁 기반 나노밀링 시스템에서 회전 운동을 수행하는 중요한 구성 요소입니다. 따라서 다양한 구동 전압 및 주파수에서 동작을 특성화하기 위해 예비 긁힘 테스트가 수행되었습니다. 스캔 범위가 0 nm인 접촉 모델에서 AFM 팁은 먼저 주어진 정상 하중에서 PC 시트의 표면에 접근하고 정적으로 유지되었습니다. 2차원 압전 액추에이터의 회전은 미리 설정된 주파수와 전압에 의해 제어되었습니다. Scratch 과정이 끝나면 AFM tip을 PC sheet 표면에서 들어올렸다. 따라서 압전 액츄에이터의 운동 진폭은 구동 전압과 주파수의 함수로 얻어졌습니다. 구동 전압은 30~150 V의 범위에서 30 V의 간격으로 설정하였고, 구동 주파수는 100 Hz와 1500 Hz로 설정하였다. 두 개의 구동 주파수에서 측정된 진폭과 구동 전압 간의 관계는 추가 파일 1:그림 S3에 표시됩니다. 구동전압이 증가함에 따라 가공진폭의 값이 증가함을 알 수 있으며, 1500 Hz에서 가공진폭의 값이 100 Hz보다 큰 것을 알 수 있다. 제안된 방법으로 제작된 나노채널의 폭은 350 nm에서 690 nm 사이인 것으로 나타났습니다.

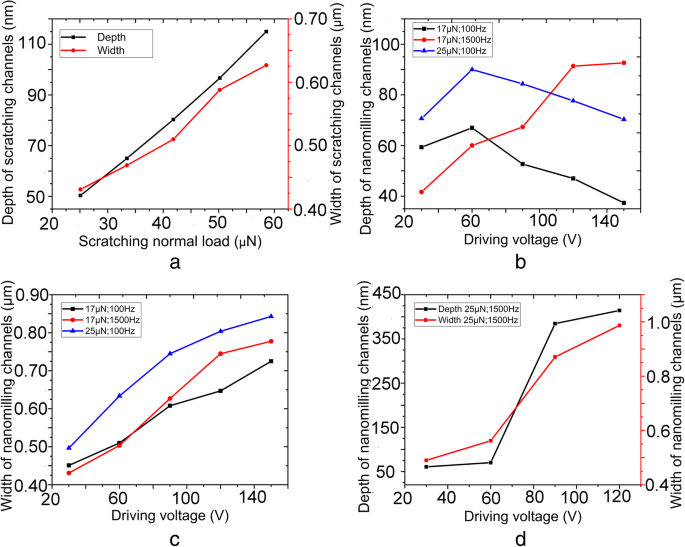

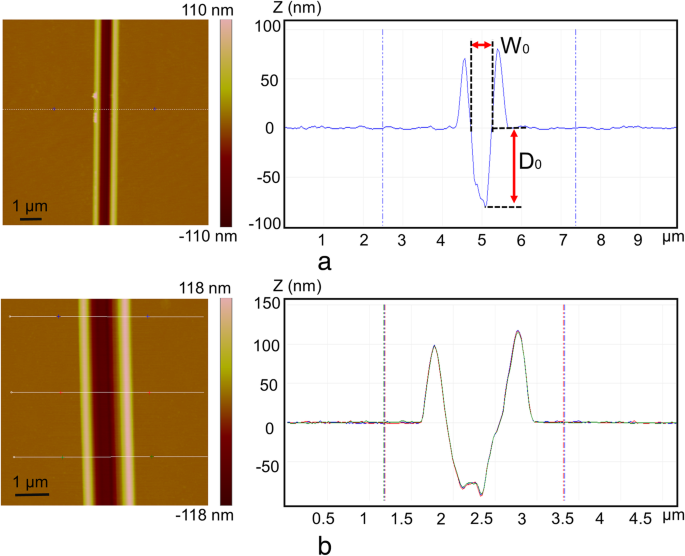

단일 긁힘 및 나노 밀링에서 나노 채널 크기와 가공 매개 변수 간의 관계는 각각 그림 4a 및 b에 나와 있습니다. 가공된 나노채널의 너비와 깊이는 W로 표시됩니다. 0 그리고 디 0 , 각각(그림 5a).

<그림>

가공된 나노채널 크기와 가공 매개변수 간의 관계:a 일반 하중의 단일 긁힘 범위는 25 μN ~ 58 μN, b 깊이 및 c 17 μN, 25 μN의 일반 부하 및 100 Hz, 150 Hz, d의 구동 주파수로 제작할 때 가공된 채널의 너비 25 μN의 일반 하중과 1500 Hz의 구동 주파수로 제작할 때 가공된 채널의 깊이와 너비

<그림>

가공 매개변수가 다른 가공된 나노채널의 일반적인 AFM 이미지:a 42 μN의 일반 하중에서 긁힘. ㄴ 일반 부하 25μN, 주파수 100 Hz, 구동 전압 60 V

에서 나노 밀링Fig. 4a에서 수직하중이 증가함에 따라 제작된 나노채널의 폭과 깊이가 증가함을 알 수 있다. 42μN의 정상 하중에서 긁힘의 일반적인 AFM 이미지가 그림 5a에 나와 있습니다. 나노채널에서 물질이 배출되어 나노채널의 양쪽에 균일하게 분포된 더미를 형성하는 것이 눈에 띕니다. 원자현미경 팁의 모양은 가공 과정에서 가장자리 "OA"에 의해 형성된 표면과 대칭이기 때문입니다(그림 1b). 따라서 재료는 edge-forward 긁는 동안 팁의 앞쪽 가장자리에 의해 균일하게 배출됩니다. 그림 4b, c, d는 가공된 나노채널 크기와 구동 전압 사이의 관계를 보여줍니다. 도 4b에서 나노채널의 깊이는 처음에 증가하다가 17μN 및 25μN의 정상 부하에서 100 Hz의 주파수에서 감소하기 시작했음이 분명하다. 우리 연구에 사용된 PC 시트는 높은 변형 수준에서 지수 변형 경화의 조합으로 탄성-점소성 거동을 나타내는 비정질 폴리머였습니다[48, 49]. 가공 중 정상 하중은 Eq. (2), 여기서 \( \overrightarrow{n} \) 및 \( \overrightarrow{t} \)는 각각 유동선 벡터에 대한 단위 법선 및 단위 접선입니다. p 그리고 τ 국부 수직 압력과 전단 응력을 각각 나타내며 \( \overrightarrow{z} \)는 수직 단위 [50]입니다.

$$ {F}_{\mathrm{N}}=p\cdot \int \overrightarrow{n}\cdot \overrightarrow{z} ds-\tau \cdot \int \overrightarrow{t}\cdot \overrightarrow{zds } $$ (2)본 연구에서는 제작된 나노채널의 치수 크기가 나노스케일에서 발견되었으므로 국부적 수직압과 전단응력 값은 일정하다고 가정하였다. 또한, 식. (2)를 식의 단순화된 형태로 변환하였다. (3), 여기서 S n 그리고 S 어 각각 AFM 팁과 샘플 사이 인터페이스의 수평 및 수직 투영입니다.

$$ {F}_{\mathrm{N}}=p\cdot {S}_n-\tau \cdot {S}_h $$ (3)S 간의 관계 n 그리고 S 어 식으로 표현된다. (4) 여기서 α 및 β 각각은 팁 표면과 수직 및 수평면 사이의 끼인각입니다.

$$ {S}_{\mathrm{n}}=\frac{S_{\mathrm{h}}}{\cos \alpha}\cdot \cos \베타 $$ (4)정상 하중은 Eq.에 의해 계산되었습니다. (5).

$$ {F}_{\mathrm{N}}=\left(p\cdot \frac{\cos \beta }{\cos \alpha }-\tau \right)\cdot {S}_h $$ (5 )Eq.에서 분명합니다. (1) 일반 하중의 값은 전체 가공 과정에서 일정합니다. Briscoe et al.에 따르면 [51], 평균 변형률의 값은 Eq. (6), 여기서 V 그리고 w 각각 팁 속도와 절단되지 않은 칩 두께를 나타냅니다. 절단되지 않은 칩 두께의 최대값은 ~ 10 nm로 발견되었습니다.

$$ {}_{\varepsilon}^{\bullet }=\frac{\mathrm{d}\varepsilon }{\mathrm{d}t}\approx \frac{V}{w} $$ (6)또한, 팁 속도의 값은 Eq. (7), 여기서 f 입력 신호 주파수입니다.

$$ V=\pi \cdot {W}_o\cdot f $$ (7)100 Hz에서의 평균 변형률 값은 1.42 × 10 4 범위에서 발견되었습니다. s -1 ~ 2.27 × 10 4 s -1 . 국부 정상 압력 값(p ) 변형률 속도가 1.42 × 10 4 범위일 때 변형률 속도가 증가함에 따라 증가하기 시작했습니다. s -1 ~ 2.27 × 10 4 s -1 [52]. τ의 값 p보다 훨씬 작았습니다. , 이는 일반 부하가 주로 p에 의존함을 나타냅니다. . 따라서 정상부하(FN) 값을 유지하기 위해 ) 전체 가공 공정 동안 일정하고 가공 깊이 값은 더 높은 구동 전압에서 더 작아야 합니다. 그러나 제작된 나노채널의 최종 치수 크기는 샘플 재료의 회복에 영향을 받았습니다. 142~227 μm/s 범위에서 가공속도가 증가함에 따라 시편의 회수율이 감소 [53]하여 30 V에서 더 높은 탄성회복이 발생함을 알 수 있으며, 30 V에서 제작된 나노채널의 깊이 (~142 μm/s)는 60 V(~161 μm/s)보다 얕았다. 추가 파일 1:그림 S4(a) 및 그림 5b는 각각 17μN 및 25μN의 정상 부하에서 100 Hz로 가공된 나노채널의 일반적인 AFM 이미지입니다. 나노채널의 오른쪽에 쌓이는 것이 왼쪽보다 큰 것을 알 수 있다. 나노 밀링 과정에서 샘플의 회전 운동은 반시계 방향이며 회전에 따라 주 절삭 날의 절단 각도가 변경됩니다. 절단되지 않은 칩 두께는 나노밀링 프로세스의 시작과 끝에서 칩을 형성하기에는 너무 작습니다. 나노 밀링 공정의 중간에서 절단되지 않은 칩 두께는 상대적으로 큽니다. 그러나 작은 받음각은 파일업의 형성에 기여합니다. 따라서 더 많은 재료가 채널의 오른쪽으로 밀려나고 쌓이는 비대칭입니다. 비대칭 말뚝 형성에 대한 자세한 내용은 이전 연구[54]에서 찾을 수 있습니다.

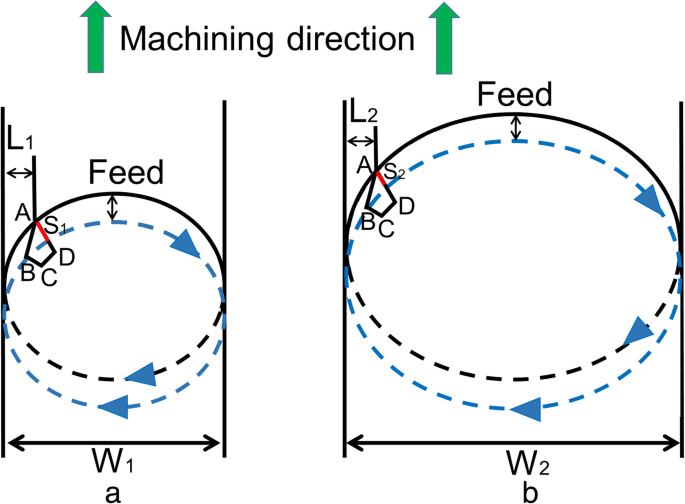

17 μN 및 25 μN의 정상 부하에서 1500 Hz에서 구동 전압이 증가함에 따라 나노 채널의 깊이가 증가하기 시작했음을 그림 4b 및 d에서 확인할 수 있습니다. 그림 4d는 나노 채널 깊이가 25 μN의 정상 부하에서 60 V(~ 2.64 mm/s)에서 90 V(~ 4.10 mm/s)로 급격히 증가했음을 보여줍니다. Geng et al.에 따르면 [55], 재료 제거 상태는 절삭 속도에 크게 영향을 받는다. 재료는 2.64 mm/s의 속도로 가공하는 동안 쌓인 형태로 나노 채널에서 배출되는 반면 재료 제거 상태는 4.10 mm/s에서 더미에서 칩으로 변경되었습니다(추가 파일 1:그림 S4(b)). . 따라서 90 V(~4.10 mm/s)에서 가공 깊이의 증가는 재료 제거 상태의 변화에 기인할 수 있습니다. 제작된 나노채널의 폭은 구동 전압이 증가함에 따라 증가하기 시작했다. 그림 6은 나노 밀링 중 AFM 팁 궤적의 개략도를 표시하고, 점선 타원, 검은색 실선 타원 및 파란색 화살표는 각각 완성된 가공 프로세스, 진행 중인 가공 프로세스 및 AFM 팁의 동작 방향을 나타냅니다. 너비(W 2 )은 Fig. 6(b)의 가공된 채널(W 1 ) 그림 6(a). 그대로1 및 AS2 (빨간색 실선)은 AFM 팁의 단면과 샘플 재료 사이의 접촉 길이를 나타냅니다. AS1의 값 AS2보다 큰 것으로 확인되었습니다. 가공 너비 "L 1 "는 "L 2. "

<그림>

나노밀링 공정 중 AFM 팁 궤적의 도식적 표현:나노채널의 가공된 너비(a ) 나노채널(b)보다 작습니다. ), 점선 타원, 검은색 실선 타원 및 파란색 화살표는 각각 완성된 가공 공정, 진행 중인 가공 공정 및 AFM 팁의 이동 방향을 나타냅니다.

Sh의 값 식에서 (5)는 식에 의해 얻어졌다. (8), 여기서 D와 AS는 각각 가공된 채널의 깊이와 AFM 팁의 단면과 샘플 재료 사이의 접촉 길이입니다.

$$ {S}_h=\frac{1}{2}\cdot \left|D\left|\cdot \right|\; 그대로\오른쪽| $$ (8)따라서 식. (5)는 Eq. (9).

$$ {F}_{\mathrm{N}}=\frac{1}{2}\cdot \left(p\cdot \frac{\cos \beta }{\cos \alpha }-\tau \right) \cdot \left|D\left|\cdot \right| 그대로\오른쪽| $$ (9)α의 값 및 β 전체 가공 공정 동안 일정하게 유지되었습니다. 1500 Hz에서의 변형률 값은 2.03 × 10 5 범위에서 발견되었습니다. ~3.66 × 10 5 s -1 ; 따라서 국부 정상 압력(p ) 1500 Hz에서 한계값에 도달했습니다. 또한, 가공 속도는 30–150 V(~ 2.03–3.66 mm/s)에서 가공하는 동안 샘플의 회복에 영향을 미치지 않았습니다[53]. 따라서 나노 채널의 최종 치수 크기는 가공 치수에 의해서만 결정되었습니다. AS2의 값 (Fig. 6(b)) AS1보다 작은 것으로 나타났다. (그림 6(a)) 더 큰 가공 너비의 경우 Eq. (9), D의 값은 AS의 값이 작을수록 크다. 따라서 구동 전압이 증가함에 따라 가공 깊이 값이 증가했습니다. 25 μN의 정상 부하, 120 V의 구동 전압, 1500 Hz의 주파수에서 제작된 나노채널의 일반적인 AFM 이미지는 추가 파일 1:그림 S4(b)에 나와 있습니다. 칩과 더미 형성 모두에서 물질이 제거되었고, 배출된 물질은 나노채널의 한 면에만 축적되었음을 알 수 있다. 또한, 25μN의 정상 하중에서 150 V에서 가공하는 동안 배출된 물질이 나노 채널 바닥에 칩 형성으로 축적되었습니다. 따라서 150 V의 전압과 1500 Hz의 주파수(정상 부하 25μN)에서 가공하는 동안 제작된 나노 채널의 크기 데이터는 그림 4d에서 비어 있습니다.

도 4c에서 나노채널 폭은 구동 전압이 증가함에 따라 증가하기 시작했음이 분명하다. 또한, 정상부하와 구동전압 값을 일정하게 유지하였을 때 1500 Hz의 주파수에서 제작된 나노채널의 폭은 100 Hz의 폭보다 넓었다. 또한, 1500 Hz에서 제작된 나노채널의 가공깊이는 100 Hz보다 깊었고, 더 깊은 나노채널을 가공하는 동안 팁의 단면크기가 더 큰 것으로 나타났다. 따라서 더 깊게 가공할 때 나노 채널이 더 넓게 제작되었습니다.

25 μN, 33 μN, 41 μN, 50 μN 및 58 μN의 일반 하중에서 단일 긁힘 방법으로 가공된 나노 채널이 첫 번째 전달 프로세스에 적용되었습니다. 또한, 30~150 V의 구동 전압 범위(30 V의 간격)에서 100 Hz의 주파수에서 나노 밀링으로 제작된 나노 채널 몰드도 전사 공정에 사용되었습니다. 단일 스크래칭 방식으로 가공된 나노채널(80 nm 깊이 및 510 nm 너비)을 "나노채널 I"이라고 하는 반면, 나노밀링으로 가공된 나노채널(50 nm 깊이 및 610 nm 너비, 90 nm 깊이 및 630 nm 너비)을 "나노채널 I"로 명명했습니다. II” 및 “나노채널 III”, 각각. 세 가지 다른 PDMS 가중치 비율(5:1, 7:1 및 9:1)이 첫 번째 전송 프로세스에서 사용되었습니다.

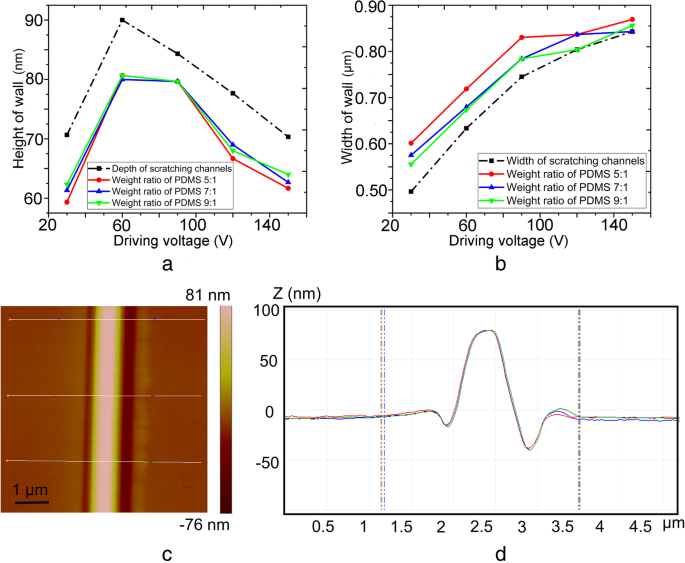

그림 7a와 b는 25 μN의 일반 하중과 100 Hz의 주파수에서 벽 크기에 대한 다양한 PDMS 가중치 비율의 영향을 나타내며 검은색 점선은 전송 전의 원래 나노채널 크기를 나타냅니다. 전형적인 AFM 이미지와 첫 번째 전송 동안 5:1의 중량비로 나노채널 III에서 얻은 벽의 해당 단면이 그림 7c 및 d에 표시되며 이 벽을 "벽 III"이라고 합니다. 17μN의 일반 하중과 100 Hz의 주파수로 단일 긁힘 프로세스에서 벽 크기에 대한 다양한 PDMS 중량 비율의 영향이 ESI에 표시되었습니다(추가 파일 1:ESI의 그림 S5, S6, S7 및 S8 참조). 자세한 내용은). The walls obtained from “nanochannel I” and “nanochannel II” were termed as “wall I” and “wall II,” respectively. It is evident that the heights of all walls at different PDMS weight ratios were approximately the same. The widths of the walls were larger than the original nanochannel width, and the width at the weight ratio of 5:1 was found to be the largest. Due to the thermal expansion of PC sheet, a small deviation was noticed between final wall size and original nanochannel size. It was also observed that the elasticity of PDMS increased as the PDMS weight ratio decreased from 5:1 to 7:1 [41, 42]. Hence, the wall obtained at the weight ratio of 5:1 was stiffer and its elastic recovery was smaller; thus, the width of the wall obtained at the weight ratio of 5:1 was the largest.

Relationship between a wall height, b wall width, and transfer parameters (various weight ratio of PDMS) during first transfer process, where the channel molds were fabricated with a normal load of 25 μN and a frequency of 100 Hz, and c typical AFM image and d corresponding cross-section of the wall obtained from nanochannel III at a weight ratio of 5:1

Second transfer of nanochannel molds

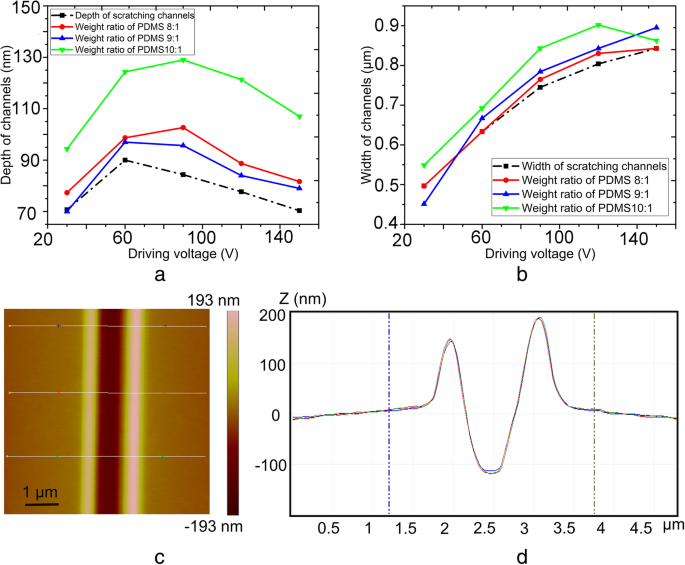

The final PDMS slabs with nanochannels were obtained during second transfer process based on the wall obtained at a weight ratio of 5:1 in the first transfer process. Three different PDMS weight ratios (10:1, 9:1, and 8:1) were used during second transfer process. Figure 8a and b present the relationship between nanochannel size obtained under a normal load of 25 μN and a frequency of 100 Hz and transfer parameters during second transfer. It is clear from Fig. 8a that the depths of the nanochannels were larger than the original machining size, moreover, the depth at 10:1 was found to be larger than other two ratios. Further, the widths of the wall were also larger than the original size, and the width at 10:1 was found to be the largest (Fig. 8b). Figure 8c and d present a typical AFM image and corresponding cross-section of the nanochannel (120 nm depth and 690 nm width) obtained from wall III at a weight ratio of 10:1 during second transfer, and it was termed as “nanochannel C.” The relationship between the nanochannel sizes obtained under single scratching process with a normal load of 25 μN and a frequency of 100 Hz and the transfer parameters during the second transfer process were shown in ESI (see Additional file 1:Figures. S9, S10, S11 and S12 of ESI for details), the nanochannels obtained from “wall I” and “wall II” were termed as “nanochannel A” and “nanochannel B”, respectively.

Relationship between a nanochannel height, b nanochannel width, and transfer parameters (various weight ratio of PDMS) during second transfer, where the channel molds were fabricated with a normal load of 25 μN and a frequency of 100 Hz, and c typical AFM image and d corresponding cross-section of the nanochannel obtained from wall III at a weight ratio of 10:1 during second transfer

The depths of nanochannels obtained from walls II and III were larger than the original machining size, whereas the depth obtained from wall I was smaller than the initial machining size. Furthermore, the changes in width were identical to the changes in depth. The aspect ratio of wall I was larger than those of walls II and III, thus each wall manifested different thermal expansion values. Hence, the changing trends of width and depth during second transfer were different though at the same PDMS weight ratio. The values of the depth and width of walls II and III at 9:1 and 8:1 were found to be closer to the original machining size compared with 10:1. Because the elastic recoveries of PDMS at 9:1and 8:1 are closer to 5:1 than 10:1, which indicates an almost similar recovery trend for PDMS at 9:1, 8:1, and 5:1.

Nanochannel devices are often used in the fields of single nanoparticle manipulation, electrokinetic transport phenomena, DNA analysis, and enzymatic reaction detection. The main working principle of nanofluidic chips depends on the variation in electric current; therefore, it is important to measure the electrical conductivities of nanochannel devices. The electrical conductance in a nanochannel can be estimated by Eq. (10) [56].

$$ G={10}^3N\;{}_Ae\frac{wh}{l}\sum {\mu}_i{c}_i+2{\mu}_e\frac{w}{l}{\delta}_n $$ (10)여기서 μ 나 is the mobility of ion i , c 나 is the concentration of ion i , δ n is the effective surface charge inside the nanochannel, and NA and e signify Avogadro constant and electron charge, besides, w , h and l are the nanochannel width, height and length, respectively. It is obvious that the electrical conductance of a nanochannel is affected by the nanochannel feature dimensions and the solution concentration. The electric double layer (EDL) plays an important role in the nanochannel when the ratio of DEL thickness to the nanochannel height increases. The diffuse layer thickness of EDL is 3~5 times of the Debye length (λ 디 ), which can be expressed by Eq. (11) [57].

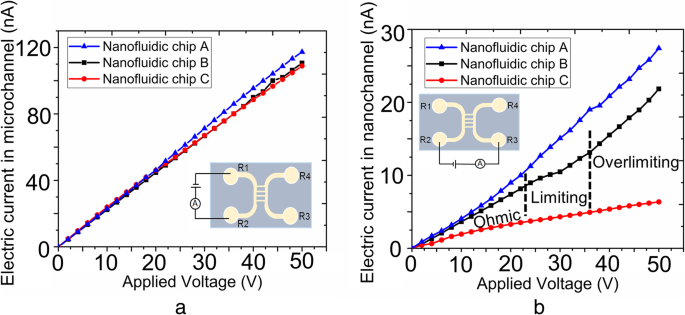

$$ {\lambda}_D=\sqrt{\frac{\varepsilon_0{\varepsilon}_r{k}_bT}{2{n}_{i\infty }{(ze)}^2}} $$ (11)여기서 n 나 ∞ denotes ion density in the solution, ε 오 is the permittivity of vacuum, ε r is the dielectric constant of electrolyte solution, z is the valency of buffer solution (z = z + − z - = 1 for KCl), and kb 그리고 T are the Boltzmann constant and temperature, respectively. In the present study, three different nanofluidic chips were obtained after the completion of transfer process. Nanofluidic chips consisted of nanochannels A, B, and C were termed as nanofluidic chips A, B, and C, respectively. Each nanofluidic chip contained four nanochannels. The widths and the depths of nanofluidic chips A, B, and C were measured as 60 nm and 500 nm, 80 nm and 680 nm, and 120 nm and 690 nm, respectively. The effective length of nanochannels in all chips was calculated as 50 μm. As shown in Fig. 8, pile-ups distribute on the sides of the nanochannels A, B, and C. The pile-ups may fill into the nanochannels and lead to a failure of the preparation for the nanofluidic chips. Thus, in order to verify the reliability of the fabricated nanochannel devices, electrical conductivity measurement test was conducted. KCl with 1 mM concentration was as the electrolyte solution in our study, and the values of electrical current were measured by an electrometer (Model 6430, Keithley, USA). The schematic sketches of the measurements for electric current in microchannel and nanochannel are presented as the inset figures in Fig. 9a and b, respectively. The experiments were carried out under DC power (applied by an Ag electrode) with an increment of 2 V for 3-s duration. Figure 9a presents the measured I -V curves of microchannels in three different nanofluidic chips, and a linear relationship between current and voltage was observed. Moreover, as the effect of EDL in microchannels was negligible and the dimensional sizes of microchannels in different nanofluidic devices were identical, the values of current in different chips were nearly the same. It is evident from Fig. 9b that the values of current in different nanofluidic devices were distinct due to different nanochannel sizes. For KCl solution of 1 mM concentration, the value of λ 디 was about 10 nm, thus the diffuse layer thickness of EDL was found as 30~50 nm [57]. Consequently, EDL got overlapped along the depth (60 nm) of nanofluidic chip A; however, no overlapping was observed in nanofluidic chip C (depth of 120 nm). However, it was difficult to determine whether EDL got overlapped or not in nanofluidic chip B (depth of 80 nm). It assumes that the effective surface charges (δ n ) in all nanochannels are identical as the charge density of a surface is material property [58, 59]. The concentration of the ions in a nanochannel depends on the EDL field, the stronger the EDL field, the higher the ion concentration in the nanochanel [44]. In the present study, the EDL field in nanofluidic chip A is the strongest as the highest ratio of the DEL thickness to the nanochannel height, which signifies that the ion concentration in the nanochannel of nanofluidic chip A is the highest. 식에 따르면 (10), the nanochannel of nanofluidic chip A is more conductive due to the higher ion concentration. Hence, the value of electrical current in nanofluidic chip A was the largest, whereas nanofluidic chip C yielded the smallest value. In addition, at larger width sizes, EDLs did not overlap along the width directions of nanochannels. In nanofluidic chip B, when the value of applied electric field was lower than 25 V, a linear relationship was noticed between current and applied voltage; however, a limiting region appeared as the value of applied voltage increased and finally, became liner again as the electrical field increased further, this phenomenon belongs to ohmic-limiting-overlimiting current characteristic [60, 61]. The results of electrical current measurement revealed that the nanofluidic devices fabricated by the proposed method were effective, the pile-ups of the nanochannels A, B, and C had almost no influence on the performance of the nanofluidic devices.

Electric current measurement results based on the fabricated nanochannel devices, the cross-section size (depth × width) of nanochannels for nanofluidic chip A, B, and C are 60 × 500 nm, 80 × 680 nm and 120 × 690 nm, respectively. 아 Current in microchannels. ㄴ Current in nanochannels. The insets display the schematic sketches of the measurements

In the present research, nanochannels with controllable sizes (sub-100-nm depth) were fabricated by AFM tip-based nanomilling, and for the first time, the machined nanochannels were applied to prepare nanofluidic devices. The multichannel nanofluidic devices were prepared in four steps:(1) fabrication of nanochannels by AFM tip and piezoelectric actuator, (2) fabrication of microchannels by lithography, (3) transfer of micro- and nanochannels, and (iv) bonding. Further, nanochannel sizes were controlled by changing the driving voltages and frequencies inputted to the actuator. The heights of the wall obtained during first transfer were smaller than the original machining size, whereas the widths were larger than the original machining size. The experiment results revealed that during second transfer process, nanochannel sizes affected PDMS weight ratios. Finally, micro-nanofluidic chips with three different nanochannel sizes were obtained by bonding a PDMS nanochannel chip on a PDMS microchannel chip. Moreover, the electrical current measurement experiment was conducted on the fabricated nanofluidic chips, and it was found that the values of current were affected by nanochannel sizes. Therefore, PDMS nanofluidic devices with multiple nanochannels of sub-100-nm depth can be efficiently and economically fabricated by the proposed method.

Compared with other fabrication approach, the proposed method for fabrication of the nanofluidic devices in the study is easy to use and low cost; besides, the nanochannels with controllable dimension size can be obtained easily. However, the commercial AFM system cannot equip with a large-scale high-precision stage due to the spatial limitation; thus, the maximum fabrication length of the nanochannel is confined as 80 μm. In addition, the tip wear cannot be neglected after long-term fabrication due to the high machining speed, which should be investigated in future work.

원자력 현미경

직류

Electric double layer

Potassium chloride

Polycarbonate

폴리디메틸실록산

Position-sensitive photodetector

나노물질

고품질 제작 파트너는 제작이 필요한 모든 산업에 필요한 전문 지식을 보유하게 됩니다. 많은 조립 공장에서 제품의 구성 요소를 사내에서 완성할 수 있다고 가정하지만 제작자를 통합하면 제품의 경쟁력을 높일 수 있습니다. 금속 가공에 있어 전문가를 활용하는 것은 비할 바가 아닙니다. 패브리케이터를 생산 공정의 확장으로 사용 생산 공정의 연장선상에서 제작자와 파트너 관계를 맺는 것을 살펴보십시오. 그들은 전문 지식을 어셈블리에 통합하여 제조 단계를 다음 단계로 진행할 수 있습니다. 귀하의 제품은 제작자에게 배송될 수 있고, 제작 단계

구조용 강철 제작은 성공적으로 완료하기 위해 전문 지식, 기술 및 리소스가 필요한 다면적인 프로세스입니다. 구조용 강철 빔, 구성 요소 또는 장비를 만들기 위해 우수한 금속 제작자는 특정 프로세스를 따릅니다. 1단계:구상 아이디어 단계는 고객이 원하는 만큼 창의적이거나 표준적일 수 있습니다. 맞춤형 구조용 강철 솔루션을 제공하는 제작자와 협력하면 프로젝트에 맞는 고유한 부품을 자유롭게 주문할 수 있습니다. 아름다운 수제 장식용 레일이 필요하든 직선형 케이지 사다리가 필요하든 맞춤형 제작자가 귀하의 요구 사항을 정확하게 충족할 수