나노물질

본 논문에서는 과도 향상과 과전류 보호(OCP)를 통합한 고안정성 전압 조정기(VR)를 제안한다. 저전압 장치의 성능과 면적상의 장점을 고려할 때 제안된 VR의 대부분의 제어 부분은 PSR(Power Supply Rejection) 부스팅과 함께 자체 전원 기술(SPT)을 형성하는 조정된 출력 전압에 의해 공급됩니다. 게다가, 안정성과 과도 응답은 동적 부하 기술(DLT)에 의해 향상됩니다. 과부하 상황에서 제시된 VR을 손상으로부터 보호하기 위해 임베디드 과전류 피드백 루프도 채택되었습니다. 제안된 VR은 표준 350 nm BCD 기술로 구현되며, 그 결과 VR이 5.5–30 V 입력 전압, 0–30 mA 부하 범위 및 0.1–3.3 μF 출력 커패시터에서 안정적으로 작동할 수 있음을 나타냅니다. 2.98 μV/V 라인 조정 및 0.233 mV/mA 부하 조정은 40 mA 전류 제한으로 달성됩니다. PSR은 0.1 μF 출력 커패시터에서 최대 10 MHz까지 -64 dB보다 우수합니다.

최신 나노미터 규모의 SoC(시스템 온 칩) 설계에서 특정 기능을 달성하려면 일반적으로 서로 다른 하위 블록에 서로 다른 공급 레일이 필요합니다. 게다가 전체 SoC 시스템은 광범위한 입력 전압에서 작동해야 하며 공급 조건의 변화에 영향을 받지 않고 여전히 고성능을 제공해야 합니다[1]. 따라서 나노미터 규모의 기술로 구현된 넓은 입력 전압 범위 전압 조정기(VR)는 이러한 종류의 애플리케이션에 가장 적합한 후보 중 하나가 될 수 있습니다. 선형 VR은 스위칭 레귤레이터 및 차지 펌프와 같은 스위칭 상대와 비교하여 고정밀, 낮은 출력 노이즈 및 소형 크기의 이점이 있습니다. 대부분의 선형 VR은 단일 전압 공급으로 전압 조절 기능을 수행하지만, 넓은 전원 공급 범위, 저잡음, 빠른 과도 상태, 고부하 기능 및 추가 보호 기능의 조합을 달성할 수 있는 것은 극소수에 불과합니다. [2,3,4] .

넓은 전원 공급 범위를 구현하려면 높은 전압 압력에 견딜 수 있는 트랜지스터의 활용이 필요합니다. 그러나 이러한 종류의 트랜지스터는 일반적으로 표준 트랜지스터에 비해 더 많은 면적을 차지하고 성능이 떨어집니다. 고전압 트랜지스터의 사용을 줄이기 위한 기존 솔루션 중 두 가지는 프리레귤레이터 방식[5, 6]과 스택형 저전압 트랜지스터 방식[7, 8]입니다. 전자는 코어 레귤레이터에 내부 공급 전압을 제공하기 위해 추가 프리레귤레이터를 사용합니다. 후자는 기술 한계 내에서 트랜지스터의 단자 전압을 유지하기 위해 잘 설계된 적층형 저전압 트랜지스터를 구현합니다[7]. 그러나 이러한 방법은 전압 헤드룸을 제한합니다. 이 논문은 넓은 전원 공급 범위를 달성하기 위해 자체 전원 기술(SPT)을 채택합니다. 이는 레귤레이션 루프의 대부분의 코어 모듈이 제안된 VR의 레귤레이트된 출력 전압에 의해 공급된다는 것을 의미합니다[9]. 별도의 회로 없이 SPT를 통해 VR의 성능을 향상시킬 수 있으며 고전압 기기의 수를 줄일 수 있습니다.

SPT를 사용하여 오류 증폭기(EA)의 첫 번째 이득 단계는 제안된 VR의 조정된 출력 전압에 의해 공급됩니다. EA의 두 번째 단계를 신중하게 설계함으로써 입력 전압의 고주파 노이즈가 EA의 출력 전압에 거의 영향을 미치지 않습니다. 또한 본 논문에서는 N형 파워 트랜지스터 아키텍처를 채택하였다. 따라서 제안하는 레귤레이터는 PSR(Power Supply Rejection)이 높고 잡음 성능이 좋다[10,11,12,13,14,15].

빠른 과도 응답은 일반적으로 추가 속도 향상 루프를 추가하여 달성되는 VR[16,17,18,19,20]의 성능을 측정하는 중요한 지표이기도 합니다[21]. 본 논문에서는 DLT(Dynamic Load Technique)를 통해 트랜션트 향상을 구현한다. 과도 응답 절차 동안 DLT는 부하 조건에 따라 변경되는 추가 전류를 도입하여 동적 부하로 작용하여 조정된 출력 전압의 오버슈트 및 언더슈트를 억제할 수 있습니다[9].

DLT의 도움으로 추가 부하 전류가 비우세 극 위치의 변동을 줄일 수 있기 때문에 넓은 부하 범위 내에서 루프 안정성이 강화됩니다. 루프를 안정적으로 만들기 위해 널링 저항을 사용한 밀러 보상은 저주파 극점과 출력 극점을 보상하기 위한 추가 영점 생성에도 사용됩니다. 게다가, 출력 커패시터가 있는 저항 직렬은 파워 트랜지스터의 기생 게이트 커패시턴스에 의해 생성된 극을 보상하기 위해 또 다른 0을 도입합니다[6, 9, 22, 23].

마지막으로 내장된 전류 제한 루프는 과전류 손상을 방지하고 제안된 VR의 신뢰성을 향상하도록 설계되었습니다[9, 24,25,26,27].

본 논문은 다음과 같이 구성되어 있다. 제안된 VR의 원리와 메커니즘은 과전류 보호(OCP) 회로, DLT 및 과도 향상 회로, 안정성 부스팅 방법, PSR 분석을 포함하여 "방법" 섹션에 설명되어 있습니다. 성능 결과 및 다른 관련 출판된 문헌과의 비교는 "결과 및 토론" 섹션에 나와 있습니다. "결론" 섹션에서는 제안된 VR의 결론을 도출합니다.

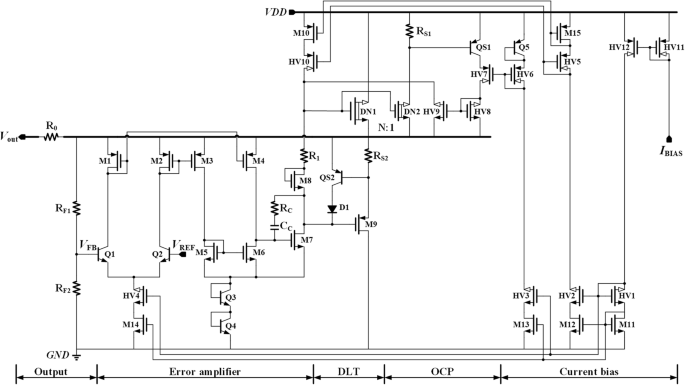

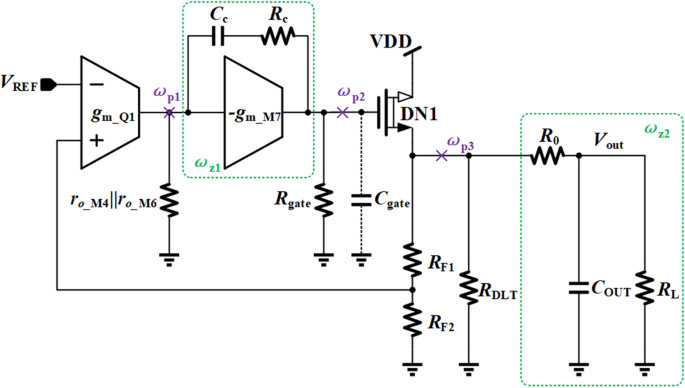

<섹션 데이터-제목="방법">제안된 VR의 세부 회로는 그림 1과 같다. 표준 저전압 MOS 트랜지스터, 고전압 트랜지스터, BJT, N형 공핍 LDMOS(측면 확산 MOS) 트랜지스터, 다이오드는 Mn , HVn , 질문n , DNn , 및 Dn , 각각 그림에서 n 해당 장치의 시퀀스 번호입니다.

<그림>

제안된 VR의 세부 회로

제안된 VR은 주로 전류 바이어스, OCP, DLT, EA 및 출력단의 5가지 하위 모듈을 포함합니다. 전류 바이어스 회로는 전체 레귤레이터 시스템에 바이어싱 전류를 제공합니다[12, 14]. 기준 전압은 다양한 방법으로 생성될 수 있으며[1] 자세한 회로는 여기에 표시되지 않습니다. 내장된 전류 제한 루프는 OCP 회로로 기능하여 부하 전류를 미리 설정된 값으로 제한합니다. DLT에 의해 구현된 과도 향상 회로는 과도 절차 동안 부하 전류를 적응적으로 변경하여 오버슈트 및 언더슈트 억제를 달성합니다. 네거티브 피드백 레귤레이션 루프는 EA와 출력 전력단에 의해 형성되어 출력 전압을 조정합니다. 출력 전압 V 밖 따라서 피드백 전압 V FB 값이 원하는 값보다 낮으면 레귤레이션 루프의 도움으로 전력 트랜지스터 DN1의 게이트 전압을 끌어올려 출력 전압을 높이거나 그 반대의 경우도 마찬가지입니다. 마지막으로 출력 전압은

에서 안정화될 수 있습니다. $$ {V}_{\mathrm{OUT}}\approx {V}_1={V}_{\mathrm{REF}}\left({R}_{\mathrm{f}1}+{R} _{\mathrm{f}2}\right)/{R}_{\mathrm{f}2} $$ (1)그림 1에서 제안된 VR의 출력 전압은 SPT로 명명된 EA의 첫 번째 이득단에도 전원을 공급함을 알 수 있다. 이 전력 다중화 기술을 사용하면 레귤레이션 루프에 있는 대부분의 장치를 저전압 장치로 구현할 수 있습니다. 고전압 장치와 비교할 때 저전압 장치는 성능이 더 높고 비용이 저렴하며 면적이 작아 제안된 조절 루프가 우수한 조절 능력을 훨씬 쉽게 달성할 수 있습니다. EA의 두 번째 단계에서는 Q3 및 Q4가 추가되어 접지 공급 레일을 들어올리며, 이는 M7, VDS_M7의 드레인-소스 전압을 제한하기 위해 채택됩니다. . 즉, Q3 및 Q4는 M7이 큰 전압 압력을 받는 것을 방지할 수 있습니다.

단순화를 위해 후속 분석에서 혁신 아이디어를 설명하기 위해 단순화된 회로가 사용되었습니다.

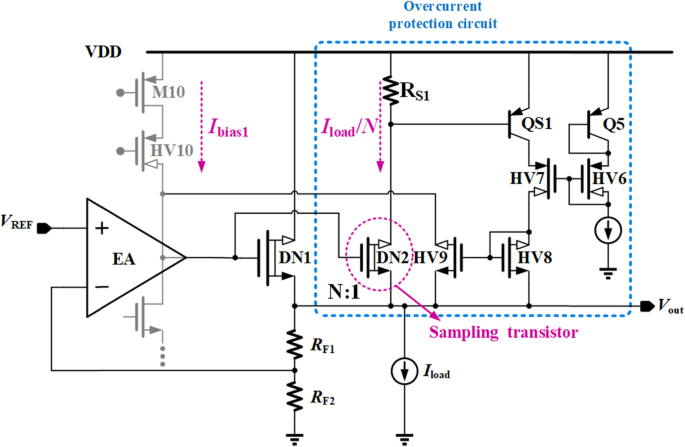

그림 2는 제안된 OCP 회로를 보여준다. 제안된 전류 제한 루프는 다양한 부하 조건에 따라 작동 모드를 자동으로 변경할 수 있습니다. 제안된 VR의 최대 전류는 과부하 발생 시 파워 트랜지스터의 게이트 전압을 감소시켜 제한할 수 있다.

<그림>

제안된 OCP의 원칙

제안하는 OCP의 메커니즘은 다음과 같다. 샘플링 트랜지스터 DN2는 부하 전류 I와 거의 동일한 DN1을 통해 흐르는 전류를 비례적으로 감지합니다. 로드 , 이는 R에 걸쳐 전압 강하를 만듭니다. S1 , V RS1 , 부하 전류 레벨을 반영합니다. 한 번 V RS1 QS1, HV8, HV9의 턴온 전압에 도달하면 EA의 두 번째 단계에서 전류를 바이패스하는 전류 미러를 형성합니다. 그런 다음 DN1의 게이트 전압을 풀다운하여 부하 전류를 미리 설정된 값으로 제한할 수 있으며, 이는 다음과 같이 표현될 수 있습니다.

$$ {I}_{\mathrm{Load}}\le N\times \left({V}_{EB\left(\mathrm{QS}1\right)}/{R}_{S1}\right ) $$ (2)여기서 N DN1 대 DN2의 크기 계수 비율입니다. Q5 및 HV6의 목적은 HV7에 적절한 바이어스 전압을 제공하여 과전압 상태로부터 QS1을 보호하는 것입니다.

제안된 OCP에는 음의 피드백 루프가 내장되어 있습니다. 루프 게인 T 그리고 지배적인 극 p 지배적인 이 전류 제한 루프는 다음과 같이 나타낼 수 있습니다.

$$ T={g}_{m\_\mathrm{DN}2}{R}_{S1}{g}_{m\_\mathrm{QS}1}{R}_{\mathrm{게이트 }\_\mathrm{OC}} $$ (3) $$ {p}_{\mathrm{우성}}=1/\left({R}_{\mathrm{게이트}\_\mathrm{OC} }{C}_{\mathrm{게이트}}\right) $$ (4)여기서 g m_DN2 그리고 g m_QS1 각각 DN2 및 QS1의 상호 컨덕턴스입니다. R 게이트_OC ≈ (g m_HV10 r o_HV10 r o_M10 ) || r o_M7 || r o_HV9 및 C 게이트 ≈ C gs_DN1 는 각각 과전류가 발생할 때 파워 트랜지스터 DN1의 게이트 노드에서 등가 출력 저항과 커패시턴스입니다. 제안된 VR이 과전류 없이 정상적으로 동작할 때 HV9는 차단 영역에 있으므로 DN1의 게이트 노드에서 등가 출력 저항은 R로 명명된다. 게이트 [(g m_HV10 r o_HV10 r o_M10 ) || r o_M7 ].

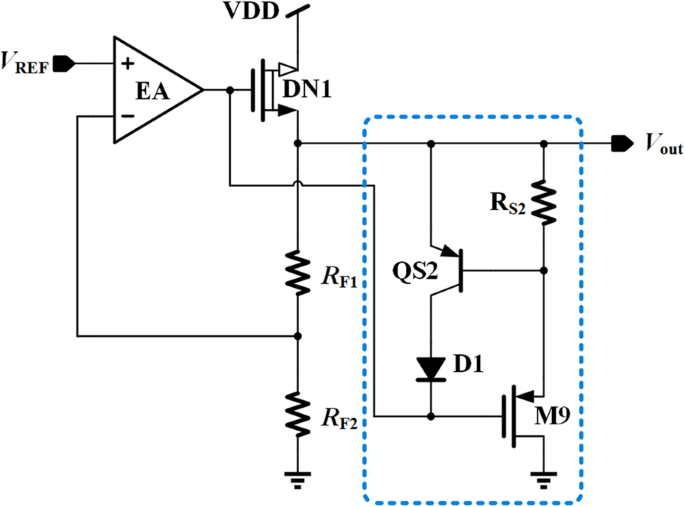

그림 3은 DLT를 사용한 과도 향상 회로를 보여줍니다. 부하 전류는 Vgs_DN1에 비례하고 Vsg_M9에 반비례하므로 M9를 통해 흐르는 전류는 경부하 조건에서 더 크고 중부하 조건에서 0에 가깝습니다. 따라서 부하 전류가 증가함에 따라 감소된 전류가 전체 출력 부하에 유입될 수 있습니다. 이 방법으로 이 회로는 동적 부하로 균등화될 수 있으며 이는 레귤레이션 루프의 과도 향상과 안정성 향상 모두에 도움이 될 수 있습니다.

<그림>

제안된 과도 향상 회로

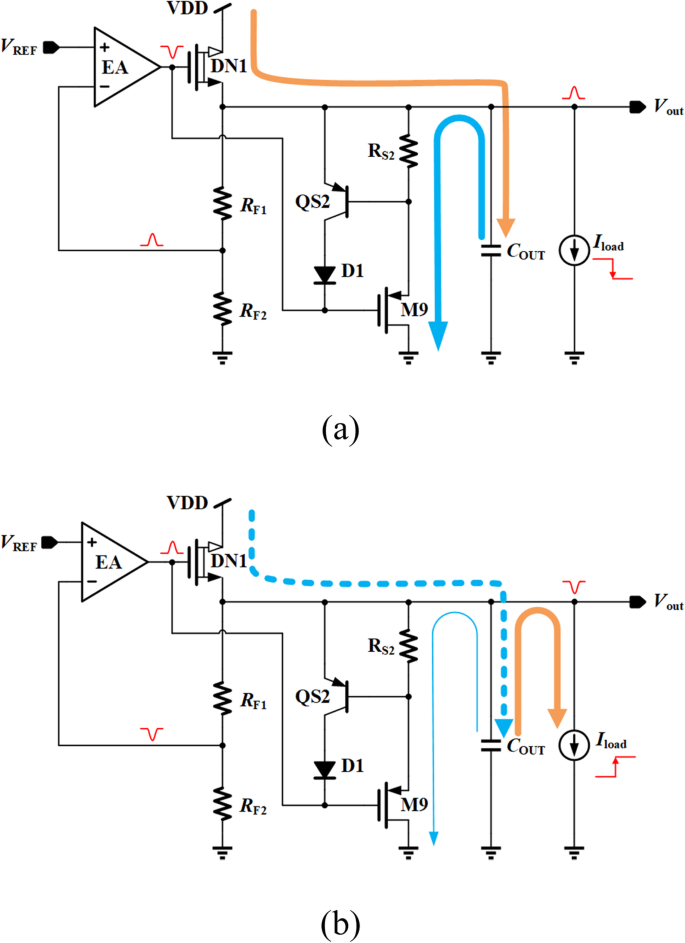

자세한 과도 향상 동작 원리는 다음과 같습니다. 부하 전류가 갑자기 감소하면 제한된 루프 조정 기능과 슬루율로 인해 전력 트랜지스터 DN1을 통해 흐르는 전류가 즉시 변경되지 않습니다. 그림 4a에 노란색 경로로 표시된 이 전류는 출력 전압에서 오버슈트를 일으켜 R 양단의 전압 강하를 증가시킵니다. S2 그리고 M9. 그런 다음 R을 통해 흐르는 추가 전류 S2 그림 4a에 파란색 경로로 표시된 M9는 조정된 출력에서 생성되어 원하지 않는 노란색 경로 전류를 상쇄합니다. 따라서 출력 전압 스파이크가 효과적으로 감소됩니다.

<그림>

제안된 VR의 일시적인 응답. 아 중부하에서 경부하 전류 변화. ㄴ 경부하에서 고부하 전류 변화

그림 4b는 조절된 출력에서 언더슈트가 발생한 다음 R을 통해 흐르는 전류인 경부하 전류 변화의 경우를 보여줍니다. S2 M9가 감소합니다. 이것은 감소된 전류 부하를 제공하는 것과 같을 수 있으므로 전력 트랜지스터 DN1을 통해 흐르는 순 전류가 증가하고 언더슈트 전압 억제가 달성될 수 있습니다.

과전류로부터 M9를 보호하기 위해 QS2 및 D1이 추가됩니다. R 양단의 전압이 S2 QS2의 턴온 전압보다 크면 추가 전류가 QS2와 D1으로 흐릅니다. M9의 최대 전류는

로 설정됩니다. $$ {I}_{\mathrm{M}9\_\max}\le \left({V}_{BE\_ QS2}/{R}_{S2}\right) $$ (5)D1의 목적은 QS2가 역 증폭 영역으로 떨어지고 역전류가 흐르는 것을 방지하는 것인데, 이는 M9 전류 제한 기능의 비정상 상태입니다.

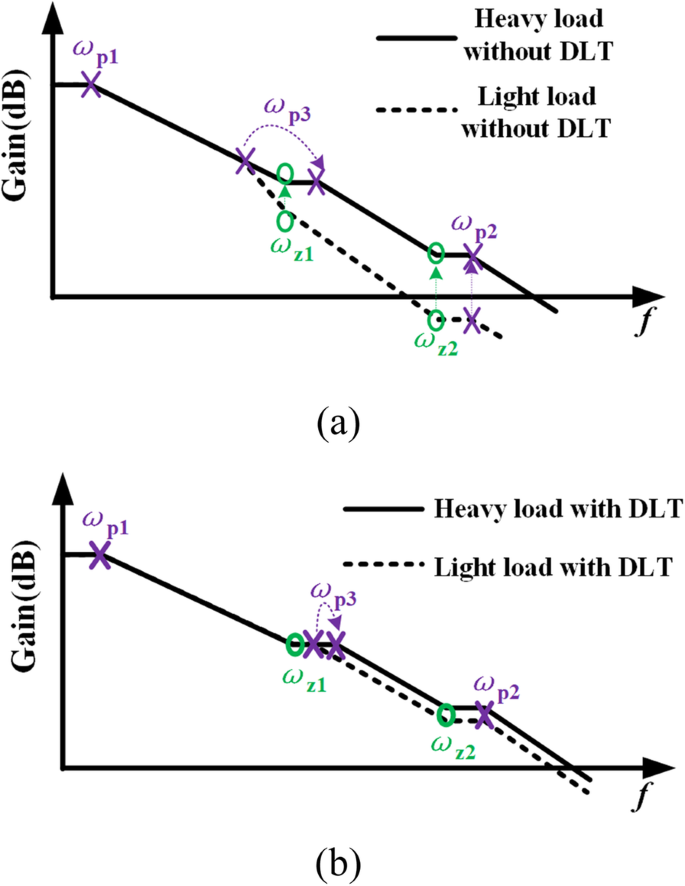

ω 3개의 극이 있다. p1 , ω p2 , 그리고 ω p3 , 그리고 두 개의 0 ω z1 그리고 ω z2 제어 루프에서 제안된 VR의 루프 이득은

$$ {A}_{\mathrm{Vloop}}={A}_O\beta $$ (6)

제안된 VR의 극점과 영점 분포

여기서 A 오 는 VR의 개방 루프 이득이고 β 피드백 계수,

$$ {A}_O={A}_{\mathrm{CD}0}{A}_{E0}\frac{\left(1+s/{\omega}_{Z1}\right)\left( 1+s/{\omega}_{Z2}\right)}{\left(1+s/{\omega}_{P1}\right)\left(1+s/{\omega}_{P3} \right)\left(1+s/{\omega}_{P2}\right)} $$ (7) $$ \beta =\frac{R_{\mathrm{F}2}}{R_{\mathrm {F}1}+{R}_{\mathrm{F}2}} $$ (8)여기서 A CD0 ≈ 1은 전압 팔로워로 작동하는 전력단의 저주파 이득이고 A E0 는 EA의 저주파 이득이고,

$$ {A}_{E0}={g}_{m\_Q1}\left({r}_{o\_M4}\Big\Vert {r}_{o\_M6}\right){g} _{m\_M7}{R}_{\mathrm{게이트}} $$ (9)DN1의 게이트 노드에서 Miller 효과와 기생 커패시턴스를 고려하여 극점과 영점은 [13]

$$ {\omega}_{p1}=1/\left[{g}_{m\_M7}{R}_{\mathrm{gate}}{C}_c\times \left({r}_{ o\_M4}\Big\Vert {r}_{o\_M6}\right)\right] $$ (10) $$ {\omega}_{p2}={g}_{m\_M7}/{ C}_{\mathrm{gate}} $$ (11) $$ {\omega}_{p3}=1/\left\{\left[{R}_L\Big\Vert \left({g}_ {m\_\mathrm{DN}1}^{-1}\Big\Vert {R}_{\mathrm{DLT}}+{R}_0\right)\right]{C}_{\mathrm{ OUT}}\right\} $$ (12) $$ {\omega}_{z1}=1/\left[{C}_c\left({R}_c-1/{g}_{m\_M7 }\right)\right] $$ (13) $$ {\omega}_{z2}=1/\left[\left({R}_0\Big\Vert {R}_L\right){C}_ {\mathrm{OUT}}\right] $$ (14)여기서 R DLT 과도 향상 회로의 등가 저항입니다. C 밖 는 제안된 VR의 출력 커패시터입니다.

보상 커패시터 C C (g만큼 확대됨 m_M7 R 게이트 ) 노드 p1에서 밀러 효과로 인해 극 ω p1 지배적인 극이다. 두 번째 극은 ω여야 합니다. p3 , C 때문에 밖 일반적으로 몇 마이크로패럿 범위에 있습니다. 기생 커패시터 C 게이트 상대적으로 크지만 노드 p1의 등가 커패시턴스와 출력 커패시터보다 여전히 작습니다. 게다가 노드 p2의 저항은 1/g에 불과합니다. m_M7 . 따라서 극 ω p2 고주파에 위치합니다. 제로 ω z1 중간 주파수 극을 취소하는 것입니다 ω p3 . 저항기 R 0 0 ω 생성 z2 내부 기생 극을 보상하기 위해 ω p2 . 제안된 VR의 안정성은 저항 R로 향상될 수 있습니다. 0 증가. 그러나 저항 R 0 부하 전류로 인한 전압 강하로 인해 출력 전압의 오차가 증가합니다. 따라서 저항 R 0 출력 전압의 정밀도와 루프 안정성 간에 적절한 균형을 유지하려면 적절한 값으로 설정해야 합니다.

DLT가 없는 기존의 전압 조정기에서 출력 노드의 극은 부하 전류가 유도된 전력 트랜지스터 트랜스컨덕턴스 변동으로 인해 다른 주파수에 있게 됩니다. 부하 전류가 증가함에 따라 파워 트랜지스터 g의 트랜스컨덕턴스 m _DN1 그림 6a와 같이 다른 영점과 극점은 동일한 위치를 유지하면서 출력 극점은 고주파수 쪽으로 이동합니다. 이것은 시스템의 주파수 보상을 더 어렵게 만들고 경부하 조건에서 과도 응답을 늦출 수 있습니다. 더 심각하게는 시스템이 불안정할 수 있습니다.

<그림>

전압 조정기의 주파수 응답. 아 동적 부하 기술이 없는 전압 조정기. ㄴ 동적 부하 기술을 사용하는 제안된 전압 조정기

제안된 DLT의 도움으로 제시된 VR은 다양한 부하에서 더 나은 안정성을 갖습니다. 앞서 분석한 바와 같이 동적 부하 회로를 통한 전류는 정상 상태에서 부하 전류가 증가함에 따라 감소하고 그 반대의 경우도 마찬가지입니다. 이 전류는 DN1에 의해 제공되기 때문에 더 넓은 부하 전류 범위 내에서 DN1의 트랜스컨덕턴스 변동을 억제할 수 있으며, 이는 제안된 DLT를 사용하여 더 넓은 부하 범위 동안 시스템 안정성과 대역폭 불변성에 도움이 된다. 제안한 VR의 주파수 응답은 그림 6b와 같으며, 이는 빠른 과도 응답으로 안정성을 보장할 수 있다.

출력 커패시터는 0 ω의 위치를 설정합니다. z2 . 영점을 합리적으로 배치함으로써 시스템은 다양한 C 밖 .

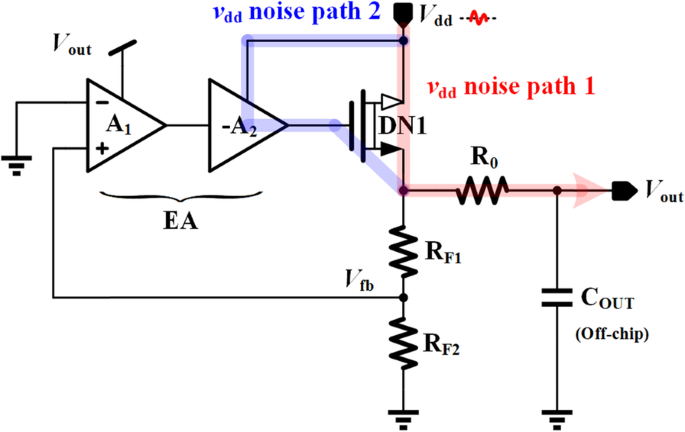

PSR은 전압 조정기의 성능을 측정하는 중요한 매개변수 중 하나로 공급 전압에서 발생하는 고주파 리플 및 노이즈에 대한 제거 능력을 나타냅니다. 이 섹션에서는 Gupta 12에서 제안한 PSR 분석 방법을 채택했으며, 이 방법의 주요 아이디어는 전체 레귤레이터 시스템을 전압 분배기 모델로 단순화하는 것입니다. 그림 7과 같이 V에서 오는 두 개의 노이즈 경로가 있습니다. dd V에게 밖 :경로 1은 전력 트랜지스터 DN1의 드레인에서 V로 노이즈를 직접 전달합니다. 밖; 경로 2는 EA의 두 번째 단계에서 전력 트랜지스터 DN1의 게이트까지입니다. 경로 2의 효과는 다음과 같이 표현될 수 있습니다.

$$ {A}_{\mathrm{경로}2}\대략 \frac{r_{o\_M7}}{g_{m\_\mathrm{HV}10}{r}_{o\_\mathrm{ HV}10}{r}_{o\_M10}} $$ (15) <그림>

제안된 VR의 PSR 분석

(15)와 같이 A 경로2 제안된 SPT 및 캐스코드 전류 미러 구조의 도움으로 매우 작습니다. 이는 PSR 분석에서 경로 1의 영향을 지배적으로 만듭니다.

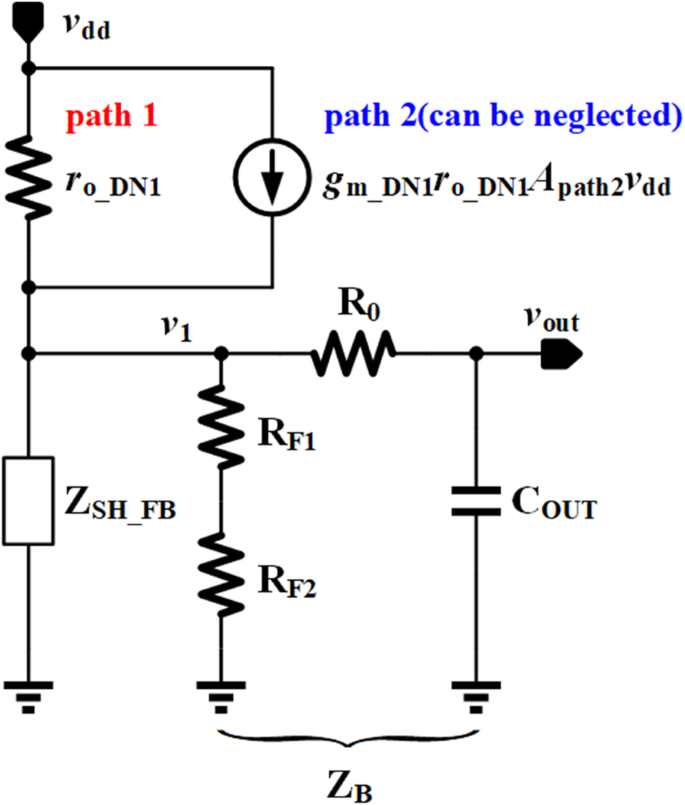

제안된 VR의 단순화된 PSR 모델은 그림 8과 같다. 여기서 r o_DN1 노이즈 경로 1을 설명하는 전력 트랜지스터 DN1의 출력 저항이고, 제어된 전류 소스는 노이즈 경로 2, Z에서 발생합니다. 나 R로 구성 F1 , R F2 , R 0 , 및 C 밖 고주파에서 필터 역할을 하고 Z SH_FB 네거티브 피드백 루프의 기능을 포함하는 등가 임피던스입니다. Z SH_FB 제공할 수 있습니다.

$$ {Z}_{SH\_ FB}=\frac{1}{g_{m\_ DN1}\left(1+\beta {A}_E\right)} $$ (16) <그림><소스 유형="이미지/webp" srcset="//media.springerature.com/lw685/springer-static/image/art%3A10.1186%2Fs11671-019-3215-4/MediaObjects/11671_2019_3215_Fig8_HTML.png? ">

PSR의 단순화된 모델

여기서 g m_DN1 전력 트랜지스터 DN1의 트랜스컨덕턴스입니다. 따라서 PSR 전달 함수는 다음과 같이 표현될 수 있습니다.

$$ \mathrm{PSR}=\frac{V_{\mathrm{out}}}{V_{\mathrm{dd}}}=\frac{\left(1+{g}_{m\_\mathrm{ DN}1}{r}_{o\_\mathrm{DN}1}{A}_{\mathrm{경로}2}\right)\left({Z}_B\Big\Vert {Z}_{ \mathrm{SH}\_\mathrm{FB}}\right)}{r_{o\_\mathrm{DN}1}+{Z}_B\Big\Vert {Z}_{\mathrm{SH}\ __\mathrm{FB}}} $$ (17)의도적으로 HV10의 고유 이득을 전력 트랜지스터 DN1보다 훨씬 크게 설정하여 g m_DN1 r o_DN1 A 경로2 <<1을 달성할 수 있으므로 제어된 전류 소스를 무시할 수 있습니다. PSR의 표현은 다음과 같이 더 단순화될 수 있습니다.

$$ \mathrm{PSR}\approx \frac{Z_B\Big\Vert {Z}_{\mathrm{SH}\_\mathrm{FB}}}{r_{o\_\mathrm{DN}1}+ {Z}_B\Big\Vert {Z}_{\mathrm{SH}\_\mathrm{FB}}} $$ (18)Z 이후로 나 및 Z SH_FB 주파수 변화에 따라 달라지므로 PSR의 주파수 특성 분석이 필요합니다.

저주파에서 EA의 이득은 매우 높고 C 밖 개방회로로 취급할 수 있다. 따라서 Z 나>> Z SH_FB PSR은 다음과 같이 쓸 수 있습니다.

$$ {\mathrm{PSR}}_{\mathrm{LF}}\approx \frac{1}{g_{m\_\mathrm{DN}1}{r}_{o\_\mathrm{DN} 1}\left(1+\beta{A}_{E0}\right)} $$ (19)Z의 임피던스 SH_FB 루프 이득이 중간 주파수에서 감소하기 때문에 증가할 것입니다. 이 단계에서 Z SH_FB 여전히 작고 PSR은 주로 루프 게인의 영향을 받습니다. (7)과 관련하여 PSR은 다음과 같이 표현될 수 있습니다.

$$ {\mathrm{PSR}}_{\mathrm{MF}}\approx \frac{1}{g_{m\_\mathrm{DN}1}{r}_{o\_\mathrm{DN} 1}\left(1+\beta{A}_{E0}\right)}\frac{1+s/{\omega}_p}{1+s/\left[{\omega}_p\left(1 +\베타 {A}_{E0}\right)\right]} $$ (20)(20)과 같이 PSR이 점점 나빠지고, 단위 이득 주파수 내에서 주파수가 증가하면서 출력 전압의 노이즈가 더 심해진다.

주파수 증가로 인해 Z SH_FB 커지고 마침내 1/g에 가까워집니다. m_DN1 . C의 임피던스 밖 작아지지만 여전히 R보다 훨씬 큽니다. 0 . 그래서 R 0 이전과 같이 생략할 수 있습니다. 고주파 PSR은 r 사이의 전압 분할에 따라 달라집니다. o_DN1 및 1/g m_DN1 C와 병행 밖 ,

로 나타낼 수 있습니다. $$ {\mathrm{PSR}}_{\mathrm{HF}}\approx \frac{1}{g_{m\_\mathrm{DN}1}{r}_{o\_\mathrm{DN} 1}}\frac{1}{1+s{C}_{\mathrm{OUT}}/{g}_{m\_\mathrm{DN}1}} $$ (21)고주파에서는 C의 영향으로 출력 전압의 노이즈를 크게 억제할 수 있습니다. 밖 .

앞서 분석한 바와 같이, 제안된 VR의 전체 주파수 범위에서 우수한 노이즈 방지 능력은 세 가지 측면에서 보장됩니다. 첫째, 높은 루프 이득이 채택됩니다. 둘째, SPT는 전원 공급 장치 노이즈가 전원 트랜지스터의 게이트에 거의 영향을 미치지 않도록 합니다. 셋째, 출력 커패시터 C 밖 필터링 특성으로 고주파에서 PSR을 향상시킬 수 있습니다.

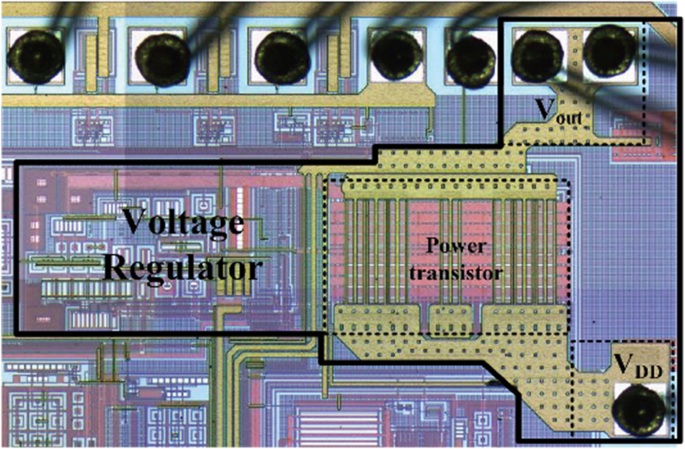

제안된 VR은 표준 0.35μm BCD 기술로 구현되었습니다. 제작된 레귤레이터의 칩 사진은 그림 9와 같으며 VR의 활성 코어 면적은 290 μm × 900 μm이다.

<그림>

제안된 VR의 칩 사진

제안된 VR의 조정된 출력 전압은 5 V이고 전원 전압 범위는 5.5~30 V이며, 출력 커패시터는 저가형 세라믹 커패시터이다. 출력 커패시터의 커패시턴스는 100 nF ~ 3.3 μF 범위에서 설정할 수 있습니다.

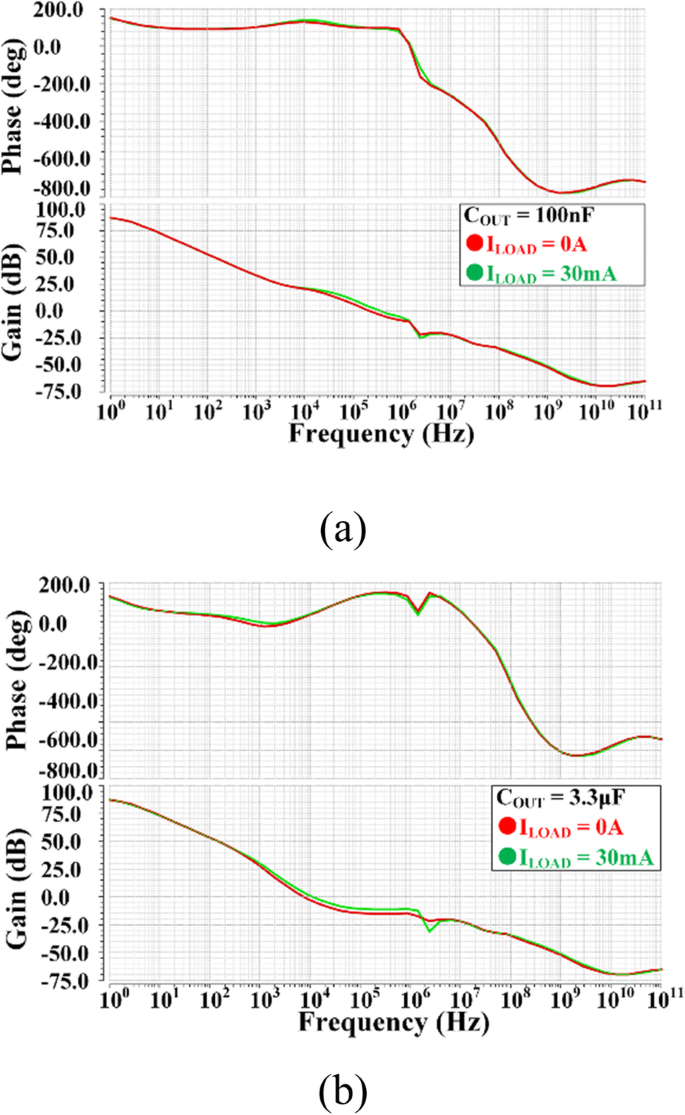

그림 10은 100 nF 및 3.3 μF 출력 커패시터를 사용하여 다양한 부하 조건에서 제안된 VR의 주파수 응답을 보여줍니다. 제안된 LDO는 광범위한 출력 커패시터 값에서 안정적으로 유지할 수 있으며 루프 주파수 응답 파형은 0~30 mA 부하 전류의 차이가 매우 작아 앞서 분석한 제안 DLT의 이점이 있습니다.

<그림>

I의 다른 값에서 제안된 VR의 루프 주파수 응답 로드 및 C 밖 정황. 아 COUT =100 nF, b COUT =3.3 ㅍF. 빨간색과 녹색 선은 I를 나타냅니다. 로드 각각 0 A 및 30 mA

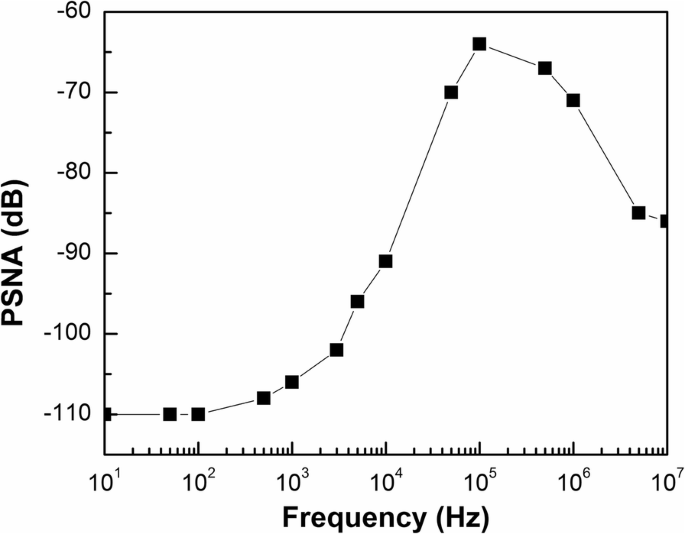

0.1 μF 출력 커패시터를 사용한 PSR 검증 결과는 그림 11에 나와 있으며, 여기에서 저주파에서는 -110 dB, 10 MHz까지는 -64 dB보다 우수합니다. 낮은 주파수에서 제안하는 VR은 높은 루프 이득으로 인해 좋은 PSR을 갖는다. PSR은 극점 ω이 지배하기 때문에 단위 이득 주파수 내에서 열악해집니다. p . 출력 커패시터 C 밖 고주파에서 PSR 특성을 향상시킵니다. 이러한 결과는 이전 분석과 일치하며 제안된 VR이 전체 주파수 범위에서 더 나은 PSR을 얻음을 보여줍니다.

<그림>

제안된 VR의 PSR

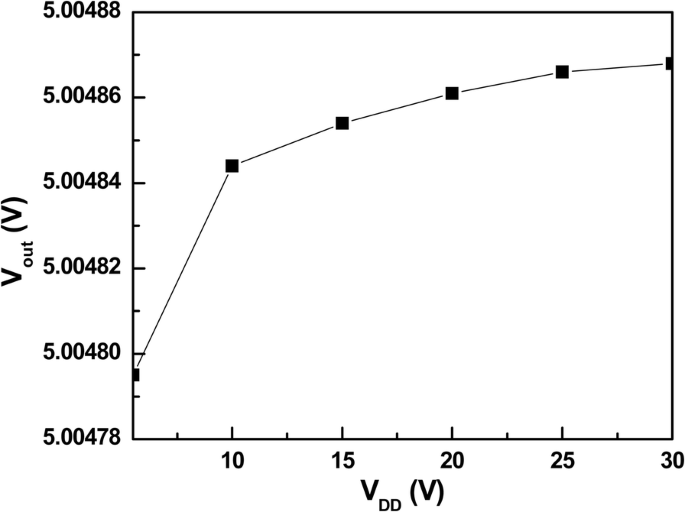

제안한 VR의 라인 레귤레이션 결과는 그림 12와 같다. 5.5 ~ 30 V의 입력 전압 범위에서 출력 전압은 73.53 μV만 변하므로 라인 레귤레이션은 2.98 μV/V에 불과하다. 이것은 제안된 SPT의 효과를 확인시켜줍니다.

<그림>

제안된 VR의 라인 규제

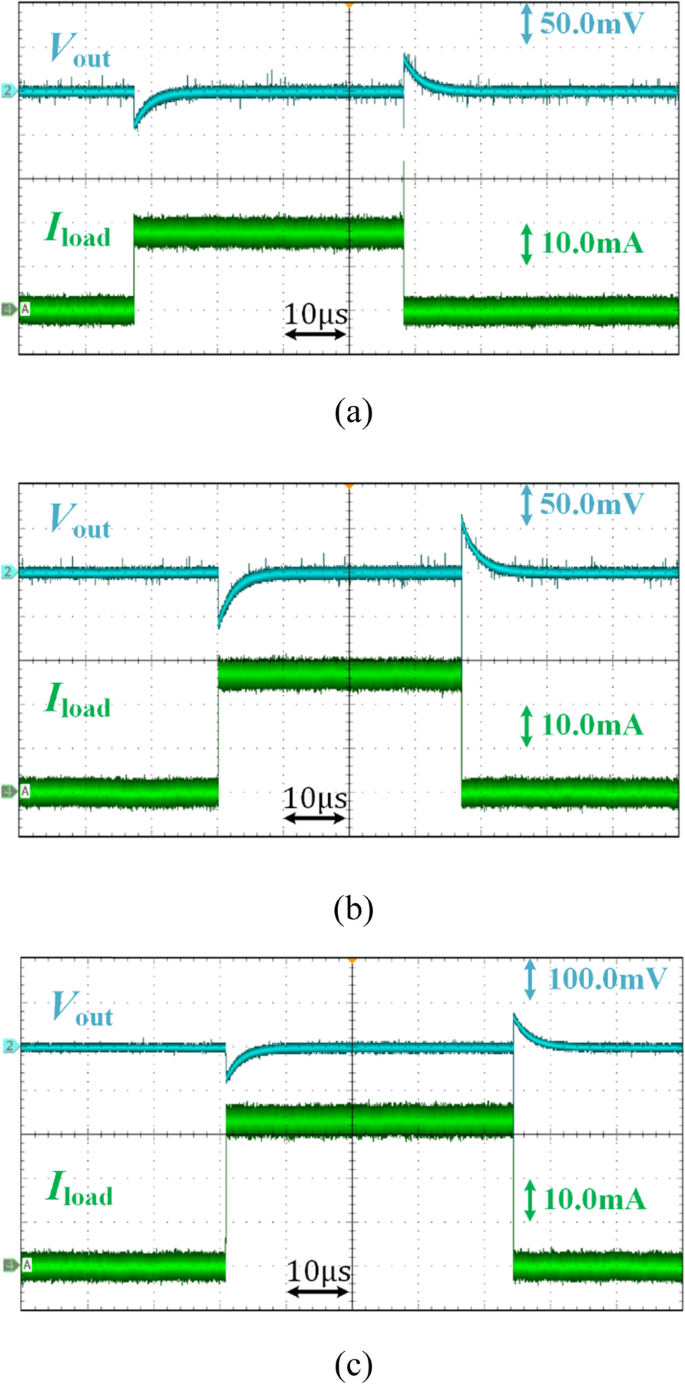

그림 13은 다른 부하 전류로 인한 출력 전압의 과도 응답을 보여줍니다. 부하 전류가 0에서 18 mA, 28 mA 및 32 mA로 변경될 때 조정된 출력 전압의 전압 스파이크 및 딥은 각각 약 43 mV, 65 mV, 83 mV입니다. 그 결과 주로 R에 의해 발생하는 0.233 mV/mA의 부하 조절이 발생합니다. 0 다양한 출력 커패시턴스로 안정성을 제공합니다.

<그림>

부하 전류 단계가 다르기 때문에 제안된 VR의 과도 응답 파형. 아 0 ~ 18 mA; ㄴ 0 ~ 28 mA; ㄷ 0 ~ 32 mA

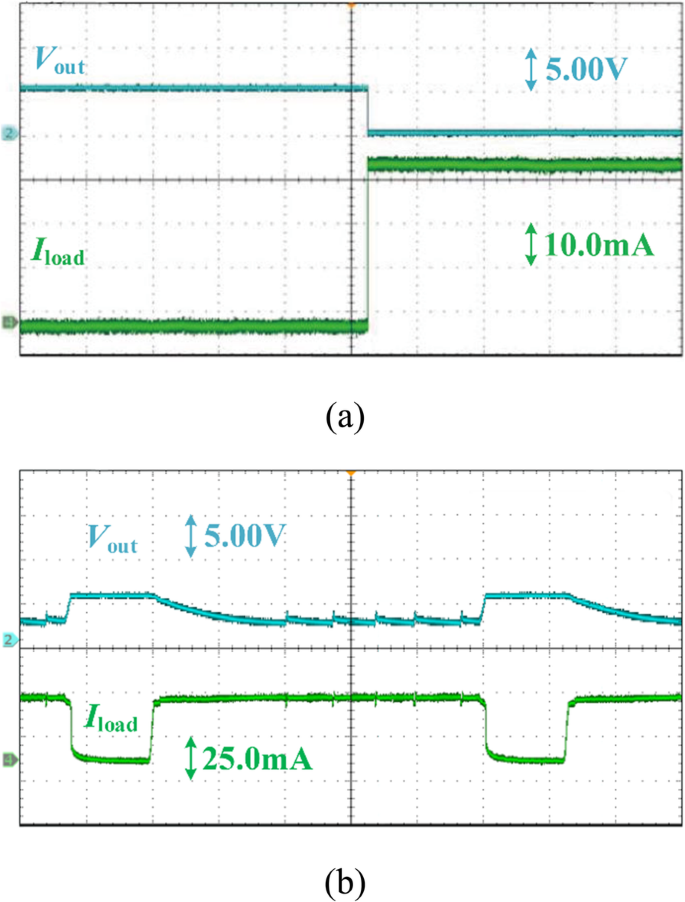

측정된 OCP를 Fig. 14에 나타내었다. OCP의 유효성을 검증하기 위해 Fig. 14a에서 short-circuit을 적용하였다. 그림 14a와 같이 출력 전압을 접지로 끌어올려 과전류가 발생하면 제안된 VR의 출력 전류는 약 40 mA로 유지된다. 그림 14b는 과전류와 정상 부하 사이의 과도 응답을 보여주며, 이는 제안된 VR이 과부하 종료 시 자체 복구 기능이 있음을 나타냅니다.

<그림>

제안된 VR의 OCP 측정. 아 출력 단락; ㄴ 과전류와 정상 부하 사이의 과도

표 1은 제안된 LDO와 이전에 발표된 일부 다른 LDO의 성능 비교를 제공합니다. 이에 비해 이 LDO는 제안된 SPT의 이점을 얻을 수 있는 최상의 회선 조절 및 PSR을 가지고 있습니다. 보다 진보된 공정으로 제작하면 활성 영역이 더 줄어들 것입니다.

표 2는 전원 공급 장치 범위가 넓은 LDO에 초점을 맞춘 또 다른 성능 비교를 제공합니다. 제안된 DLT 및 SPT의 도움으로 이 작업은 다른 LDO에 비해 최고의 라인 레귤레이션과 가장 넓은 전원 공급 범위를 갖습니다. 추가적인 OCP 기능은 이 작업을 보다 경쟁력 있고 안정적으로 만듭니다.

DLT 및 OCP가 포함된 높은 안정성 SPT VR은 표준 0.35μm BCD 프로세스에서 구현됩니다. SPT의 도움으로 대부분의 레귤레이션 루프는 레귤레이트된 출력 전압에 의해 공급되므로 안정성과 PSR 개선에 도움이 됩니다. 제안된 DLT는 과도 응답과 안정성에 도움이 됩니다. 또한 내장된 OCP 회로는 제시된 VR이 과부하 또는 단락으로 인한 손상을 방지할 수 있습니다. The linear regulation of the proposed VR is 2.98 μV/V with VDD from 5.5 to 30 V while the regulated output voltage is 5 V, and the load regulation is 0.233 mV/mA with load current from 0 A to 30 mA. The overshoot and undershoot voltage during load current changing is also small by using the presented transient enhancement circuit. The PSR at low frequency is − 110 dB, and is better than − 64 dB up to 10 MHz. High loop stability can be achieved in a wide range of output capacitor and load current, and thus the proposed VR is suitable for applications that require high performance and reliability under variations of output capacitor and load current.

All data generated or analysed during this study are included in this published article.

Voltage regulator

Overcurrent protection

Self-power technique

Power supply rejection

Dynamic load technique

Error amplifier

나노물질

전류 조절기는 휴대폰을 충전하거나, 자동차에 시동을 걸거나, 컴퓨터를 꽂거나, 작은 전기 제품을 켤 때마다 작동합니다. 전압 조정기라고도 하는 전류 조정기는 전기 장치가 작동하는 데 필요한 수준으로 전기량을 줄이고 제한합니다. 미국(미국)의 표준 주택 전류는 110볼트이며, 이는 영국 및 대부분의 유럽 국가에서 240볼트입니다. 그러나 많은 전기 장치는 들어오는 전압의 일부만 필요로 합니다. 여기에서 전류 조정기가 작동합니다. 일반적으로 전류 조정기는 정해진 양의 전류만 장치에 통과할 수 있도록 하는 강압 변압기의 한 형태입니다.

생산성은 사람들이 산업용 로봇을 생산 라인에 통합하는 이점에 대해 이야기할 때 사용하는 주요 단어 중 하나입니다. 로봇은 애플리케이션의 생산성을 높이는 데 도움이 될 뿐만 아니라 생산 과정에서 로봇과 상호 작용하고 주변에서 일하는 인간 작업자의 생산성도 높이는 데 도움이 됩니다. 로봇은 어떻게 인간 작업자의 생산성을 향상합니까? 간단합니다. 로봇이 생산 라인에 통합되면 인간 작업자는 지루하고 지루하며 위험한 작업을 경감하고 더 많은 작업 기술과 더 많은 책임을 부여하는 작업에 더 잘 활용되어 사기를 높이고 생산성을 높일 수 있습니