소개

셀룰러 표준과 같은 무선 통신 애플리케이션의 수요 증가에 따라 ADC(아날로그-디지털 변환기)는 더 높은 신호 대역폭(BW) 및 동적 범위(DR)를 지원하도록 빠르게 발전하고 있습니다. LTE-A(Long-Term-Evolution Advanced) 통신 표준에서 BW의 요구 사항은 100MHz로 높아졌습니다. Nyquist ADC, 일반적으로 파이프라인 ADC[1, 2]는 높은 BW를 위해 매크로 기지국에서 사용되었습니다. 그러나 열잡음이 제한된 스위치 입력 커패시터와 앤티 앨리어싱 필터를 구동하기 위한 필수 입력 버퍼는 상당한 전력 소비와 설계 복잡성을 유발합니다. 또한 파이프라인 ADC가 고이득 광대역 잔류 증폭기 및 교정 기술을 결정하는 정확한 단계 간 이득에 의존한다는 사실은 복잡성과 전력 손실을 초래합니다. Δ Σ ADC는 오버샘플링 및 잡음 형성 기술을 사용하는 고성능 및 전력 효율성으로 유명합니다. 그러나 일반적으로 16[3-6]을 초과하는 오버샘플링 비율(OSR)의 요구 사항은 GHz를 초과하는 샘플링 주파수를 결정합니다. 최근 Δ Σ 50MHz BW를 초과하는 ADC는 다중 GHz 클록 속도를 허용하는 나노스케일 CMOS 프로세스를 사용하여 제안되었습니다. 이전에는 고주파수 Δ Σ ADC는 일반적으로 이산 시간(DT) 구현 대신 연속 시간(CT) 구현[3-9]을 채택합니다. 후자는 스위치드 커패시터 회로에 의해 구현되며 그 정확도는 커패시터 매칭에 의존합니다. 즉, 프로세스 변동에서 강력한 작동이 제공됩니다. 또한 커패시터와 스위치의 시상수가 충분히 작기 때문에 클록 지터에 대한 내성이 우수하다. 그러나 변조기 이전에 샘플링 작업을 수행하므로 앤티앨리어싱 필터가 필요합니다. 반면에 스테이지의 안정성을 보장하기 위한 안정화 요구 사항으로 인해 DT 변조기의 연산 증폭기는 CT 변조기보다 더 넓은 단위 이득 대역폭(UGBW)으로 구현됩니다. 요약하면, DT 변조기는 높은 정확도를 제공하지만 좁은 신호[10, 11]를 제공할 수 있으며 스마트 센서 및 생물 의학 이미징과 같은 측정 응용 프로그램을 구현하는 데 널리 사용됩니다. 대조적으로, 비슷한 복잡성과 전력 소비를 가진 DT 변조기보다 고주파수 애플리케이션을 위한 CT 변조기를 설계하려는 노력이 더 광범위했습니다.

주어진 프로세스에서 더 높은 BW에 대한 까다로운 설계 목표는 프로세스 제한적인 클록 속도 때문에 더 낮은 OSR을 결정합니다. 충분한 DR을 달성하기 위해서는 기존에 루프 필터 캐스케이드(loop filter cascade)에 의해 수행되고 이전 작업에서는 일반적으로 3보다 크거나 같은 높은 잡음 전달 함수 차수에 의해 구현된 공격적인 잡음 성형이 필요하다. 그러나 루프 필터 차수가 증가하면 전력 소비, 불안정성 및 설계 복잡성이 발생합니다. 계단식 저차 로컬 Δ에 의해 구현된 다단계 잡음 형성(MASH) 아키텍처[6, 8] Σ 서로 피드백 경로가 없는 변조기는 안정성 문제를 완화하기 위해 사용되었지만 민감도가 일치하지 않습니다. 게다가, 다중 비트 양자화기가 있는 변조기는 비교기 양이 기하급수적으로 증가하면서 조건부로 높은 DR을 얻습니다.

이 문서에서는 40nm CMOS 프로세스를 사용하여 69.7mW 소비로 100MHz BW에서 80DR을 달성하는 40nm CMOS의 CT 변조기에 대해 설명합니다. 이 논문은 다음과 같이 구성되어 있습니다. "방법" 섹션에서는 변조기 토폴로지 및 회로 구현에 대해 설명합니다. "결과 및 토론" 섹션은 시뮬레이션 결과를 보여주고 "결론" 섹션은 이 작업에 대한 요약을 제공합니다.

<섹션 데이터-제목="방법"> 메소드

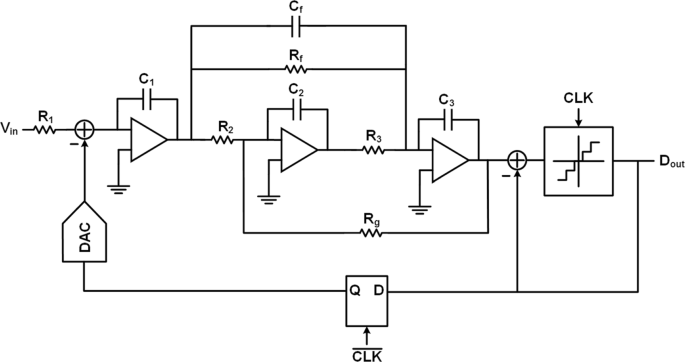

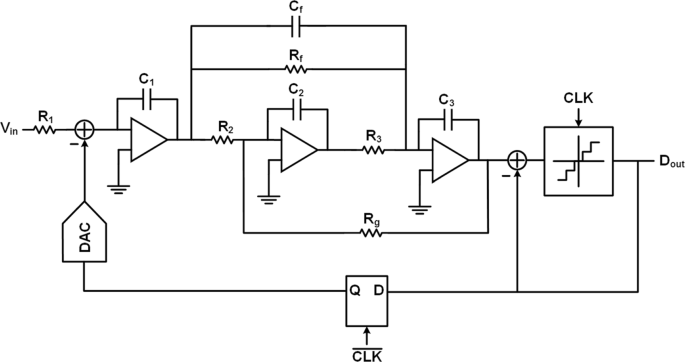

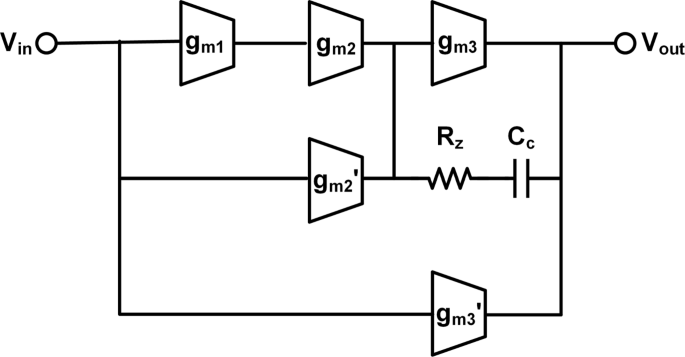

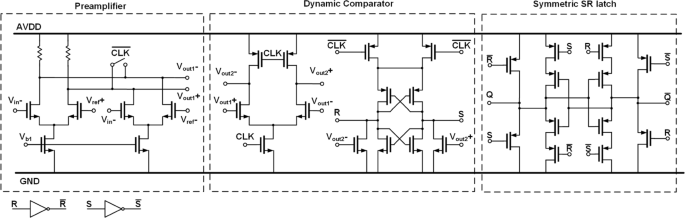

그림 1은 제안된 3차 CT Δ의 전체 개략도를 보여줍니다. Σ 단순화를 위한 단일 종단 구조의 변조기. 3차 노이즈 쉐이핑은 DR과 루프 안정성 사이에서 큰 절충안을 얻습니다. 제안하는 변조기는 12 OSR에서 2.4GHz의 샘플링 속도를 갖는다. Δ에서 상대적으로 높은 OSR Σ 100MHz BW를 초과하는 변조기는 높은 DR을 보장합니다. 변조기는 3개의 RC 적분기, 4비트 양자화기 및 4비트 전류 조정 DAC를 포함합니다. 적분기는 높은 에너지 효율성을 위해 혁신적인 저전력 소산 피드포워드 증폭기로 구현됩니다. 피드백 DAC에는 양자화기의 준안정성 요구 사항을 완화하기 위해 절반의 샘플링 기간 지속 시간 추가 지연이 있습니다. 수동 가산기에 의해 구현되고 양자화기에 의해 직접 구동되는 빠른 피드백 경로는 초과 루프 지연(ELD) 보상을 실현합니다. 대역 외 신호 전송 기능을 희생시키면서 전력 효율성을 위해 피드포워드 토폴로지가 사용됩니다.

<그림><그림><소스 유형="이미지/webp" srcset="//media.springerature.com/lw685/springer-static/image/art%3A10.1186%2Fs11671-020-3284-4/MediaObjects/ 11671_2020_3284_Fig1_HTML.png?as=webp">

제안된 단일 루프 3차 4비트 CT Δ의 전체 개략도 Σ 피드포워드 토폴로지가 있는 변조기

앰프 디자인

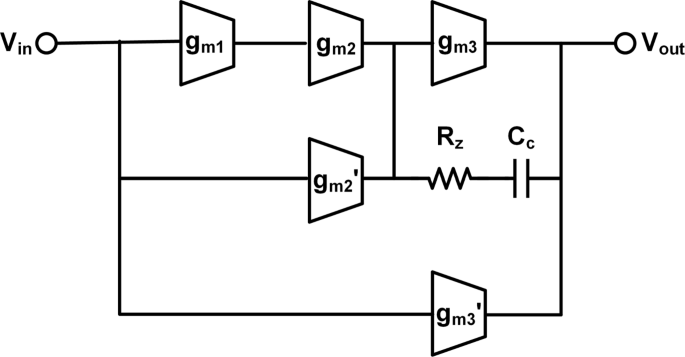

Δ에는 높은 증폭기 이득이 필요합니다. Σ 원하는 노이즈 변환 기능을 보장하는 변조기. 그러나 다중 GHz 클록 속도를 달성하는 데 사용되는 나노스케일 기술은 고유 이득이 낮습니다. 따라서 그림 2와 같이 3단 증폭기를 사용하여 충분한 DC 이득을 구현합니다. Feedforward 토폴로지와 Miller 보상을 결합하여 단위 이득 대역폭 감소 없이 위상 마진을 개선합니다. 피드포워드 증폭기는 적절한 UGBW 및 위상 마진(PM)으로 높은 이득을 달성하는 인기 있는 솔루션 중 하나였습니다. 피드포워드 경로로 인한 왼쪽 절반 평면 영점은 극의 음의 위상 편이를 효과적으로 취소해야 합니다. 이는 피드포워드 경로에서 증폭기의 높은 트랜스컨덕턴스를 요구하고 상당한 전력을 소비합니다. 바이어스 전류를 재사용하는 유리한 방식은 전력을 절약하는 반면 g m 가치. 불충분한 g m 일반적으로 UGBW 이상으로 0이 발생하고 적절한 위상 마진을 제공할 수 없습니다. 전체 UGBW 아래에 최적화된 영점은 Miller 보상 커패시터와 널링 저항을 추가하여 제공됩니다.

<그림><그림><소스 유형="이미지/webp" srcset="//media.springerature.com/lw685/springer-static/image/art%3A10.1186%2Fs11671-020-3284-4/MediaObjects/ 11671_2020_3284_Fig2_HTML.png?as=webp">

Miller 보상이 있는 제안된 3단계 피드포워드 증폭기의 토폴로지

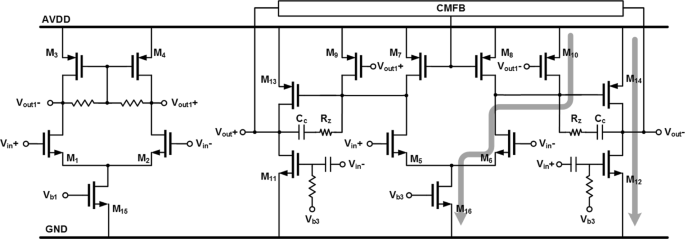

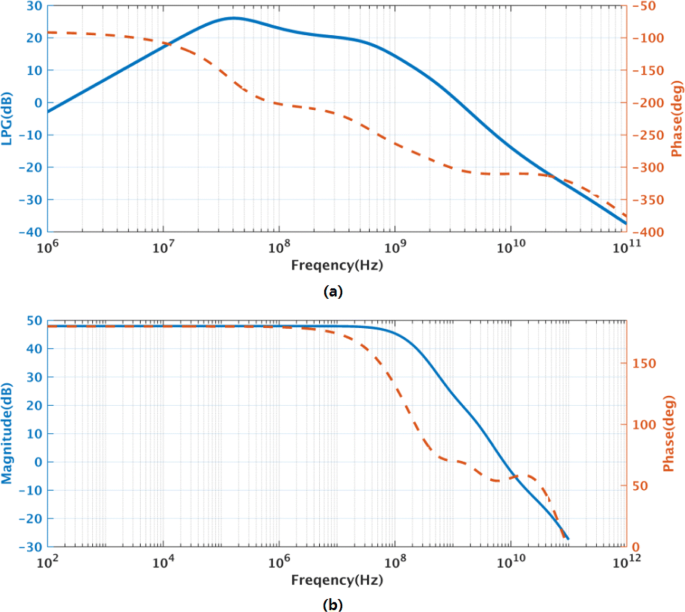

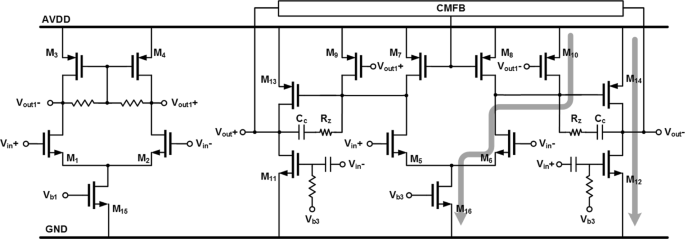

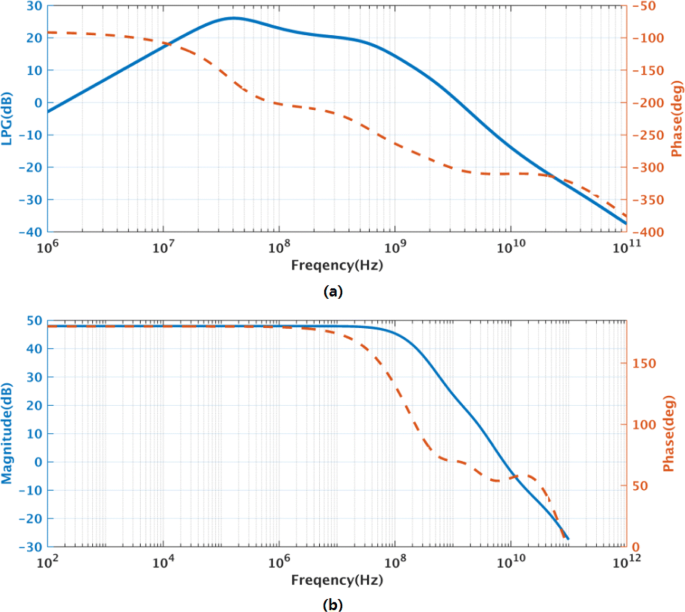

그림 3은 첫 번째 적분기에 사용된 증폭기의 트랜지스터 수준 회로도를 보여줍니다. 트랜지스터 M 1−4 증폭기의 입력단을 형성하고 트랜지스터 M 9,10 그리고 M 13,14 각각 두 번째와 세 번째 단계를 형성합니다. 트랜지스터 M 5−8 그리고 M 11,12 2단계 및 3단계 증폭기와 바이어스 전류를 공유하면서 입력과 출력 사이에 2개의 고속 피드포워드 경로를 생성합니다. 1단계 출력 공통 모드(CM)는 로컬로 고정됩니다. 2단계 및 3단계 출력 CM은 CMFB 증폭기 M에 걸친 2단계 피드백 경로에 의해 고정됩니다. 7,8 그리고 M 13,14 . 그림 4a는 모든 부하가 있는 첫 번째 적분기 증폭기의 시뮬레이션된 레이아웃 후 개루프 응답을 보여주고 그림 4b는 폐루프 응답을 보여줍니다. 첫 번째 통합자는 3.6GHz의 UGBW 및 57.8GHz를 달성했습니다.

∘

1.2V 전원에서 10.5mW를 소비하는 동안 모든 부하 효과가 있는 PM의. 두 번째 및 세 번째 적분기는 동일한 토폴로지를 채택하지만 확장된 바이어스 전류를 사용하여 4.7 및 3.3GHz의 UGBW와 58.0 및 57.8의 PM을 달성합니다.

∘

각각 4.3mW 및 17.3mW를 소비하면서

<그림><그림><소스 유형="이미지/webp" srcset="//media.springerature.com/lw685/springer-static/image/art%3A10.1186%2Fs11671-020-3284-4/MediaObjects/ 11671_2020_3284_Fig3_HTML.png?as=webp">

증폭기 트랜지스터 레벨 회로도

<그림><그림><소스 유형="이미지/webp" srcset="//media.springerature.com/lw685/springer-static/image/art%3A10.1186%2Fs11671-020-3284-4/MediaObjects/ 11671_2020_3284_Fig4_HTML.png?as=webp">

첫 번째 적분기에서 증폭기의 레이아웃 후 시뮬레이션 결과. 아 개방 루프 AC 응답; ㄴ 폐쇄 루프 AC 응답

양자화기 및 DAC

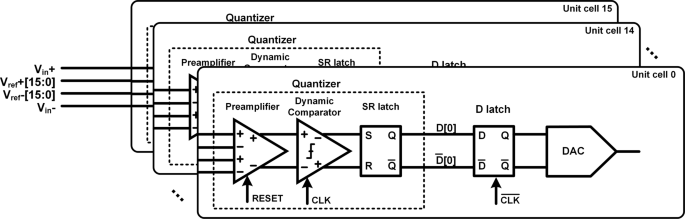

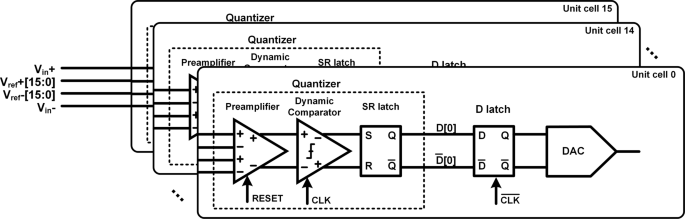

도 5에 도시된 양자화기와 DAC의 개략도와 같이, 각각은 16개의 단위 셀로 구성된다. 양자화기는 17탭 저항 래더에서 생성된 16레벨 인코더가 있는 4비트 플래시 ADC로 실현됩니다. ELD에서 루프 안정성을 보장하기 위해 샘플링 주기의 절반 미만으로 작동 기간을 요구하는 양자화기는 최대 BW의 제한으로서 핵심 블록입니다.

<그림><그림><소스 유형="이미지/webp" srcset="//media.springerature.com/lw685/springer-static/image/art%3A10.1186%2Fs11671-020-3284-4/MediaObjects/ 11671_2020_3284_Fig5_HTML.png?as=webp">

양자화기 및 DAC의 단순화된 회로도

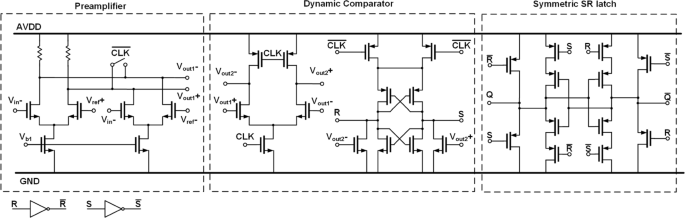

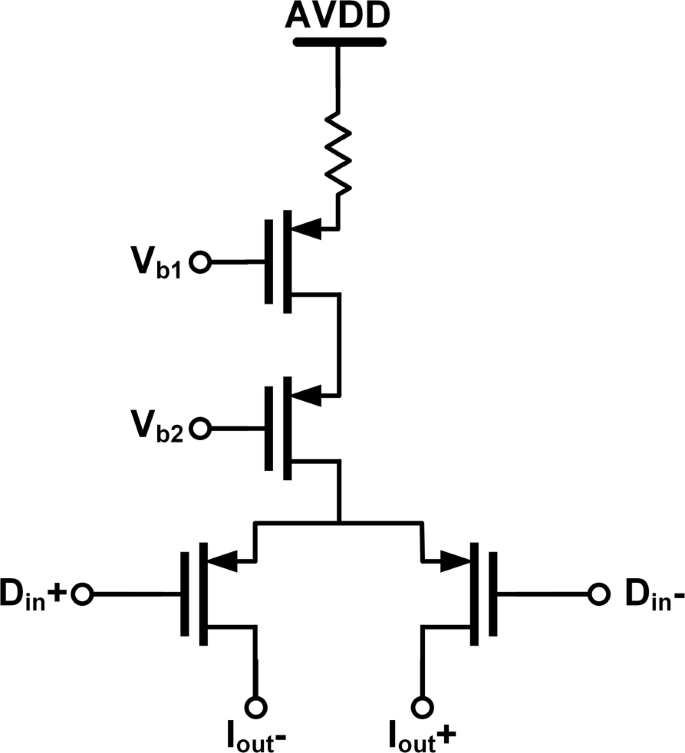

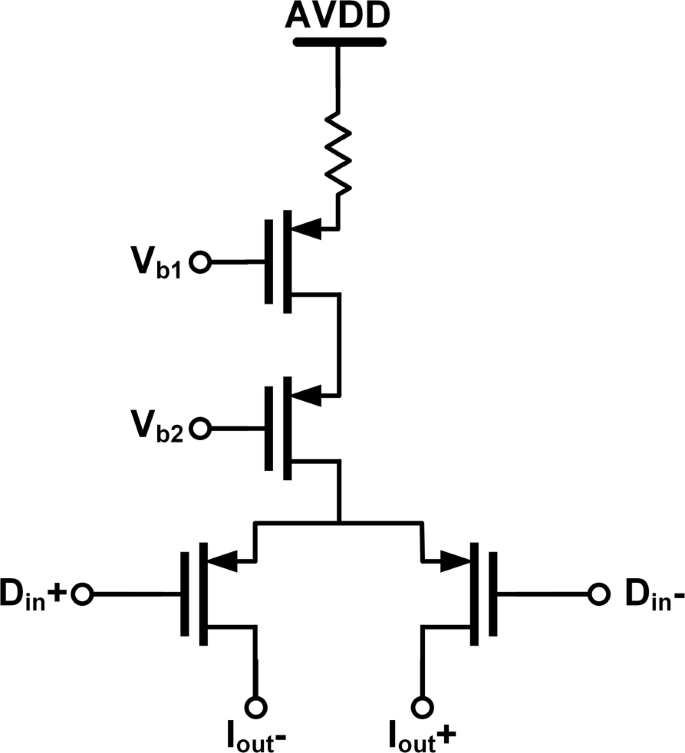

고속 플래시 ADC를 구현하기 위해 그림 6과 같이 전치 증폭기 단, 동적 비교기 단, 대칭 SR(Set-and-Reset) 래치[12]로 구성된 3단 비교기 아키텍처가 사용됩니다. 입력 참조 오프셋 감소를 위한 전치 증폭기는 빠른 복구를 가능하게 하기 위해 출력에 연결되는 리셋 스위치가 있는 2개의 저항 부하 차동 쌍입니다. 기존의 동적 비교기와 달리 차동 쌍 및 교차 결합 인버터는 저전압 전원을 위한 모든 전류 경로에서 트랜지스터의 양을 최소화하기 위해 두 부분으로 분할됩니다. 클록이 하이 레벨로 바뀌면 동적 비교기가 입력에 따라 비교 결정을 내리기 시작합니다. 그런 다음 각 동적 비교기의 두 출력은 클록 리턴이 하이에서 로우로 이동함에 따라 모두 0으로 재설정되어 대칭 SR 래치의 재생성 및 래치를 트리거합니다. 각 브랜치에서 하나의 트랜지스터만 활성화되기 때문에 대칭 SR 래치 구조는 강력한 로딩 구동 능력을 이끕니다. 이것은 상당한 스위치 오프 속도와 낮은 전력 소비로 작은 트랜지스터 크기를 허용합니다. 또한 두 출력 신호의 지연이 동일합니다. DAC 장치 앞의 D 래치는 클록 신호 레벨에 대해 낮은 레벨에 민감하여 절반의 ELD 지속 시간을 보장합니다. 전류 스티어링 DAC 유닛의 트랜지스터 레벨 회로는 그림 7과 같다.

<그림><그림><소스 유형="이미지/webp" srcset="//media.springerature.com/lw685/springer-static/image/art%3A10.1186%2Fs11671-020-3284-4/MediaObjects/ 11671_2020_3284_Fig6_HTML.png?as=webp">

제안하는 양자화기의 한 단위 소자의 트랜지스터 레벨 회로

<그림><그림><소스 유형="이미지/webp" srcset="//media.springerature.com/lw685/springer-static/image/art%3A10.1186%2Fs11671-020-3284-4/MediaObjects/ 11671_2020_3284_Fig7_HTML.png?as=webp">

PMOS 전류 스티어링 DAC 유닛 요소

결과 및 토론

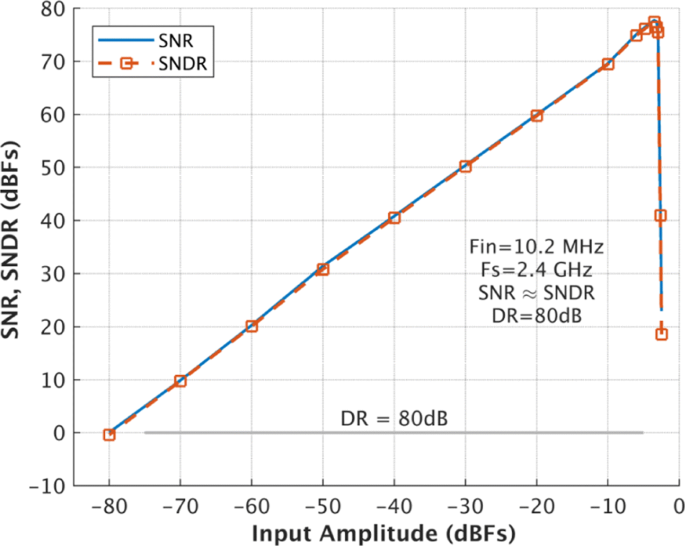

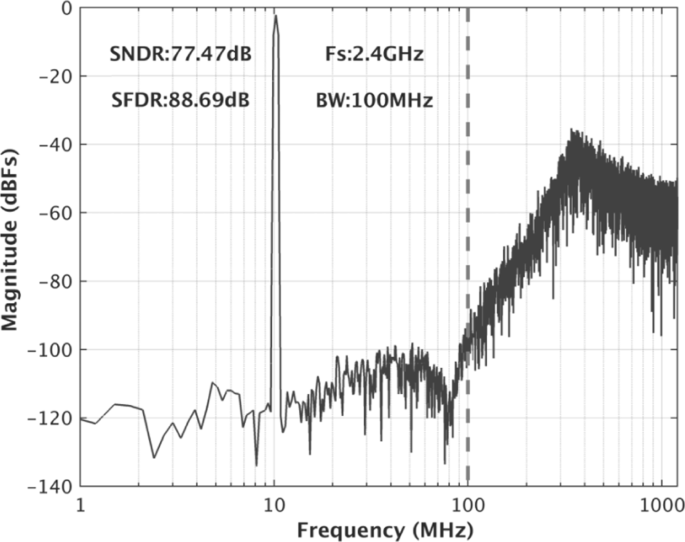

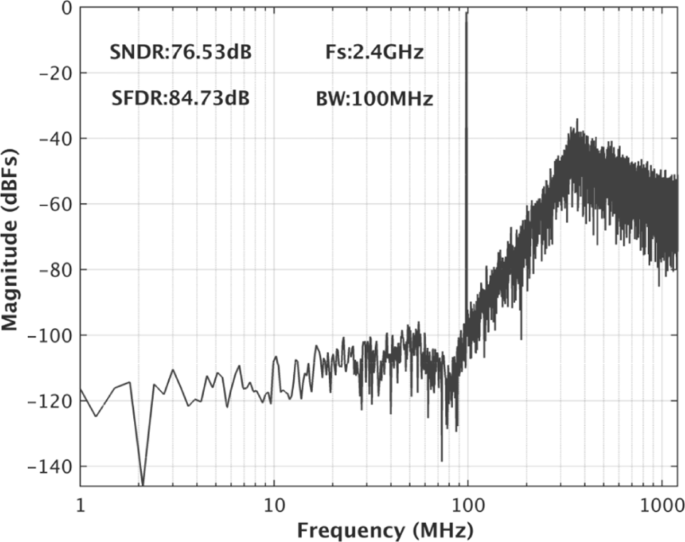

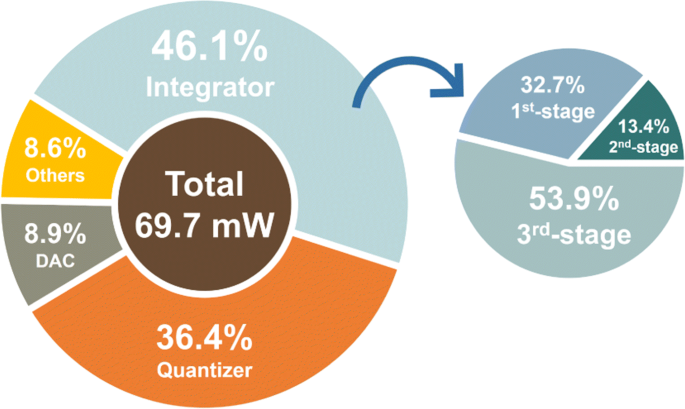

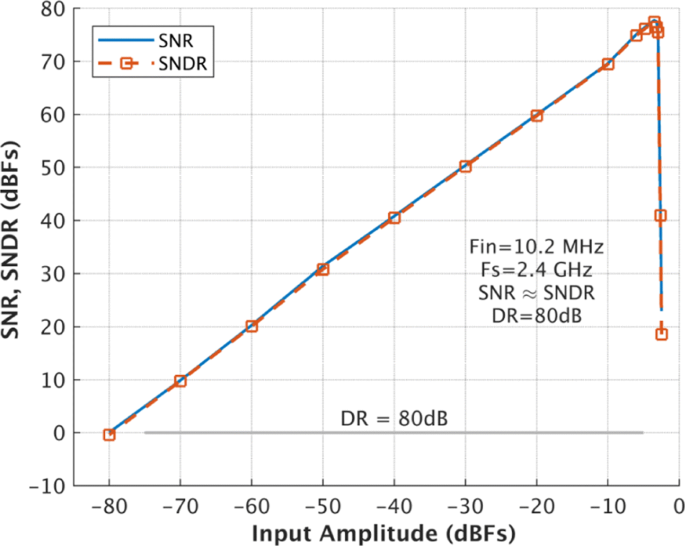

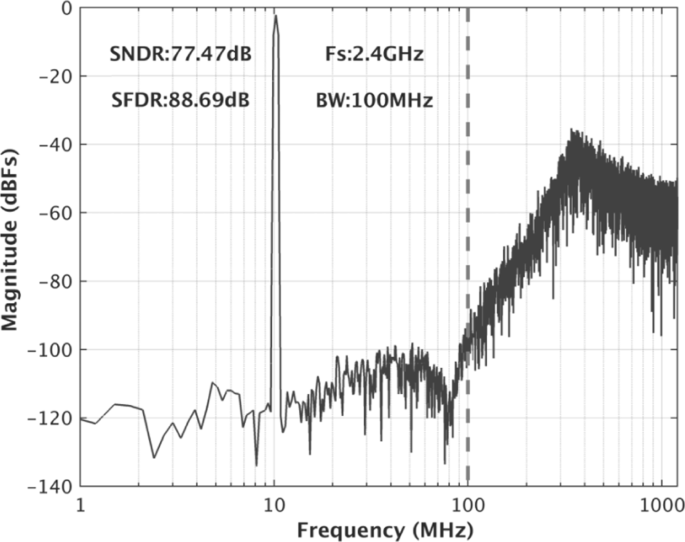

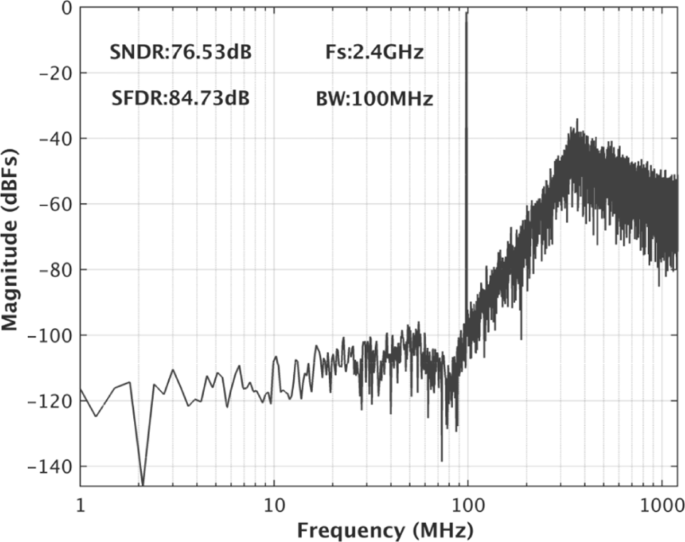

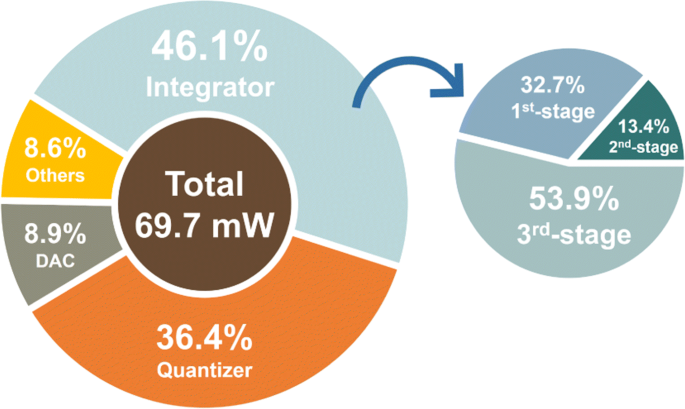

프로토타입 Δ Σ 변조기는 40nm CMOS 공정으로 제작되었습니다. 그림 8과 같이 10.2MHz에서 SNR 및 SDNR 대 입력 진폭의 시뮬레이션 후 결과로 80dB DR이 달성됩니다. 그림 9와 10은 각각 10.2MHz 및 97MHz에서 −3.52dBF 단일 톤 입력으로 시뮬레이션된 스펙트럼을 보여줍니다. 0dBF는 2.4Vpp 변조기 전체 스케일에 해당하기 때문입니다. SNDR은 각각 77.47dB 및 76.53dB입니다. 그림 11과 같이 항복 소모량으로 변조기는 69.7mW의 전력을 소모합니다. 적분기, 양자화기 및 DAC는 각각 32.1mW, 25.4mW 및 6.2mW를 소비합니다. 6.0 mW 전력은 클록 버퍼, 전류 바이어스 및 기준 전압을 포함한 다른 전류에 의해 소비됩니다. 변조기는 DR을 기준으로 171.6dB의 Schreier FOM을 달성합니다. 표 1은 이 작업을 이전에 출판된 여러 작업과 비교합니다. 제안된 변조기는 가장 높은 FOM으로 넓은 BW를 달성합니다.

<그림><그림><소스 유형="이미지/webp" srcset="//media.springerature.com/lw685/springer-static/image/art%3A10.1186%2Fs11671-020-3284-4/MediaObjects/ 11671_2020_3284_Fig8_HTML.png?as=webp">

시뮬레이션 후 SNR 및 SNDR 대 10.2MHz 입력의 입력 신호 진폭

<그림><그림><소스 유형="이미지/webp" srcset="//media.springerature.com/lw685/springer-static/image/art%3A10.1186%2Fs11671-020-3284-4/MediaObjects/ 11671_2020_3284_Fig9_HTML.png?as=webp">

10.2MHz에서 단일 톤 입력으로 사후 시뮬레이션된 스펙트럼

<그림><그림><소스 유형="이미지/webp" srcset="//media.springerature.com/lw685/springer-static/image/art%3A10.1186%2Fs11671-020-3284-4/MediaObjects/ 11671_2020_3284_Fig10_HTML.png?as=webp">

97MHz에서 단일 톤 입력으로 사후 시뮬레이션된 스펙트럼

<그림><그림><소스 유형="이미지/webp" srcset="//media.springerature.com/lw685/springer-static/image/art%3A10.1186%2Fs11671-020-3284-4/MediaObjects/ 11671_2020_3284_Fig11_HTML.png?as=webp">

시뮬레이션 후 전력 소비 분석

<그림> 결론

본 연구에서는 3차 4비트 CT Δ를 제안하였다. Σ 단일 루프 피드포워드 토폴로지가 있는 변조기. 이 변조기는 40nm CMOS 공정으로 설계되었으며 2.4GHz의 클록 속도에서 100MHz BW에 대해 80dB DR을 달성합니다. 저전력 소산 증폭기 구조는 높은 에너지 효율을 이끌어내고 변조기는 1.2V 전원 공급 장치에서 69.7mw를 소비하고 171.6dB의 Schreier FOM을 달성합니다.

데이터 및 자료의 가용성

이 연구 동안 생성되거나 분석된 모든 데이터는 이 출판된 기사에 포함됩니다.

약어

- ADC:

-

아날로그-디지털 변환기

- 흑백:

-

대역폭

- CT:

-

연속 시간

- DR:

-

다이내믹 레인지

- DT:

-

이산 시간

- ELD:

-

초과 루프 지연

- LTE-A:

-

장기 진화 고급

- OSR:

-

오버샘플링 비율

- 오후:

-

위상 마진

- UGBW:

-

단일 이득 대역폭