산업기술

현재 고속직렬전송을 응용한 고성능 컴퓨터 상호접속망의 전송속도는 1차 SDR(Single Data Rate, 2.5Gb/s)에서 4세대인 FDR(Fourteen Data Rate, 14Gb/s)로 발전하고 있다. s), DDR(Double Data Rate, 5Gb/s) 및 QDR(Quad Data Rate, 10Gb/s). 인터넷의 형성에 필수적인 배선 및 스위치 보드 및 인터페이스 카드를 포함하는 PCB(Printed Circuit Board)의 설계는 FDR 고속 및 고주파 분야에 진입했습니다. FDR 신호의 상승 시간이 10ps의 크기로 급격히 감소했기 때문에 신호 무결성과 관련된 일련의 문제는 감쇠, 누화, 반사, 전자기 간섭 등과 같은 기능 구현 및 안정적인 작동 가능성을 결정하는 핵심 기능이 되었습니다. 다중 포트, 다중 채널, 다중 전력 범주 및 높은 에너지 소비를 포함하는 FDR 상호 연결 칩의 특징에 따라 처리율을 높이기 위해 단일 상호 연결 보드에 다중 상호 연결 칩을 항상 통합해야 합니다. 한편으로 공간이 제한된 기판에서는 부품 레이아웃 및 열 발산, 고밀도 라우팅, 기판 후면을 통한 장거리 전송 및 모든 종류의 신호 무결성을 비롯한 몇 가지 요구 사항을 충족해야 합니다. 한편, PCB 설계 기간, PCB 제조 기술의 한계, 비용 관리 등 일부 요소를 고려해야 합니다. 따라서 설계 구현 및 시뮬레이션 검증이 매우 어렵습니다. FDR 상호 연결 및 스위치 보드의 PCB 설계 예를 기반으로이 기사에서는 모든 종류의 신호 무결성 문제를 해결하기 위해 기판 재료 선택, 스택 업 설계, 라우팅 규칙 및 간섭 방지 설계 측면에서 몇 가지 최적화 방법을 제시합니다. FDR 고속 PCB 설계 과정.

FDR 고주파 신호의 경우 전송선 손실은 신호 무결성과 관련된 문제입니다. FDR 신호가 상호 연결 채널을 따라 송신 터미널에서 수신 터미널로 전송될 때 고주파 감쇠가 저주파 감쇠보다 훨씬 크기 때문에 수신 터미널에 도달하는 신호 파형에 심각한 변형이 발생합니다. 변형은 주로 두 가지 측면으로 분류됩니다. 신호의 전압 스윙이 크게 감소한 반면 신호 상승 에지에 나쁜 열화가 발생했습니다. 전자는 신호의 전송 거리를 제한하고 후자는 코드 간의 간섭을 유발합니다. 전송선 손실 A는 도체 손실 Acond의 합으로 간주할 수 있습니다. 및 유전 손실 Adiel 공식 (1)과 같이:A =Adiel + A조건 .

도체 손실은 신호 경로와 반환 경로 사이의 구리 도체에 직렬 저항으로 인해 발생하는 손실을 나타냅니다. 고주파 상황에서 표피 효과는 주변 구리 도체의 표면에 전류를 흐르게 합니다. 구리 도체의 등가 직렬 저항이 증가하면 주파수의 제곱근에 양의 비례하는 주파수가 증가함에 따라 도체 손실이 증가하며, 이는 공식 (2)에 나와 있습니다.  .

.

유전 손실은 기판 재료의 매질에 의해 발생하는 손실을 말하며, 주로 재료의 속성에 의해 결정되고 도체 폭을 포함한 기하학적 구조와 관련이 없으며 주파수에 양의 비례하며 식 (3)에 표시됩니다.  .

.

식 (2)에 기초하여 선폭의 증가는 도체 손실을 감소시킬 수 있다. 그러나 실제 PCB 설계에서는 핀, 보드, 신호 레이어 수 및 임피던스 사이의 간격의 제한으로 인해 도체의 너비가 무한정 넓을 수 없습니다. FDR 설계에서 일반적으로 적용되는 도체 폭/간격/폭은 일반적으로 7mil/7mil/7mil 또는 8mil/10mil/8mil입니다. 도체 폭이 같을 때 도체 손실은 재료와 관계 없이 도체 길이에 양의 비례합니다. 따라서 전체 전송 손실을 줄이려면 유전 손실만 고려해야 합니다. 식 (3)에 따르면 유전 손실은 유전 손실 계수에 비례하며 유전 손실을 작게 적용하면 유전 손실을 줄이는 데 도움이 되어 전체 전송 손실을 초래할 수 있습니다.

표 1은 전송속도 14Gb/s, 도체폭 8mil, 임피던스 50Ω일 때 일반 고속기판 3가지 속성 파라미터와 식 (1), (2), (3)에 따라 계산된 손실값을 나타낸다.

| 보드 재료 매개변수 | FR4 | Nelco4000-13SI | 메그트론6 |

| [email protected] | 0.02 | 0.008 | 0.004 |

| [email protected] | 4.10 | 3.200 | 3.600 |

| 조건 @7GHz/in | 0.24 | 0.240 | 0.240 |

| 딜 @7GHz/in | 0.65 | 0.230 | 0.120 |

| [email protected]/in | 0.89 | 0.470 | 0.360 |

| [email protected]/30인치 | 27.00 | 14.000 | 11.000 |

| 상대 비용 | 1.00 | 3.500 | 8.000 |

전송 속도가 14Gb/s이고 전송 길이가 30인치일 때 Nelco4000-13SI의 전체 전송 손실은 약 14dB인 반면 일반적인 FDR 칩이 견딜 수 있는 전압 스윙 감쇠는 20dB~ 25dB. 따라서 이러한 유형의 기판 재료는 전송 거리가 30인치 미만인 FDR 상호 연결 스위치 기판 설계에 적용할 수 있습니다. 그러나 FR4의 전체 전송 감쇠는 약 27dB이며 FR4는 장거리 설계의 FDR 설계에 적용할 수 없지만 전송 거리가 짧은 FDR 상호 연결 인터페이스 카드는 비용 절감을 위해 FR4를 선택할 수 있습니다. 전체 전송 감쇠가 가장 작은 Megtron6의 경우 비용이 가장 높고 FDR에 적용하면 시스템 아키텍처 비용이 증가합니다. 결론적으로 고주파 PCB의 경우 기판 재질이 기본이며 기판 재질의 선택에 따라 신호의 전송 길이가 결정됩니다.

PCB 설계를 위해서는 먼저 회로 기판 구조와 스택을 고려해야 합니다. 일반적으로 회로 기판의 패턴과 모양이 결정되고 스택 수의 결정은 신호 주파수, 회로 기판 핀 밀도, PCB 제조 비용, 제조 기간 및 신뢰성 요구 사항에 있습니다. FDR 상호 접속 스위치 보드는 고주파수와 밀도를 가지며 다층 보드의 적용은 간섭을 줄이는 데 필요한 단계입니다. 또한 스택 번호를 결정하는 것이 중요합니다.

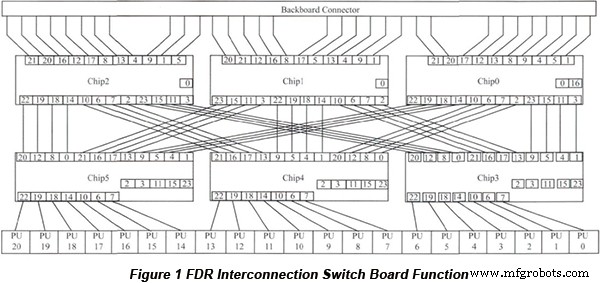

FDR 인터커넥션 칩에는 24개의 포트가 있으며 각 포트에는 8개의 Tx 채널과 8개의 Rx 채널이 있으며 인터커플링 동작 방식입니다. 6개의 인터커넥션 칩과 3개의 다운링크 칩은 FDR 인터커넥션 보드에 의해 적용되며 32개의 포트는 백보드 커넥터를 통해 액세스됩니다. 3개의 업링크 칩은 QSFP(Quad Small Form-factor Pluggable) 광섬유를 통해 21개의 포트에 액세스합니다. 업링크 칩과 다운링크 칩은 그림 1과 같이 4개의 포트를 통해 서로 연결됩니다.

FDR은 BGA(Ball Grid Array) 패키지로 면적 50mmx50mm, 1157핀, 간격 1.0mm로 Tx, Rx 포트의 P/N 핀이 3개의 동심원을 따라 분포되어 있는 것이 특징이다. 이론적으로 3개의 신호 레이어를 적용하여 모든 포트의 모든 핀을 BGA 밖으로 리드할 수 있습니다. 다음 두 가지 요소를 고려하면 두 개의 신호 레이어를 사용하여 동심원의 핀 그룹에 액세스할 수 있습니다.

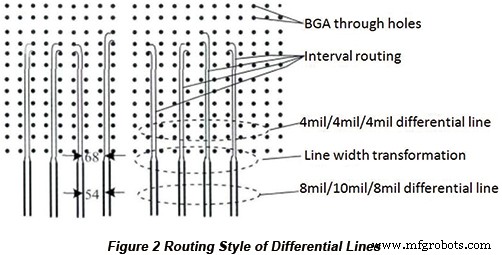

a. 간격 제한으로 인해 차동 라인의 선폭/간격/폭은 4mil/4mil/4mil이며 BGA에서 나오는 8mil/10mil/8mil로 확장되며 차동 라인 쌍 사이의 거리는 4mil/4mil/8mil 이상이어야 합니다. 50만 따라서 한 쌍의 차동 라인은 2mm의 폭을 차지해야 하고 48 쌍의 신호는 가장 밀도가 높은 가장자리를 따라 있습니다. 따라서 이 방법을 구현하기가 어렵습니다.

b. BGA 핀 사이의 간격은 1mm입니다. 동심원 신호 그룹에 액세스하기 위해 신호 레이어가 적용되는 경우 BGA 아래의 차동 라인 쌍 사이의 간격은 필요한 50mil에서 멀리 떨어진 14mil에 불과합니다. 또한 최대 병렬 라우팅 길이는 20mm에 불과하므로 약간의 누화가 발생합니다.

위에서 언급한 부정적인 요인을 피하기 위해 동심원 신호 그룹에 액세스하기 위해 두 개의 신호 레이어가 적용되고 각 신호 레이어의 차동 신호는 50mil 간격에 따라 BGA 밖으로 유도되어야 합니다. 따라서 FDR 상호 연결 보드는 BGA에서 나오는 모든 차동 신호를 만들기 위해 최소 6개의 레이어가 필요합니다. 보드의 연결성 및 라우팅 양, 교환 커플링 커패시터를 위한 충분한 보드 표면을 고려하여 8개의 내부 신호와 22개의 레이어 스택이 적용됩니다.

Crosstalk는 고속 및 고밀도 회로 설계 측면에서 첫 번째 고려 사항입니다. 공격 라인의 전압과 전류가 변경되면 공격 라인과 희생 라인 사이의 상호 정전 용량 및 상호 인덕턴스를 통해 전자기 결합이 발생합니다. 희생선을 따라 송신단으로 흐르는 누화를 근거리 누화라고 하고, 희생선을 따라 수신단으로 흐르는 누화를 원거리 누화라고 한다. 일반적으로 희생 라인의 전체 노이즈 전압은 신호 전압의 5% 미만으로 제어되어야 합니다. 싱글 에지 공격 라인의 크로스토크 버짓을 1% 이내로 조절하는 것이 가장 좋은데, 희생 라인 양측의 다른 노이즈 소스와 공격 라인을 고려하는 것이 좋다.

누화 감소 측면에서 따라야 할 핵심 사항은 다음과 같습니다.

a. 공격 라인과 희생 라인 사이의 간격을 늘리고 평행 라우팅 길이를 줄여야 합니다.

b. 통합 접지는 신호의 반환 경로로 적용됩니다. 경험적 법칙에 따르면 50Ω의 스트립 라인에 대해 간격이 라인 폭의 3배일 때 근단 크로스토크는 약 0.5%입니다. 50Ω의 마이크로스트립 선로의 경우 간격이 선폭의 3배일 때 근단 누화는 약 1%이다. 스트립 라인 또는 완전히 내장된 마이크로스트립 라인의 원단 누화는 거의 0에 가깝고 마이크로스트립 전송 라인의 원단 누화 극성은 음의 크기로 상대적으로 크기가 커서 유도 결합의 영향이 용량 결합보다 크기 때문입니다.

• 간격 라우팅

이 설계에서 고속 차동 라인의 차동 임피던스는 100Ω입니다. Si9000 필드 솔버를 기반으로 라인 너비/간격/라인 너비는 8mil/10mil/8mil로 계산됩니다. 선이 넓을수록 감쇠가 작아지며 10mil의 간격은 100Ω의 차동 임피던스를 유지하기 위한 것입니다. 이러한 종류의 차동 라인은 BGA 칩 영역 외부에 적용됩니다. 누화를 줄이기 위해 두 쌍의 차동 라인 사이의 간격은 80mil 이상입니다. The spacing between pins of interconnection chip in this article is 1mm and the through hole size limitation of BGA makes the line width/spacing/line width of the differential line in the BGA chip area 4mil/4mil/4mil. Although the differential impedance of this type of differential line is 100Ω as well, the lead loss is big, requiring differential line of 4mil/4mil/4mil to be transformed into 8mil/10mil/8mil as soon as it enters BGA chip area. In order to reduce crosstalk, differential line of 4mil/4mil/4mil in BGA chip area applies the way of interval routing to ensure the spacing between two pairs of differential lines more than 50mil as well, which is shown in Figure 2.

• Differential holes

Specific differential holes are set in this design for the application of exchange coupling capacitance on the connection surface layer. Ground holes have to be placed beside differential holes to provide backflow channel for returning path. Design of four ground holes features the best effect and two ground holes can be also applied when the area of board is limited. Besides, measures such as back drilling and internal pad eliminationhave should be taken to differential holes to reduce the impedance change at differential holes in order to decrease crosstalk and reflection.

• Preventing Tx and Rx from being routed in the same layer

In order to reduce crosstalk, Tx differential line should be routed in the different layer from Rx differential line. Here, Tx refers to the source terminal of differential line while Rx refers to the receiving terminal of differential line. If both of them have to be routed in the same layer, the spacing between them has to be over 5mm to ensure safety.

• 20H rule

In the PCB circuit with high frequency and high speed, RF energy is coupled by PCB power layer and ground layer and edge magnetic flux leakage is generated between power layer and ground layer. The radio RF energy can be radiated to the free space. 20H rule indicates that if there are high-speed currents on the board, there are electromagnetic fields associated with them. In the design of this article, the distance between all the routings and board edge should be at least 20 times of line width and the distance between high-speed differential holes and power plane cut-off lines is at least 5mm.

• Routing on the surface layer

In the design of high-frequency PCBs, with the relatively big far-end crosstalk between microstrip lines and strip lines considered, high-speed differential lines are prohibited on the surface layer. In the design of this article, at most 8 internal routing layers are required owing to the limitation of manufacturing craft. Moreover, the terminal arrangement limitation of interconnection chip makes it impossible for internal layers only to implement the connections of the interconnection differential lines between 6 chips inside connection board.

Helpful Resources

• Something You Must Know about HDI

• History of High-Density Packaging Technology

• 3 Keys to Designing a Successful HDI PCB

• Advantages of HDI Printed Circuit Boards

• Full Feature PCB Manufacturing Service from PCBCart - Multiple Value-added options

• Advanced PCB Assembly Service from PCBCart - Start from 1 piece

산업기술

솔더 마스크란 무엇입니까? 솔더 레지스트 또는 솔더 스톱 마스크/코팅이라고도 하는 솔더 마스크는 PCB 신뢰성과 고성능을 보장하기 위해 상단과 하단의 인쇄 회로 기판(PCB)에 솔더링할 필요 없이 구리 트레이스를 덮는 얇은 층입니다. 수지는 일반적으로 내습성, 절연성, 내땜납성 및 고온 내성 및 미관 면에서 우수한 작용을 하기 때문에 솔더 마스크의 주요 재료로 선택됩니다. 대부분의 PCB는 실제로 솔더 마스크 그린 오일의 색상인 녹색으로 간주됩니다. 그러나 솔더 마스크는 녹색, 흰색, 파란색, 검정색, 빨간색, 노란색 등 다양

오늘날 RF/Microwave PCB는 의료, 통신 등을 포함한 수많은 휴대용 무선 장치 및 상업 산업에서 광범위하게 적용되는 것을 목격했습니다. RF(무선 주파수)/Microwave 회로는 피부 효과 및 결합 효과, 간섭 및 회로의 방사선은 실제 인쇄 회로 기판(PCB) 설계에서 제어하기 어렵습니다. 일반적으로 발생하는 문제로는 디지털 회로와 아날로그 회로 간의 교차 간섭, 전원으로 인한 노이즈 간섭, 부조리한 레이아웃으로 인한 유사한 간섭 문제가 있습니다. 결과적으로 PCB 설계의 장점과 단점을 어떻게 균형을 잡고 간섭을 줄이려