verilog

always 블록은 절차적 중 하나입니다. Verilog의 블록. always 블록 내의 명령문은 순차적으로 실행됩니다.

always @ (event)

[statement]

always @ (event) begin

[multiple statements]

end

always 블록은 특정 이벤트에서 실행됩니다. 이벤트는 민감도 목록으로 정의됩니다.

민감성 list는 always 블록이 실행되어야 하는 시기를 정의하는 표현식으로 @ 뒤에 지정됩니다. 괄호 ( ) 안의 연산자 . 이 목록에는 값 변경이 항상 블록을 실행하는 신호 그룹이 하나 또는 포함될 수 있습니다.

아래 표시된 코드에서 always 안의 모든 명령문은 신호 또는 b의 값이 변경될 때마다 블록이 실행됩니다.

// Execute always block whenever value of "a" or "b" change

always @ (a or b) begin

[statements]

end

always 블록은 조합 또는 순차 요소를 구현하는 데 사용할 수 있습니다. 플립플롭과 같은 순차 소자는 클럭과 리셋이 제공되면 활성화된다. 마찬가지로 조합 블록은 입력 값 중 하나가 변경되면 활성화됩니다. 이러한 하드웨어 블록은 모두 서로 독립적으로 동시에 작동합니다. 각각의 연결이 데이터의 흐름을 결정합니다. 이 동작을 모델링하려면 always 차단은 감도 목록 내의 신호가 활성화될 때 트리거되고 일부 작업을 수행하는 연속 프로세스로 만들어집니다.

다음 예에서 always 블록 내의 모든 명령문은 신호 clk의 모든 양의 에지에서 실행됩니다.

// Execute always block at positive edge of signal "clk"

always @ (posedge clk) begin

[statements]

end

always 블록은 시뮬레이션 기간 동안 계속 반복됩니다. 감도 목록은 특정 타이밍 감각을 가져옵니다. 즉 감도 목록의 신호가 변경될 때마다 항상 차단이 트리거됩니다. 항상 블록 내에 타이밍 제어 문이 없으면 지연이 없는 무한 루프로 인해 시뮬레이션이 중단됩니다!

아래에 표시된 예는 신호 clk의 값을 반전시키려는 always 블록입니다. 명령문은 0 시간 단위마다 실행됩니다. 따라서 명령문에 지연이 없기 때문에 영원히 실행됩니다.

// always block is started at time 0 units

// But when is it supposed to be repeated ?

// There is no time control, and hence it will stay and

// be repeated at 0 time units only. This continues

// in a loop and simulation will hang !

always clk = ~clk;

민감도 목록이 비어 있더라도 다른 형태의 시간 지연이 있어야 합니다. 시뮬레이션 시간은 always 내의 지연 문에 의해 앞당겨집니다. 아래와 같이 구성합니다. 이제 시계 반전은 10시간 단위마다 수행됩니다.

always #10 clk = ~clk;

참고: 명시적 지연은 논리 게이트로 합성할 수 없습니다!

따라서 실제 Verilog 디자인 코드에는 항상 민감도 목록이 필요합니다.

아래 표시된 코드는 데이터 입력, 클록 및 액티브 로우 리셋을 수락하는 tff라는 모듈을 정의합니다. 클럭의 양의 에지에서 d가 1로 발견될 때마다 출력이 반전됩니다. 여기에서 always 블록은 clk의 양의 에지 또는 rstn의 음의 에지에서 트리거됩니다.

다음 이벤트는 클록의 양의 에지에서 발생하고 클록의 모든 양의 에지에 대해 반복됩니다.

if 블록은 액티브 로우 리셋 rstn의 값을 확인합니다.

module tff (input d,

clk,

rstn,

output reg q);

always @ (posedge clk or negedge rstn) begin

if (!rstn)

q <= 0;

else

if (d)

q <= ~q;

else

q <= q;

end

endmodule

다음 이벤트는 rstn의 음수 에지에서 발생하며 이러한 모든 경우에 발생합니다.

if 블록은 먼저 액티브 로우 리셋 값을 확인합니다. 신호의 음의 에지에서 값은 0입니다.

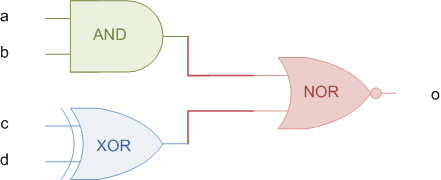

always 블록은 조합 블록 설계에도 사용할 수 있습니다. 예를 들어 다음 디지털 회로는 신호 o에서 특정 출력을 제공하는 3개의 서로 다른 논리 게이트의 조합을 나타냅니다.

아래에 표시된 코드는 module입니다. 4개의 입력 포트와 o라는 단일 출력 포트가 있습니다. always 차단은 민감도 목록의 신호 값이 변경될 때마다 트리거됩니다. 출력 신호는 reg 유형으로 선언됩니다. 절차 블록에서 사용되기 때문에 모듈 포트 목록에 있습니다. 절차 블록에서 사용되는 모든 신호는 reg 유형으로 선언되어야 합니다. .

module combo ( input a,

input b,

input c,

input d,

output reg o);

always @ (a or b or c or d) begin

o <= ~((a & b) | (c^d));

end

endmodule

RHS의 조합 식이 참이 될 때마다 신호 o가 1이 되는 것을 보십시오. 마찬가지로 o는 RHS가 거짓일 때 0이 됩니다.

시뮬레이션 출력시뮬레이션 예제가 있는 슬라이드쇼를 보려면 여기를 클릭하십시오!

verilog

Verilog는 하드웨어 설명 언어이며 설계자가 RTL 설계를 시뮬레이션하여 논리 게이트로 변환할 필요가 없습니다. 시뮬레이션이 필요한 이유는 무엇입니까? 시뮬레이션은 RTL 코드가 의도한 대로 동작하는지 확인하기 위해 다른 시간에 다른 입력 자극을 설계에 적용하는 기술입니다. 기본적으로 시뮬레이션은 설계의 견고성을 검증하기 위해 잘 따라야 하는 기술입니다. 또한 가공된 칩이 실제 세계에서 사용되는 방식과 다양한 입력에 반응하는 방식과 유사합니다. 예를 들어, 위의 디자인은 출력 pe 보여진 바와 같이. 시뮬레이션을 통해

디자인 module pr_en ( input [7:0] a, input [7:0] b, input [7:0] c, input [7:0] d, input [1:0] sel, output reg [7:0] out); always @ (a or b or c or d or sel) begin if (sel == 2b00) out <= a; else if