나노물질

기존의 1트랜지스터(1T)-1캐패시터(1C) DRAM(Dynamic Random Access Memory)의 더 큰 부피와 트랜지스터의 더 높은 누설 전류는 고유한 단점이 되었습니다. 최근에는 낮은 오프 전류와 높은 스위칭 비율로 인해 TFET(Tunneling FET)가 DRAM 셀에 적용되고 있다. 커패시터가 없는 구조의 듀얼 게이트 TFET(DG-TFET) DRAM 셀은 성능이 우수하고 유지 시간(RT)이 높고 온도 의존성이 약합니다. 그러나 TFET DRAM 셀의 성능은 프로그래밍 조건에 민감합니다. 본 논문에서는 시뮬레이션 툴인 실바코 아틀라스(Silvaco Atlas)를 사용하여 프로그래밍 최적화 가이드라인을 자세히 설명합니다. DG-TFET DRAM의 쓰기 및 읽기 작업은 모두 대역 간 터널링(BTBT)에 의존합니다. 쓰기 작업 동안 Gate2에 의해 제어되는 BTBT에서 오는 구멍은 Gate2 아래의 전위 우물에 저장됩니다. Gate2에 작은 음의 전압을 인가하여 "1"을 유지하는 동안 홀을 오랫동안 유지합니다. Gate1에 의해 제어되는 BTBT는 주로 판독 전류에 영향을 미칩니다. 최적화된 프로그래밍 조건을 사용하여 DG-TFET DRAM은 판독값 "1" 대 판독값 "0"의 더 높은 전류 비율을 얻습니다(10 7 ) 및 2초 이상의 RT RT가 높을수록 DRAM의 재생률과 동적 전력 소비가 감소합니다.

<섹션 데이터-제목="배경">DRAM(Dynamic Random Access Memory)은 모바일 및 컴퓨팅 시스템에서 통합 메모리 셀이 되었습니다[1,2,3]. 소자의 기하학적 구조가 축소됨에 따라 대용량 커패시터는 기존의 1트랜지스터(1T)-1 커패시터(1C) DRAM 셀의 고유한 단점이 되어 대규모 애플리케이션을 제한합니다. 플로팅 게이트 트랜지스터를 기반으로 하는 무 커패시터 1T DRAM 셀은 메모리의 고밀도 패키징을 위해 기존 1T-1C DRAM에 비해 잠재적인 이점을 보여주었습니다[4]. 플로팅 게이트 트랜지스터에서 기판 영역의 전하는 Fowler-Nordheim 터널링에 의해 플로팅 게이트 영역에 저장됩니다. 그리고 읽기 동작은 금속 산화물 반도체 전계 효과 트랜지스터(MOSFET)와 동일한 열이온 방출[5, 6]에 의존합니다. 결과적으로 플로팅 게이트 트랜지스터가 있는 DRAM의 읽기 전류는 온도에 크게 의존합니다. 또한 열이온 방출로 인해 트랜지스터의 하위 임계값 스윙(SS)이 60mV/dec보다 높아져 높은 누설 전류와 전력 소비가 주요 문제가 됩니다[7,8,9].

최근 터널링 전계효과 트랜지스터(TFET)는 미래의 저전력 전기소자에 대한 유망한 후보로 여겨져 왔다[10,11,12]. TFET의 주요 전도 메커니즘은 열이온 방출 대신 대역 간 터널링(BTBT)으로, 60mV/dec 이하의 SS, 낮은 오프 상태 누설 전류, 약한 온도 의존성과 같은 여러 이점을 얻습니다. [13, 14]. 지금까지 TFET에 대한 많은 연구 작업은 주로 단일 TFET의 소자 성능에 대한 연구에 중점을 두고 있으며 일부 간단한 회로는 TFET로 구성됩니다. 그러나 높은 I 켜기 /나 꺼짐 TFET는 DRAM 셀에 사용할 수 있습니다[15]. 특히, 낮은 오프 상태 누설 전류는 판독값 "0" 전류와 DRAM 셀의 소비 전력을 줄일 수 있습니다. 연구원들은 커패시터가 없는 구조의 이중 게이트 TFET(DG-TFET) DRAM을 설계했습니다[16]. DG-TFET DRAM에서 쓰기 작업 중 전하 저장은 주로 Gate2에서 생성되는 채널과 드레인 사이의 BTBT를 기반으로 합니다. 동시에 전자의 터널링은 Gate2 아래의 채널 영역에 정공의 축적을 촉진합니다. Gate1은 주로 읽기 작업을 담당합니다. DGTFET DRAM의 읽기 전류는 주로 소스 영역과 채널 영역 사이의 BTBT에 의존합니다. DG-TFET DRAM의 읽기 전류가 온도 의존도가 약함을 입증한 일부 연구 그룹이 있습니다. 그리고 DG-TFET DRAM은 목표(64ms)보다 더 긴 머무름 시간을 얻을 수 있습니다[17]. 그러나 판독값 "1" 대 판독값 "0" 및 RT의 현재 비율은 최적화되지 않은 프로그래밍 조건으로 인해 최적 값이 아닙니다.

TFET DRAM의 성능, 특히 읽기 "1" 대 읽기 "0"의 현재 비율은 프로그래밍 조건에 크게 의존합니다. Gate2는 주로 Gate2 아래의 전하 및 전위 저장 영역을 지배하는 쓰기 작업 동안 BTBT에 영향을 줍니다. Gate1은 판독 작업 중 BTBT를 제어하며, 이는 판독 "1" 전류에 주로 영향을 미칩니다. Gate1과 Gate2의 적절한 바이어스는 DGTFET DRAM이 더 높은 전류 비율을 얻도록 할 수 있습니다. 읽기 전류에 대한 프로그래밍 조건의 영향을 연구하는 문헌이 거의 없습니다. 본 논문에서는 쓰기, 유지, 읽기 연산을 포함한 상세한 프로그래밍 최적화 지침을 제안한다. 최적화된 프로그래밍 조건을 적용하여 DG-TFET DRAM은 최대 10 7 의 읽기 전류 비율인 최적의 성능을 얻습니다. 2초 이상의 RT 그리고 최적화된 프로그래밍 전압을 적용하면 "0" 전류가 참고문헌[16, 18]에 보고된 것보다 훨씬 낮아서 전력 소모를 줄이는 데 도움이 됩니다.

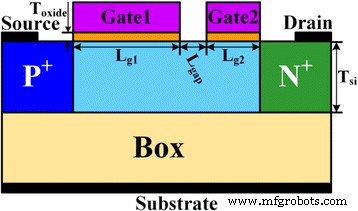

본 논문에서 조사한 DG-TFET의 구조는 그림 1과 같다. 두 P + 의 도핑 농도 소스 및 N + 배수는 1 × 10 20 입니다. /cm 3 . 고유 채널은 Gate1과 Gate2의 두 부분으로 나뉘며 Gate1과 Gate2 사이에는 짧은 간격이 있습니다. Gate1과 Gate2는 N + 입니다. 폴리실리콘 및 P + 각각 폴리실리콘. P + 폴리실리콘 Gate2는 전하 저장을 위한 물리적 우물을 생성 및 유지하고 P + 포켓 영역을 저장 영역으로 사용합니다. N + 동안 폴리실리콘 Gate1의 경우 Gate1과 Gate2 사이 언더랩 영역의 홀 농도가 낮아 읽기에 도움이 됩니다. 따라서 P + 폴리실리콘 Gate2는 더 긴 보존을 용이하게 할 수 있는 더 깊은 저장 영역을 갖도록 선택되었으며 N + 폴리실리콘 Gate1은 읽기 작업 동안 터널링 메커니즘을 제어하기 위해 선택됩니다[18].

<그림>

DG-TFET DRAM 셀의 개략도. 이 그림은 Gate1, Gate2, 소스, 드레인 및 채널을 포함하는 이중 게이트 TFET(DGTFET) DRAM 셀의 개략도를 보여줍니다. 이 설계에서 소스 영역과 드레인 영역은 P + 입니다. 도핑 및 N + 각각 도핑. Gate1과 Gate2는 N + 입니다. 폴리실리콘 및 P + 폴리실리콘, 각각

시뮬레이션의 자세한 장치 매개변수는 다음과 같습니다. 벌크 실리콘의 두께(T 시 )는 20nm입니다. Gate1의 길이(Lg1 ) 및 Gate2(Lg2 )는 각각 400nm 및 200nm입니다. 간격의 길이(L 갭 ) Gate1과 Gate2 사이는 50nm입니다. 게이트 산화물의 두께(HfO2 ) (T 산화물 )는 3nm입니다. 최적화된 프로그래밍 조건은 표 1과 같습니다. 프로그래밍 조건의 최적화 지침은 다음 섹션에서 자세히 설명합니다.

모든 분석은 Nonlocal BTBT 모델을 사용하여 Silvaco-Atlas 도구에서 수행됩니다[19]. Nonlocal BTBT는 전자와 정공의 nonlocal 생성을 고려하여 터널링 프로세스를 보다 정확하게 모델링할 수 있습니다. 터널링 모델 매개변수는 참고문헌[20]의 실험 데이터에 따라 보정됩니다. 또한 Shockley-Read-Hall 재조합, Fermi 통계, 도핑 및 전기장 종속 이동성을 포함한 물리적 모델도 사용됩니다. [16, 18]의 접근 방식에 따르면 전자 및 정공 수명은 100ns로 설정됩니다. 기본 온도는 300K입니다.

DG-TFET DRAM 셀의 작동 원리는 기존 DRAM과 다릅니다. 쓰기 및 읽기 작업은 모두 BTBT를 기반으로 하지만 각각 기능이 다릅니다. "1"을 쓰는 동안 BTBT는 구멍이 Gate2 아래의 전위 우물에 저장되도록 하여 판독값 "1" 전류를 높일 수 있습니다. 읽기 동작 동안 드레인 전류는 주로 소스 측 근처의 BTBT에 의존합니다. 또한 두 게이트는 서로 다른 역할도 수행합니다. Gate1과 Gate2는 주로 각각 읽기 작업과 쓰기 작업을 결정합니다.

"1"을 쓰는 동안 음의 바이어스가 있는 Gate2는 Gate2 아래 채널의 에너지 대역을 증가시켜 장벽 너비를 줄이고 채널과 드레인 사이에 BTBT를 생성합니다. 그리고 이 음의 Gate2 바이어스도 Gate2 아래에 깊은 잠재력을 유도합니다. 채널에서 드레인으로 전자의 터널링으로 인해 Gate2 아래의 채널 영역이 완전히 고갈되고 이 전위 우물에 많은 정공이 축적됩니다. "0"을 쓰는 동안 양의 바이어스가 있는 Gate2는 구멍이 배수 측에서 재결합되는 전위 우물에서 배출되도록 합니다[21].

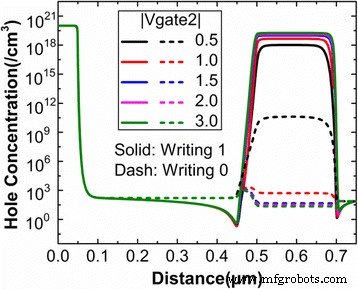

일반적으로 Gate2 전압의 절대값은 "1"을 쓰고 "0"을 쓰는 동안 변하지 않습니다. 그림 2는 기입 동작 후 Gate2 전압에 따른 홀 농도의 변화를 보여준다. Gate2 전압이 0.5V일 때 "0"을 쓴 후 홀 농도는 전위 우물의 존재로 인해 더 높아져 "0" 상태에 해롭습니다. Gate2 전압의 절대값이 1V보다 높을 때 "0"을 쓰고 "1"을 쓴 후 홀 농도는 뚜렷한 변화가 없습니다. 이는 BTBT가 "1"을 쓰기 위해 포화되었고 "1"을 쓰는 동안 축적된 모든 구멍이 "0"을 쓴 후 포텐셜 우물에서 추방됨을 시사합니다. 그리고 "1"을 쓰는 것과 "0"을 쓰는 것 사이의 구멍 농도의 차이가 매우 뚜렷하여 "1" 상태와 "0" 상태를 구별하는 데 도움이 됩니다.

<그림>

쓰기 작업 후 채널 표면의 구멍 농도. 이 그림은 다양한 Gate2 전압에 따른 홀 농도의 변화를 보여줍니다. 절단선은 소스 영역에서 드레인 영역까지 디바이스 표면에서 취합니다. 이 그림에서 실선과 점선은 각각 "1"을 쓰고 "0"을 쓴 후의 구멍 농도를 나타냅니다.

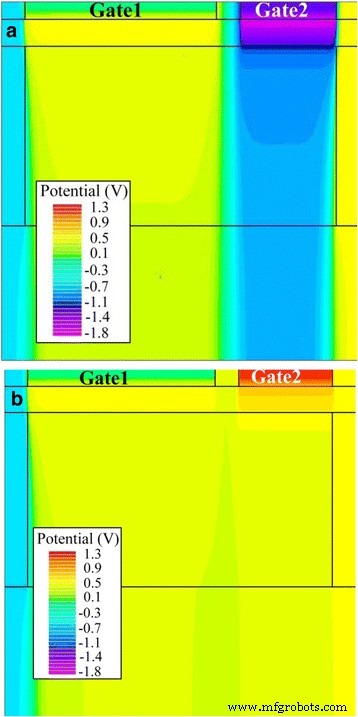

그러나 쓰기 작업 중 Gate2 바이어스는 홀 농도에 의해서만 결정될 수 없습니다. 그림 3은 쓰기 동작 중 Gate2 바이어스가 홀드 동작 후 드레인 전류에 상당한 영향을 미친다는 것을 나타냅니다. 홀딩 동작 중 프로그래밍 전압 세트는 다음 섹션에서 설명합니다. 그림 3은 기록 전압의 절대값이 1.3V보다 높을 때 홀드 동작 후 드레인 전류에 뚜렷한 변화가 없음을 보여줍니다. 따라서 -1.3 및 1.3V는 "1"을 기록하는 동안 최적의 Gate2 전압으로 간주되고 "1" 각각 "0"을 씁니다.

<사진>

"0"을 유지하고 "1"을 유지한 후 DG-TFET의 드레인 전류. 이 그림은 쓰기 전압에 대해 "0"을 유지하고 "1"을 유지한 후 드레인 전류의 변화를 보여줍니다.

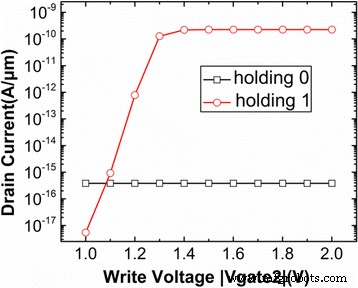

그림 4a, b는 각각 쓰기 전압의 절대값이 1.3V일 때 "1"을 쓰고 "0"을 쓴 후의 전위 윤곽을 나타냅니다. 분명히 "를 쓴 후 Gate2 아래의 채널 영역에 매우 깊은 포텐셜 우물이 생성됩니다. 1", 도 4a에 도시된 바와 같이. 축적된 구멍은 "1"을 쓰는 동안 이 전위 우물에 보존됩니다. 그러나 축적된 구멍은 "0"을 쓰는 동안 이 포텐셜 우물에서 탈출합니다.

<그림>

a 이후의 잠재적 등고선 "1" 및 b 쓰기 Gate2 전압의 절대값이 1.3V일 때 "0"을 씁니다. a , b 각각 "1"을 쓰고 "0"을 쓴 후의 전위 윤곽. 이 그림의 전위 등고선은 Gate2 전압의 절대값을 1.3V로 설정했을 때 추출된 것입니다.

보유 프로세스는 주로 요금 보유를 수정하는 데 사용됩니다. 일반적으로 제로 바이어스는 전력 소비를 줄이기 위해 홀딩 동작 중에 사용됩니다[22]. 홀딩 작업 중에 포텐셜 웰 깊이의 감소로 인해 포텐셜 웰에 축적된 구멍이 점차적으로 재결합됩니다. 따라서 홀딩 작업 최적화의 주요 목적은 홀딩 "1" 동안 홀의 재결합을 방지하는 것입니다. 이 설계에서는 "1"을 유지한 후 잠재적인 우물에 구멍을 유지하기 위해 Gate2에 작은 음의 바이어스가 적용되는 반면 "0"을 유지한 후에는 전위 우물에서 구멍이 고갈됩니다.

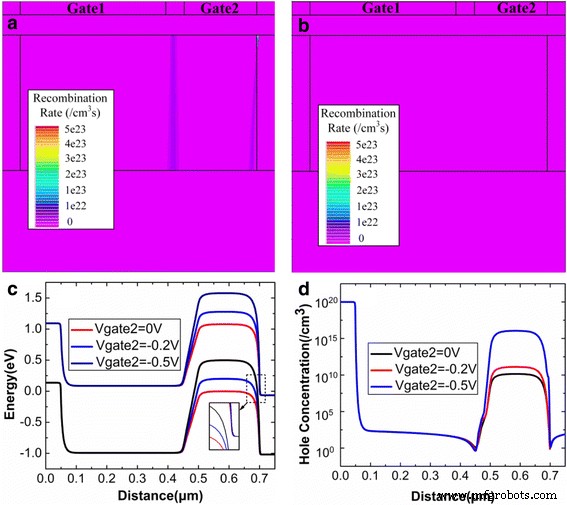

홀딩 동작 동안 더 음의 Gate2 전압(-0.5V)으로, 그림 5a, b와 같이 "1"을 홀딩한 후 홀의 재결합이 제거됩니다. 홀 재결합의 제거는 "1"을 유지하는 동안 홀을 유지하는 데 유리합니다. Gate2에 작은 음의 바이어스를 적용하여 잠재적인 우물 깊이를 높이고 홀을 오랫동안 유지하므로 DGTFET DRAM의 유지 시간에 유리합니다. "0"을 유지하는 동안 음의 Gate2 바이어스는 Gate2 아래 채널 영역의 에너지 대역을 끌어올릴 수 있으며, 이는 소스와 채널 사이의 BTBT에서 나오는 전자가 드레인 쪽으로 흐르는 것을 방지할 수 있습니다. 따라서 음수가 있는 Gate2는 판독값 "0" 전류를 줄일 수 있습니다. 그러나 더 많은 음의 전압(-0.5V)을 갖는 Gate2는 그림 5c와 같이 드레인 측 근처의 터널링 거리를 감소시킵니다. 이 감소된 터널링 거리는 그림 5d와 같이 홀딩 "0" 동안 드레인 측 근처에서 BTBT를 유발하여 홀딩 "0" 동안 포텐셜 우물에 정공의 축적을 촉진합니다. 따라서 "0"을 유지하는 동안 더 음의 Gate2 전압(-0.5V)은 "0" 상태를 저하시킵니다. 따라서 홀딩 "1" 및 "0" 홀딩 시 홀 재결합 및 BTBT를 제거하기 위해 홀딩 동작 시 -0.2V가 최적의 Gate2 바이어스로 간주됩니다.

<그림>

Gate2 전압이 a일 때 "1"을 유지한 후 DG-TFET DRAM 셀의 재결합 속도 0 V 및 b −0.5V ㄷ 에너지 밴드 다이어그램 및 d "0"을 누른 후의 구멍 농도. 아 , b Gate2 전압이 각각 0V 및 -0.5V로 설정되었을 때 "1"을 유지한 후의 재결합 비율입니다. ㄷ 소스 영역에서 드레인 영역으로의 장치 에너지 대역. d 홀링 "0" 후 장치의 홀 농도. 에너지 밴드와 홀 농도는 게이트 산화물 아래 3nm에서 추출됩니다.

다음으로, 읽기 연산의 최적화도 조사됩니다. 읽기 작업은 P + 사이의 BTBT에 크게 의존합니다. 소스 및 채널. "1"을 읽는 동안 Gate1은 주로 소스 측에서 BTBT를 촉진하는 반면, 높은 전압을 가진 Gate2는 전자가 채널에서 드레인으로 흐르는 것을 저항하는 에너지 장벽을 낮춥니다. 그러나 "0"을 읽는 동안 작은 전압의 Gate2는 전자가 채널에서 드레인으로 흐르는 것을 방지할 수 있어야 합니다. 따라서 Gate1 및 Gate2 전압의 최적화는 읽기 작업에 매우 중요합니다.

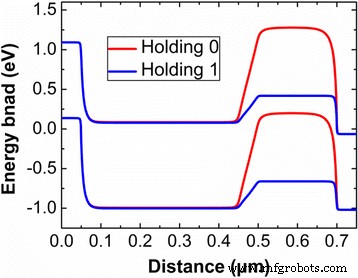

그림 6은 "1"을 유지하고 "0"을 유지한 후의 다른 에너지 밴드 다이어그램을 보여줍니다. "1"을 읽고 "0"을 읽는 동안 동일한 전압이 게이트 측면에 적용됩니다. 양의 게이트 바이어스가 판독 작업 중에 사용되므로 "1" 또는 "0"을 읽을 때마다 에너지 대역이 내려갑니다. "0"을 유지한 후 Gate2 아래 채널의 에너지 밴드는 "1"을 유지한 후보다 높으며 이 에너지 밴드도 "1"을 읽을 때보다 "0"을 읽을 때 더 높습니다. Gate2 아래 채널의 더 높은 에너지는 드레인 측으로 흐르는 전자에 저항하는 효과적인 장벽을 생성하여 판독값 "0" 전류를 감소시킵니다.

<사진>

a 이후의 에너지 밴드 다이어그램 "1"과 b를 누르고 "0"을 유지합니다. 아 , b 각각 "1" 및 "0"을 유지한 후 장치의 에너지 밴드. 에너지 밴드는 게이트 산화물 아래 3nm에서 추출됩니다.

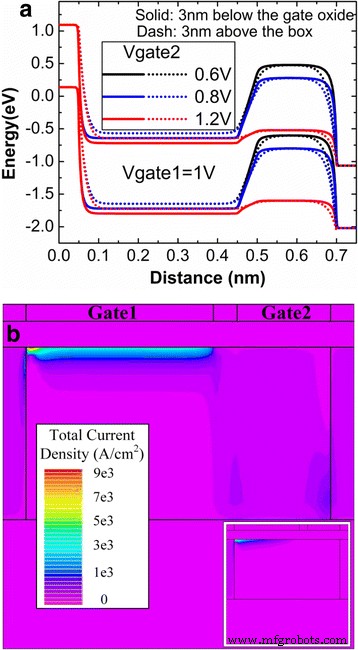

읽기 작업 중에는 DG-TFET에서 드레인 전류를 읽을 수 있도록 드레인 바이어스가 1V로 설정됩니다. 먼저 Gate1 전압을 1V로 유지하면서 Gate2의 바이어스를 변경하여 최적의 Gate2 전압을 선택합니다. Gate2 전압은 주로 판독 "0" 전류에 영향을 미치기 때문에 Gate2 전압의 최적화는 판독 "0" 메커니즘에 의해 분석됩니다. 그림 7a는 "0"을 읽은 후 Gate2 전압에 따른 에너지 대역의 변화를 보여줍니다. Gate2 전압이 더 낮으면(0.6 또는 0.8V) Gate2 아래의 채널이 완전히 고갈됩니다. 그러나 Gate2 전압이 1.2V로 상승하면 Gate2 아래 채널의 풀다운 에너지 대역은 전자가 드레인 쪽으로 흐르는 것을 방지하는 효과적인 장벽을 만들 수 없습니다. 그림 7b와 그 삽입은 각각 Gate2 전압이 1V 및 0.8V일 때 "0"을 읽은 후의 총 전류 밀도를 보여줍니다. 명백한 전류 밀도는 Gate2 전압이 1V일 때 Gate2 아래의 채널 영역에서 명확하게 찾을 수 있습니다. 더 높은 판독값 "0" 전류를 발생시킵니다. 따라서 0.8V는 읽기 프로세스를 위한 최적의 Gate2 전압으로 간주됩니다.

<사진>

아 에너지 밴드 다이어그램 및 b "0"을 읽은 후의 총 전류 밀도. 아 , b 각각 "0"을 읽은 후의 에너지 밴드 및 총 전류 밀도. 에너지 밴드는 게이트 산화물 아래 3nm에서 추출됩니다.

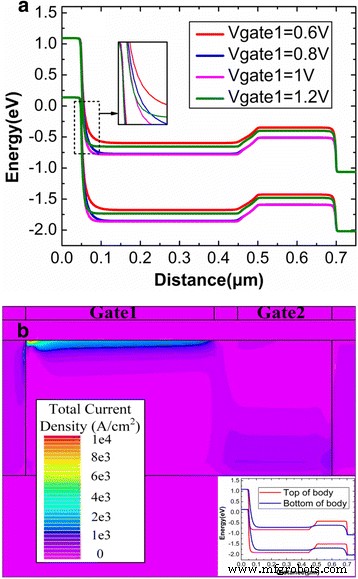

마지막으로 Gate1 바이어스의 최적화도 수행됩니다. 그림 8a는 Gate1 전압에 따른 상단 에너지 대역의 변화를 보여줍니다. 소스 측의 BTBT 장벽 너비는 Gate1 전압이 증가함에 따라 점차 감소하지만 이러한 감소 추세는 Gate1 전압이 1V보다 높을 때 포화되기 시작합니다. 그리고 Gate1 전압 1V는 판독값 "0"에 심각한 영향을 줄 수 없습니다. ” 동작은 그림 7b에 의해 입증되었습니다. 따라서 1V는 읽기 동작 시 최적의 Gate1 바이어스로 간주됩니다.

<사진>

아 에너지 밴드 다이어그램 및 b "1"을 읽은 후의 총 전류 밀도. 아 , b 각각 "1"을 읽은 후의 에너지 밴드 및 총 전류 밀도. 에너지 밴드는 게이트 산화물 아래 3nm에서 추출됩니다.

위의 분석을 통해 "1"을 쓴 후 Gate2 아래 채널 상단에만 deep potential well이 형성됩니다. 따라서 Gate2 아래의 채널 영역에서 채널 상단의 에너지 대역은 채널 하단의 에너지 대역보다 훨씬 높습니다. 이것은 "1"을 읽는 동안 Gate2 아래 채널 상단에 장벽이 있음을 보여줍니다. 그림 8b의 삽입은 "1"을 읽은 후 채널의 상단과 하단 모두에서 에너지 밴드를 표시합니다. 채널 상단의 Gate1과 Gate2 사이에는 더 높은 채널 장벽이 존재하지만 채널 하단에는 이 장벽이 존재하지 않음을 분명히 알 수 있습니다. 따라서 "1"을 읽는 동안 전도 경로는 Gate1 아래의 채널 상단과 Gate2 아래의 채널 하단에 있으며 이는 그림 8의 전류 밀도로 명확하게 입증될 수 있습니다.

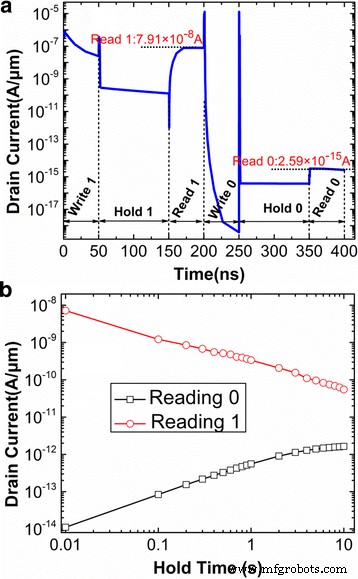

위의 최적화된 프로그래밍 조건을 적용하면 DG-TFET DRAM 셀의 과도 응답이 그림 9에 나와 있습니다. 쓰기 및 읽기 시간은 모두 50ns로 설정되고 유지 시간은 100ns로 설정됩니다. 그림 9a에서 판독값 "1" 대 판독값 "0"의 현재 비율은 10 7 만큼 높습니다. , 이는 10 2 보다 훨씬 높습니다. ~10 3 참조 [16, 18, 23]. 또한, 홀딩 시간이 10초로 증가하더라도 전류비는 여전히 10을 초과한다. 참고문헌[16]에서, 홀딩 시간을 2초로 증가시키면 전류비는 약 10에 불과하다. 따라서 DG-TFET의 RT 최적화된 프로그래밍 조건의 DRAM은 2초 이상입니다. 따라서 최적화된 프로그래밍 조건은 DG-TFET DRAM 셀이 더 높은 판독 전류 비율뿐만 아니라 더 큰 RT를 얻도록 합니다. 또한 최적화된 프로그래밍 전압에서 판독값 "0" 전류가 참조 [16, 18, 22, 23]보다 훨씬 낮아 저전력 애플리케이션을 충족할 수 있습니다.

<그림>

아 작업 순서의 과도 드레인 전류; ㄴ 유지 시간에 따른 판독 전류의 변화. 아 쓰기, 유지 및 읽기 작업 중 DGTFET DRAM 셀의 과도 전류. ㄴ 홀링 시간이 다른 판독값 "1" 및 판독값 "0" 전류의 변화

본 논문에서는 실바코-아틀라스(Silvaco-Atlas) 시뮬레이션 도구를 사용하여 DG-TFET DRAM의 프로그래밍 조건에 대한 상세한 최적화 지침을 제안합니다. "1"을 쓰는 동안 음의 전압(-1.3V)의 Gate2는 전위 우물을 만들고 채널과 드레인 사이의 BTBT는 이 전위 우물에 구멍을 축적합니다. "0"을 쓰는 동안 양의 전압(1.3V)이 있는 Gate2는 정공이 포텐셜 우물에서 빠져나가게 합니다. 홀딩 작업의 경우 Gate2에 작은 음의 전압(-0.2V)을 인가하여 홀을 유지하므로 판독값 "1" 전류를 개선할 수 있습니다. "0"을 유지한 후 Gate2 아래의 채널 장벽은 "0" 전류 판독을 줄이기 위해 드레인 쪽으로 흐르는 전자에 저항할 수 있습니다. 읽기 작업의 최적화를 위해 더 큰 Gate1 전압(1V)은 주로 "1"을 읽는 동안 소스 측에서 BTBT를 향상시키는 데 사용되는 반면 적절한 Gate2 전압(0.8V)은 읽기 중에 드레인으로 흐르는 전자에 저항하는 데 사용됩니다. "0". 최적화된 프로그래밍 조건은 DG-TFET DRAM이 더 높은 전류 비율(10 7 ) 판독 "1"에서 "0" 판독 및 2초 이상의 유지 시간. 그리고 매우 낮은 판독값 "0" 전류는 소비 전력 감소에 도움이 됩니다.

나노물질

로봇 프로그래밍을 시작할 때 알아두면 가장 유용한 기본 속성은 무엇인가요? 로봇 공학의 세계를 처음 접하거나 프로그래밍 기술을 향상시키려는 경우에 알아두면 좋은 최고의 로봇 프로그래밍 기본 사항은 다음과 같습니다. 로봇 프로그래밍을 시작하려면 로봇 학위가 필요하다고 느낄 때가 있습니다. 산업용 로봇 프로그래밍에 대한 기존의 접근 방식은 새로운 로봇 프로그래머가 이해하기 어려워 보입니다. 그러나 로봇 공학의 기본 사항과 우수한 로봇 프로그래밍 소프트웨어만 있으면 쉽고 빠르게 시작할 수 있습니다. 다음은 11가지 가장 유용한

새로운 로봇 프로그래밍 도구에 투자해야 하는지 어떻게 알 수 있나요? 로봇 자동화가 비즈니스에 좋은 방향이라는 것을 알고 있습니다. 어쩌면 이미 로봇을 가동하고 있을지도 모릅니다. 아직 첫 배포를 계획 중일 수 있습니다. 지금이 예산을 더 많이 지출할 적기입니까? 또는 로봇이 잠시 동안 실행될 때까지 기다려야 합니까? 많은 로봇 사용자는 로봇과 함께 제공되는 프로그래밍 옵션을 사용하여 로봇 여행을 시작합니다. 그러나 분명히 다른 프로그래밍 방법이 있습니다. 휴대용 로봇 프로그래밍 도구, 오프라인 프로그래밍 소프트웨