산업기술

지금까지 우리는 논리 감소 문제에 대한 SOP(Sum-Of-Product) 솔루션을 찾았습니다. 이러한 각 SOP 솔루션에는 애플리케이션에 따라 더 유용할 수 있는 POS(생산적합) 솔루션도 있습니다.

합산 솔루션을 작업하기 전에 몇 가지 새로운 용어를 도입해야 합니다. 제품 용어 매핑에 대한 아래 절차는 이 장의 새로운 내용이 아닙니다.

우리는 maxterms에 대한 새로운 절차와 비교하기 위해 minterms에 대한 공식적인 절차를 수립하고자 합니다.

단기

미팅 1이 되는 부울 표현식입니다. 단일 셀 출력의 경우 0 Karnaugh 맵 또는 진리표의 다른 모든 셀에 대해 s. minterm이 하나의 1이 있는 경우 나머지 셀은 0 s, 1의 최소 영역을 포함하는 것으로 보입니다. s.

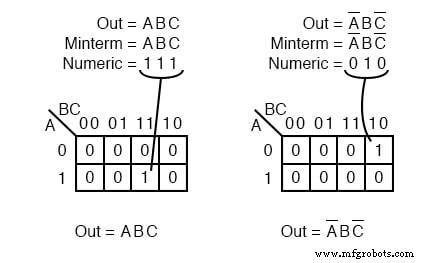

위 왼쪽 그림은 minterm ABC를 보여줍니다. , 단일 제품 용어, 단일 1 그렇지 않으면 0인 지도에서 에스. 0이(가) 표시되지 않았습니다. Karnaugh 지도의 s는 특별히 필요한 경우가 아니면 생략하는 것이 일반적이므로 여기까지입니다. 또 다른 minterm A'BC' 오른쪽 위에 표시됩니다.

검토할 점은 셀의 주소가 매핑되는 최소값에 직접 해당한다는 것입니다. 즉, 셀 111 최소항 ABC에 해당 왼쪽 위.

위 오른쪽에서 minterm A'BC' 셀 010에 직접 해당 . 부울 표현식 또는 지도에는 여러 개의 최소항이 있을 수 있습니다.

위의 그림을 참조하여 K-map에 minterm을 배치하는 절차를 요약해 보겠습니다.

<울>

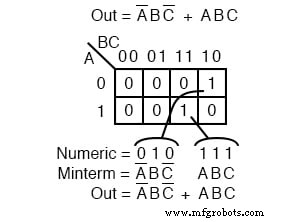

부울 표현식은 위에 표시된 것처럼 Karnaugh 맵의 여러 셀에 해당하는 여러 최소 항으로 구성되는 경우가 많습니다. 이 맵의 다중 최소 항은 위의 이전 그림에서 조사한 개별 최소 항입니다.

우리가 참조를 위해 검토하는 요점은 1 s는 하나 이상의 제품 용어로 직접 변환되는 이진 셀 주소로 K-맵에서 나옵니다.

직접적으로는 0 보완된 변수에 해당하고 1 실제 변수에 해당합니다. 예:010 A'BC'로 직접 변환 .

이 예에서는 감소가 없었습니다. 그러나 우리는 minterms의 Sum-Of-Products 결과를 가지고 있습니다.

위의 그림을 참조하여 K-map에서 Sum-Of-Products Reduced Boolean 방정식을 작성하는 절차를 요약해 보겠습니다.

<울>지금까지 새로운 것은 없었고, 최소 조건을 처리하기 위한 공식 절차가 작성되었습니다. 이것은 maxterm을 처리하기 위한 패턴 역할을 합니다.

다음으로 0인 부울 함수를 공격합니다. 단일 셀 및 1 다른 모든 사람들을 위한 것입니다.

맥스텀

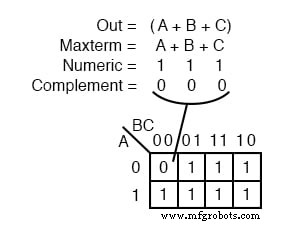

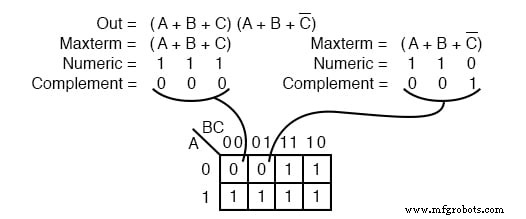

최대 기간 0이 나오는 부울 표현식입니다. 단일 셀 표현식의 출력, 1 Karnaugh 맵 또는 진리표의 다른 모든 셀에 대한 s. 위 왼쪽 그림은 maxterm (A+B+C)을 보여줍니다. , 단일 합계 용어, 단일 0 그렇지 않으면 1인 지도에서 s.

maxterm에 단일 0이 있는 경우 나머지 셀은 1 s, 그것은 1의 최대 영역을 커버하는 것으로 보입니다. s.

새로운 maxterms를 다루기 때문에 약간의 차이점이 있습니다. maxterm은 0입니다. , 1이 아님 카르노 맵에서 최대항은 합계 항입니다. (A+B+C) 이 예에서는 제품 용어가 아닙니다. (A+B+C) 000 셀에 매핑됩니다. .

Out=(A+B+C)=0 방정식의 경우 , 세 변수 모두 (A, B, C) 개별적으로 0과 같아야 합니다. . (0+0+0)=0만 0과 같습니다. . 따라서 우리는 유일한 0 최소 기간 동안 (A+B+C) 셀 A,B,C=000 입력이 모두 0인 K-맵에서 .

이것은 우리에게 0을 줄 유일한 경우입니다. 우리의 maxterm을 위해. 다른 모든 셀에는 1이 포함됩니다. ((0,0,0) 이외의 모든 입력 값 때문에 (A+B+C) 수익 1 s 평가 시.

위의 그림을 참조하여 K-map에 maxterm을 배치하는 절차는 다음과 같습니다.

<울>

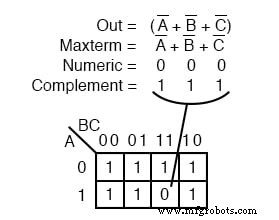

또 다른 극단어 A'+B'+C' 위에 나와 있습니다. 숫자 000 A'+B'+C'에 해당 . 보수는 111입니다. . 0 배치 최대 용어 (A'+B'+C') 이 셀의 (1,1,1) 위와 같이 K-map을 사용합니다.

(A'+B'+C')해야 하는 이유 0 발생 111 셀에 있어야 함 ? A'+B'+C'일 때 (1'+1'+1')입니다. , 모두 1 s in, 즉 (0+0+0) 보완을 취한 후 0을 줄 수 있는 유일한 조건이 있습니다. . 모든 1 s는 모든 0에 보완됩니다. s, 0 또는일 때 에드.

Boolean Product-Of-Sum 표현식 또는 맵에는 위에 표시된 것처럼 여러 개의 최대항이 있을 수 있습니다. 맥스텀 (A+B+C) 숫자 111 산출 000을 보완합니다. , 0 배치 셀 (0,0,0) . Maxterm (A+B+C') 숫자 110 산출 001을 보완합니다. , 0 배치 셀 (0,0,1) .

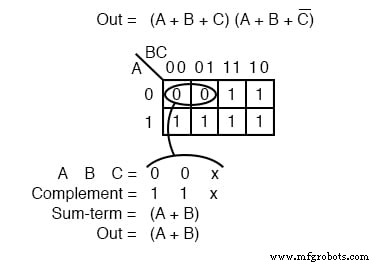

이제 k-map 설정이 완료되었으므로 실제로 관심 있는 것은 Product-Of-Sum 감소를 작성하는 방법을 보여주는 것입니다. 0 형식 그룹으로 s. 그것은 아래의 두 그룹이 될 것입니다. (0,0,X)인 합에 해당하는 이진 값을 작성합니다. .

A와 B 모두 0입니다. 그룹을 위해. 그러나 C 둘 다 0입니다. 및 1 그래서 우리는 X를 씁니다. C의 자리 표시자로 . 보완 (1,1,X) 형성 . 요약 (A+B) 쓰기 C 삭제 및 X 그 자리를 지켰습니다.

일반적으로 합계 결과에서 더 많은 합계 항이 함께 곱해질 것으로 예상합니다. 하지만 여기에 간단한 예가 있습니다.

K-map에 대한 Product-Of-Sums 부울 감소를 작성하는 절차를 요약해 보겠습니다.

<울>

예

예:

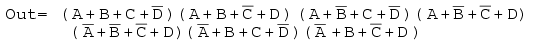

POS 형식의 결과를 제공하여 아래의 Product-Of-Sums 부울 표현식을 단순화하십시오.

해결책:

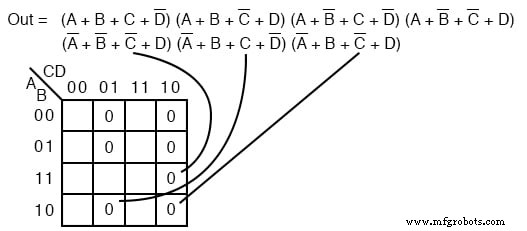

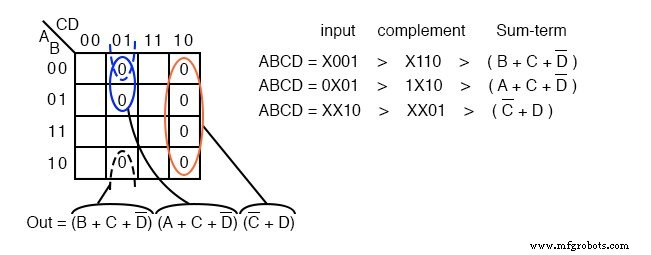

7개의 maxterm을 아래 지도에 0으로 전송합니다. 에스. 적절한 셀 위치를 찾을 때 입력 변수를 보완해야 합니다.

0을 매핑합니다. s 위의 지도에서 왼쪽에서 오른쪽 위에서 아래로 나타납니다. 지시선이 있는 마지막 세 개의 maxterms를 찾습니다.

위의 위치에 셀이 있으면 아래와 같이 셀 그룹을 형성합니다. 더 큰 그룹은 더 적은 수의 입력으로 합계 항을 제공합니다. 그룹이 적을수록 결과에서 더 적은 합계가 생성됩니다.

3개의 그룹이 있으므로 위의 POS 결과에 3개의 합계가 있을 것으로 예상합니다. 4-셀 그룹은 2-변수 합계 항을 생성합니다. 2개의 셀로 구성된 두 그룹은 2개의 3변수 합계 항을 제공합니다.

위의 Sum-terms에 어떻게 도달했는지에 대한 세부 정보가 표시됩니다. 그룹의 경우 이진 그룹 입력 주소를 작성한 다음 이를 보완하여 부울 합계 항으로 변환합니다. 최종 결과는 세 합계의 곱입니다.

예:

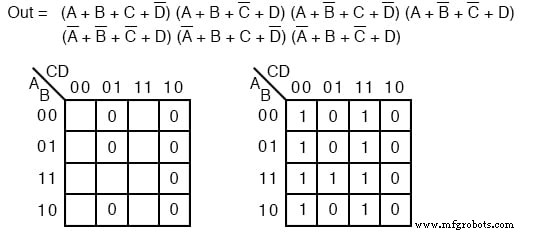

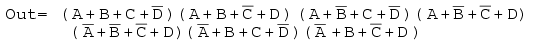

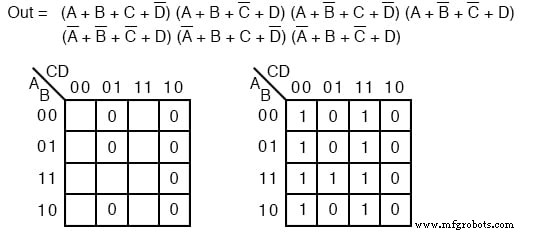

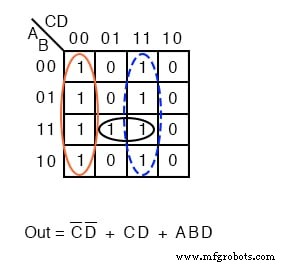

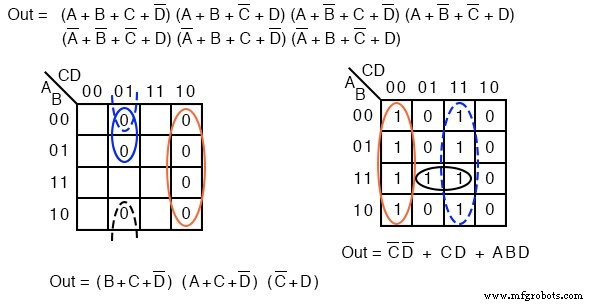

SOP 형식의 결과를 제공하여 아래의 Product-Of-Sums 부울 표현식을 단순화하십시오.

해결책: 이것은 마지막 문제의 반복처럼 보입니다. 우리가 방금 완료한 Product-Of-Sum 대신 Sum-Of-Products Solution을 요청한 것 외에는 다릅니다. maxterm 0 매핑 s는 이전 문제에서와 같이 주어진 합계의 곱에서 나온 것입니다(왼쪽 아래).

그런 다음 암시된 1을 입력합니다. 오른쪽 위 지도의 나머지 셀에 있습니다.

1의 그룹 형성 모든 1을 포함하는 s 에스. 그런 다음 이 장의 이전 섹션에서와 같이 Sum-Of-Products 단순화된 결과를 작성합니다. 이것은 이전 문제와 동일합니다.

위에서 우리는 비교를 위해 이전 예제의 합산 솔루션과 현재 문제의 곱 합 솔루션을 모두 보여줍니다.

더 간단한 솔루션은 무엇입니까? POS는 3-OR 게이트와 1-AND 게이트를 사용하는 반면 SOP는 3-AND 게이트와 1-OR 게이트를 사용합니다. 둘 다 각각 4개의 게이트를 사용합니다.

자세히 살펴보면 게이트 입력 수를 계산합니다. POS는 8개 입력을 사용합니다. SOP는 7개 입력을 사용합니다. 최소 비용 솔루션의 정의에 따라 SOP 솔루션은 더 간단합니다.

이것은 실제 세계에서 거의 사용되지 않는 기술적으로 정답의 예입니다.

더 나은 솔루션은 복잡성과 사용되는 논리 제품군에 따라 다릅니다. SOP 솔루션은 일반적으로 TTL 로직 제품군을 사용하는 경우 더 좋습니다. NAND 게이트는 SOP 구현과 잘 작동하는 기본 빌딩 블록이기 때문입니다.

반면에 모든 크기의 NOR 게이트를 사용할 수 있으므로 CMOS 로직 제품군을 사용할 때 POS 솔루션을 사용할 수 있습니다.

두 경우 모두에 대한 게이트 다이어그램이 위에 나와 있습니다. Product-Of-Sums는 왼쪽이고 Sum-Of-Products는 오른쪽입니다.

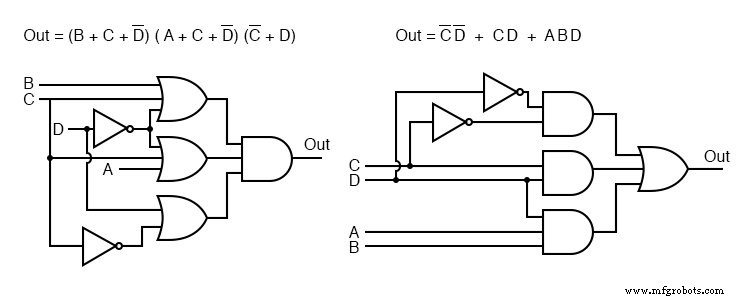

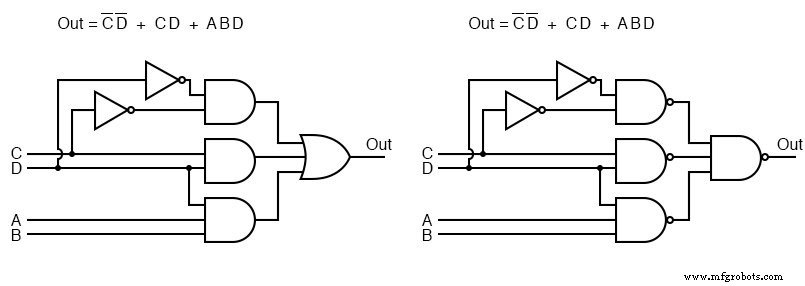

아래에서 왼쪽에서 반복되는 예제 로직의 Sum-Of-Products 버전을 자세히 살펴보겠습니다.

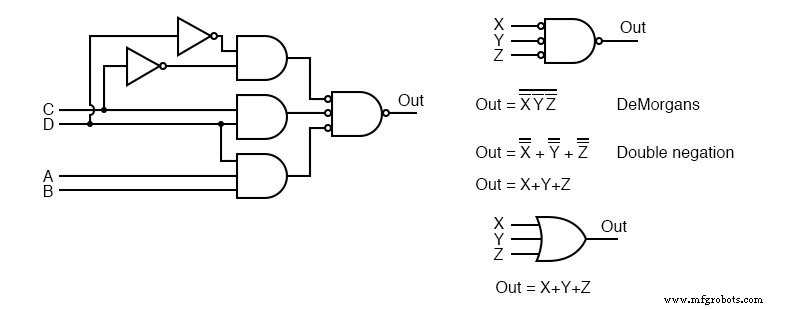

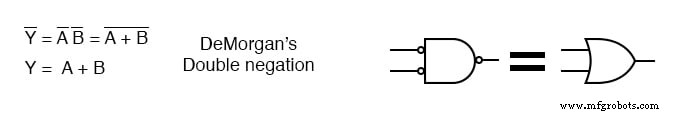

무엇보다도 왼쪽의 AND 게이트는 오른쪽의 NAND 게이트로 대체되었습니다.. 출력의 OR 게이트는 NAND 게이트로 대체되었습니다. AND-OR 논리가 NAND-NAND 논리와 동일함을 증명하기 위해 오른쪽 위에서 왼쪽 아래로 이동하는 것과 같이 3-NAND 게이트의 출력에서 인버터 반전 버블을 최종 NAND의 입력으로 이동합니다.

오른쪽 위에서 우리는 입력이 반전된 출력 NAND 게이트가 DeMorgan의 정리와 이중 부정에 의해 논리적으로 OR 게이트와 동일하다는 것을 알 수 있습니다.

이 정보는 TTL 논리 제품군 NAND 게이트가 다른 유형보다 다양한 구성에서 더 쉽게 사용 가능한 실험실 환경에서 디지털 논리를 구축하는 데 유용합니다.

AND-OR 논리 대신 NAND-NAND 논리를 구성하는 절차는 다음과 같습니다.

<울>

예:

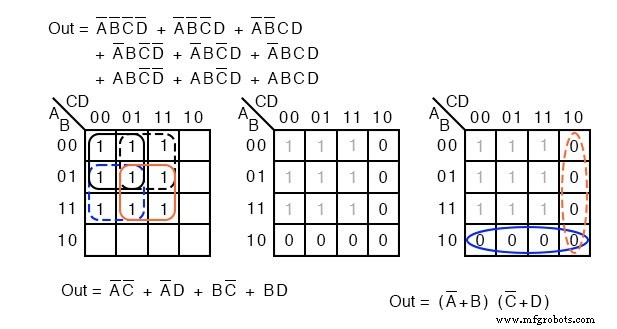

SOP 최소화와 관련된 이전 문제를 다시 살펴보겠습니다. 합산 솔루션을 생성합니다. POS 솔루션을 이전 SOP와 비교합니다.

해결책:

위 왼쪽에는 9분짜리 부울 단순화되지 않은 표현으로 시작하는 원래 문제가 있습니다. 검토하면서 4개의 셀로 구성된 4개의 그룹을 구성하여 4-product-term SOP 결과를 산출했습니다(왼쪽 하단).

위의 중간 그림에서 암시적인 0으로 빈 공간을 채웁니다. 에스. 0 s는 4-cell의 두 그룹을 형성합니다. 파란색 실선 그룹은 (A'+B)입니다. , 빨간색 점선 그룹은 (C'+D)입니다. . 그러면 오른쪽 위의 합산 결과에서 두 개의 합계 항이 생성됩니다. Out =(A'+B)(C'+D)

이전 SOP 단순화(왼쪽)와 POS 단순화(오른쪽)를 비교하면 POS가 최소 비용 솔루션임을 알 수 있습니다. SOP는 총 5개 게이트를 사용하고 POS는 3개 게이트만 사용합니다.

이 POS 솔루션은 결과의 단순성으로 인해 TTL 로직을 사용할 때도 매력적으로 보입니다. AND 게이트와 2개의 입력이 있는 OR 게이트를 찾을 수 있습니다.

SOP 및 POS 게이트 다이어그램은 비교 문제에 대해 위에 나와 있습니다.

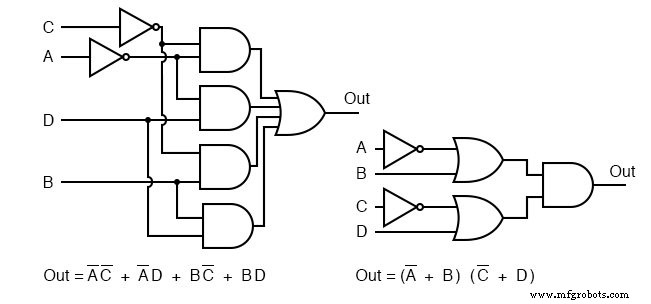

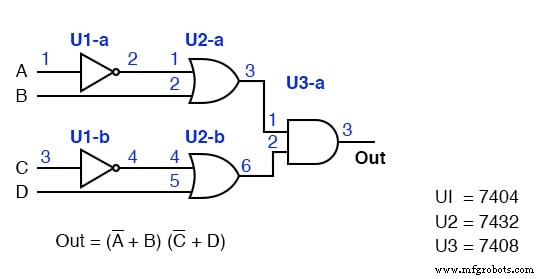

아래의 TTL 로직 제품군 집적 회로 게이트에 대한 핀아웃이 주어지면 오른쪽 위의 maxterm 다이어그램에 회로 지정자(U1-a, U1-b, U2-a 등) 및 핀 번호로 레이블을 지정하십시오.

우리가 사용하는 각 집적 회로 패키지는 회로 지정자 U1, U2, U3을 받습니다. 패키지 내의 개별 게이트를 구별하기 위해 a, b, c, d 등으로 식별됩니다.

7404 육각 인버터 패키지는 U1입니다. 개별 인버터는 U1-a, U1-b, U1-c 등입니다. U2는 7432 쿼드 OR 게이트에 할당됩니다. U3는 7408 쿼드 AND 게이트에 할당됩니다.

위 패키지 다이어그램의 핀 번호를 참조하여 아래 회로도의 모든 게이트 입력 및 출력에 핀 번호를 할당합니다.

이제 실험실 환경에서 이 회로를 구축할 수 있습니다. 또는 인쇄 회로 기판을 설계할 수 있습니다. 그것을 위해. 인쇄 회로 기판에는 페놀 또는 에폭시 유리 섬유의 비전도성 기판으로 뒷받침되는 구리 호일 "배선"이 포함되어 있습니다.

인쇄 회로 기판은 전자 회로를 대량 생산하는 데 사용됩니다. 사용하지 않는 게이트의 입력을 접지하십시오.

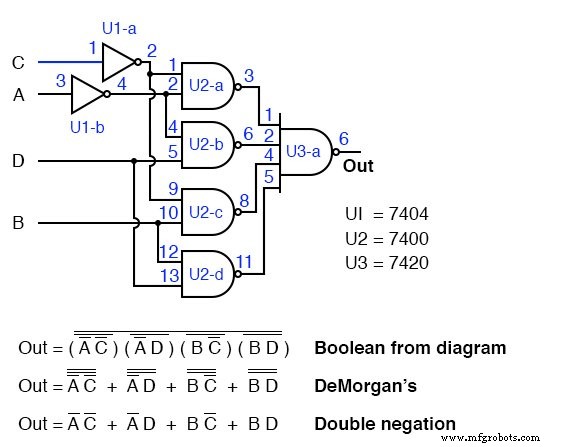

왼쪽 위의 이전 POS 솔루션 다이어그램(뒤에서 세 번째 그림)에 회로 지정자와 핀 번호로 레이블을 지정합니다. 이것은 우리가 방금 한 것과 유사할 것입니다.

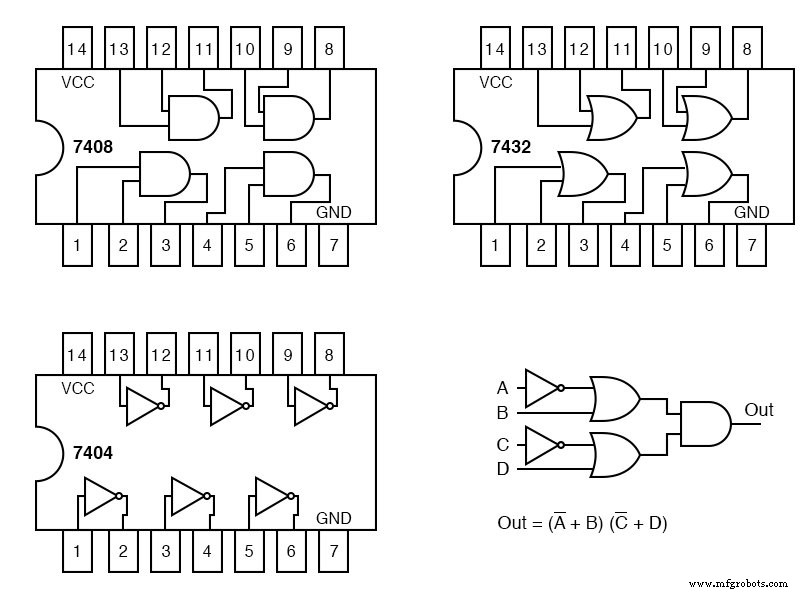

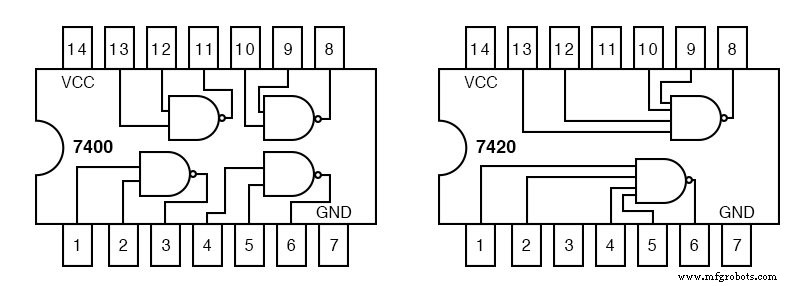

앞의 예에서 2입력 AND 게이트 7408을 찾을 수 있습니다. 그러나 TTL 카탈로그에서 4입력 OR 게이트를 찾는 데 문제가 있습니다.

4개의 입력이 있는 유일한 종류의 게이트는 오른쪽 위에 표시된 7420 NAND 게이트입니다.

아래 그림과 같이 입력을 NAND 게이트로 반전하여 4입력 NAND 게이트를 4입력 OR 게이트로 만들 수 있습니다. 따라서 입력을 반전하여 7420 4입력 NAND 게이트를 OR 게이트로 사용합니다.

개별 인버터를 사용하여 입력을 7420 4입력 NAND 게이트로 반전시키지 않고 SOP, minterm, 솔루션에서 요구하는 AND 게이트 대신 2입력 NAND 게이트로 구동합니다.

2입력 NAND 게이트 출력의 반전은 4입력 OR 게이트의 반전을 제공합니다.

결과는 위에 나와 있습니다. AND-OR 논리를 대체하는 NAND-NAND 논리를 사용하여 실제로 TTL 게이트로 빌드하는 유일한 실용적인 방법입니다.

관련 워크시트:

<울>산업기술

AC DC 컨버터는 AC에서 DC로의 변환 프로세스가 필요한 전자 장치에 전원을 제공합니다. 이 장치의 다양한 응용 프로그램은 근처에 있는 DC 벽면 콘센트에 액세스할 수 없는 경우 유용할 수 있습니다. 그럼에도 불구하고 이 기술을 이해하는 것은 복잡한 특성으로 인해 혼란스럽고 압도적일 수 있습니다. 이 심층 기사를 통해 이러한 장치가 달성하는 것과 작동 방식에 대해 자세히 알아볼 수 있습니다. WellPCB에서는 AC-DC 컨버터에 이상적인 애플리케이션에 대한 정보를 제공합니다. 따라서 이러한 변환기의 작동 방식과 안전하게 활용하

의심의 여지 없이 Snapmaker 2.0의 출시 많은 이야기를 주고 있습니다. 언뜻 보기에 이 기계는 평범한 3D 프린터처럼 보일 수 있지만 가장 인기 있는 3가지 기능이 포함되어 있습니다. 창작자, 제작자, 교육 센터 또는 소규모 디자인 또는 건축 스튜디오용: FDM 3D 프린팅. CNC 가공 레이저 절단 및 제판 . Snapmaker 2.0은 Snapmaker Original의 향상된 고급 버전입니다. , Kickstarter i의 요람에서 탄생한 프로젝트 n 2017년에 큰 영향을 미치고 대성공 사용자 중. 몇 가