verilog

산업 제조

D 플립플롭 입력 핀 d 뒤에 오는 순차 요소입니다. 시계의 주어진 가장자리에서.

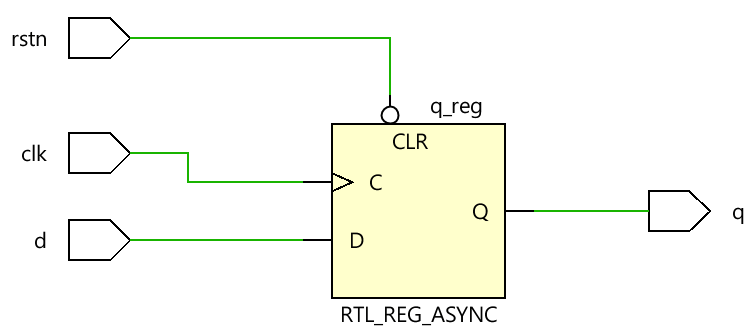

module dff ( input d,

input rstn,

input clk,

output reg q);

always @ (posedge clk or negedge rstn)

if (!rstn)

q <= 0;

else

q <= d;

endmodule

module tb_dff;

reg clk;

reg d;

reg rstn;

reg [2:0] delay;

dff dff0 ( .d(d),

.rsnt (rstn),

.clk (clk),

.q (q));

// Generate clock

always #10 clk = ~clk;

// Testcase

initial begin

clk <= 0;

d <= 0;

rstn <= 0;

#15 d <= 1;

#10 rstn <= 1;

for (int i = 0; i < 5; i=i+1) begin

delay = $random;

#(delay) d <= i;

end

end

endmodule

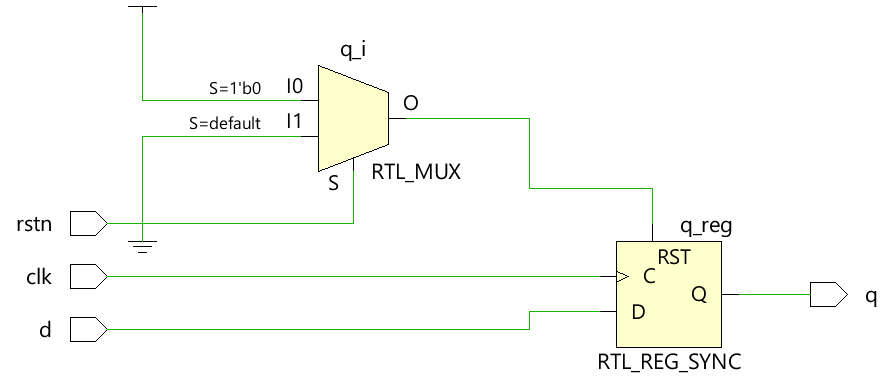

module dff ( input d,

input rstn,

input clk,

output reg q);

always @ (posedge clk)

if (!rstn)

q <= 0;

else

q <= d;

endmodule

module tb_dff;

reg clk;

reg d;

reg rstn;

reg [2:0] delay;

dff dff0 ( .d(d),

.rsnt (rstn),

.clk (clk),

.q (q));

// Generate clock

always #10 clk = ~clk;

// Testcase

initial begin

clk <= 0;

d <= 0;

rstn <= 0;

#15 d <= 1;

#10 rstn <= 1;

for (int i = 0; i < 5; i=i+1) begin

delay = $random;

#(delay) d <= i;

end

end

endmodule

verilog

Fanuc TC에서 프로그램 편집 후 재설정 CNC 기계공은 CNC 부품 프로그램을 변경하는 경우 FANUC TC cnc 제어 기능이 있는 cnc 기계(예:Gildemeister NEF 560)에서 CYCLE START를 누르기 전에 항상 RESET 버튼을 누르는 것을 기억해야 합니다.

Heidenhain TNC 640/530/410/426/430/320용 Heidenhain M 코드(기타 기능) 하이덴하인 TNC 320 하이덴하인 M 코드 M 코드 설명 M0 프로그램 실행 중지(Spindle STOP, Coolant OFF) M1 옵션 프로그램 STOP(스핀들 STOP, 절삭유 OFF) M2 프로그램 실행 중지(스핀들 정지, 냉각수 꺼짐, 블록 1로 이동, 상태 표시 지우기(기계 매개변수에 따라 다름)) M3 시계 방향으로 스핀들 ON M4 시계 반대 방향으로 스핀들 ON M5 스핀들 정지 M6