verilog

산업 제조

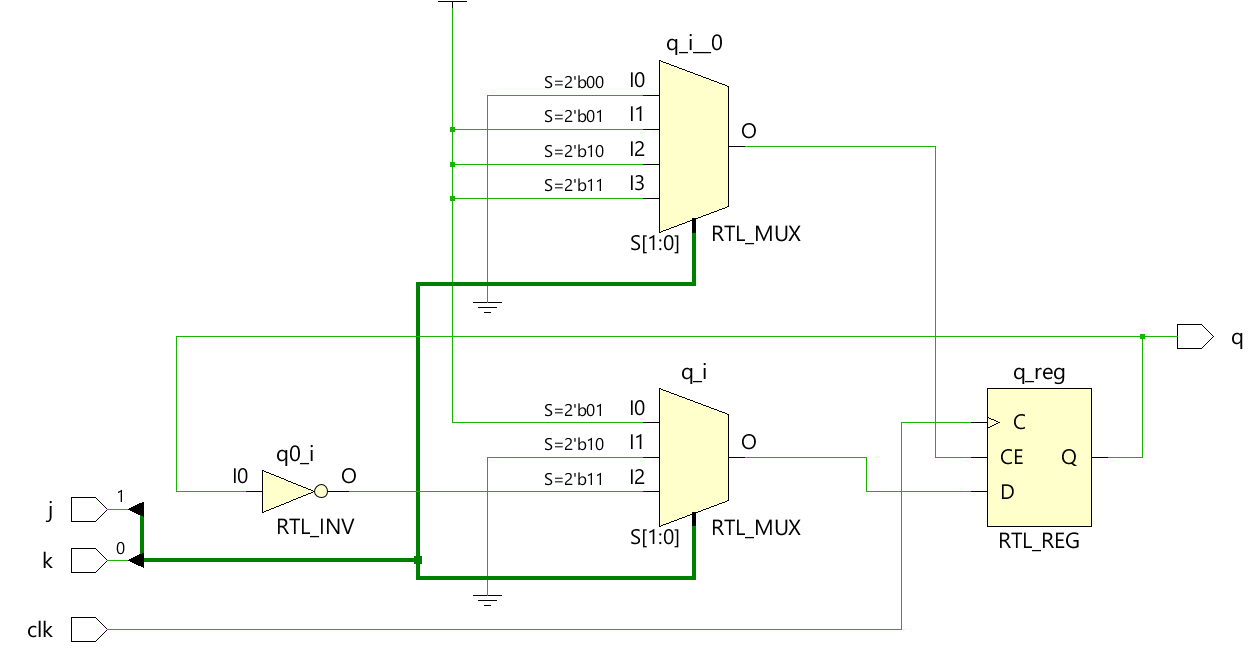

module jk_ff ( input j,

input k,

input clk,

output q);

reg q;

always @ (posedge clk)

case ({j,k})

2'b00 : q <= q;

2'b01 : q <= 0;

2'b10 : q <= 1;

2'b11 : q <= ~q;

endcase

endmodule

module tb_jk;

reg j;

reg k;

reg clk;

always #5 clk = ~clk;

jk_ff jk0 ( .j(j),

.k(k),

.clk(clk),

.q(q));

initial begin

j <= 0;

k <= 0;

#5 j <= 0;

k <= 1;

#20 j <= 1;

k <= 0;

#20 j <= 1;

k <= 1;

#20 $finish;

end

initial

$monitor ("j=%0d k=%0d q=%0d", j, k, q);

endmodule

verilog

구성품 및 소모품 Arduino Nano R3 × 1 Maxim 통합 DS3231M - ±5ppm, I2C 실시간 클록 × 1 MAX7219 드라이버가 있는 8x8 Led 매트릭스 × 1 RGB 확산 공통 음극 × 1 저항 220옴 × 2 푸시 버튼이 있는 로터리 인코더 × 1 필요한 도구 및 기계 납땜 인두(일반) 앱 및 온라인 서비스 Arduino IDE

컴퓨터, 통신 장비 및 기타 유사한 유형의 시스템에서 볼 수 있는 것과 같은 디지털 회로를 배우거나 만드는 데 관심이 있습니까? 가장 먼저 살펴볼 것은 트랜지스터 플립플롭입니다. 플립플롭의 기본 빌딩 블록은 논리 게이트이며, 이는 부울 기능을 구현하는 이상적인 전자 모델입니다. 이러한 논리 게이트에는 커패시터 및 저항과 같은 여러 구성 요소가 있을 수 있지만 주로 트랜지스터입니다. 아래에서 다양한 유형의 플립플롭 회로와 해당 배선도에 대해 자세히 설명했습니다. 프로젝트에 사용할 수 있는 방법을 알아보세요. 플립플롭이란 무엇입니까