VHDL

대부분의 VHDL 디자인은 클럭 로직을 사용합니다. , 동기 논리라고도 함 또는 순차 논리 . 클럭된 프로세스는 마스터 클럭 신호에 의해서만 트리거되고 다른 입력 신호가 변경될 때는 트리거되지 않습니다.

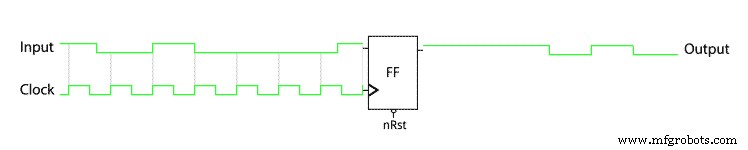

클럭 로직의 기본 구성 요소는 플립플롭이라는 구성 요소입니다. . 다양한 변형이 있으며 이 튜토리얼에서는 네거티브 리셋이 있는 포지티브 에지 트리거 플립플롭에 중점을 둘 것입니다.

플립플롭은 샘플 앤 홀드 회로로, 클록 신호의 상승 에지가 도착할 때 입력에서 출력으로 값을 복사합니다. 그런 다음 출력은 클록의 다음 상승 에지까지 또는 리셋 신호가 펄스될 때까지 샘플링된 값에서 안정적으로 유지됩니다.

이 블로그 게시물은 기본 VHDL 자습서 시리즈의 일부입니다.

클럭된 모든 프로세스는 동시에 트리거되고 한 번에 입력을 읽습니다. 동시에 마지막 반복의 결과를 출력합니다. 클록 신호는 데이터 흐름에서 타임 스텝을 효과적으로 생성합니다. 이를 통해 디자이너는 복잡하고 심층적인 논리를 쉽게 만들 수 있습니다. 그는 알고리즘의 동작을 시계 주기에서 발생하는 이벤트로 나눌 수 있습니다.

플립플롭 또는 플립플롭 배열을 레지스터라고도 합니다. , 같은 것입니다.

클럭 프로세스에 대한 감도 목록에는 일반적으로 클럭 신호만 포함됩니다. 이것은 클록된 프로세스가 클록 신호의 측면에 의해서만 트리거되기 때문이며 다른 입력 신호는 전혀 깨우지 않습니다.

다음은 동기식 재설정을 사용하여 클럭 프로세스를 생성하기 위한 템플릿입니다.process(Clk) is

begin

if rising_edge(Clk) then

if nRst = '0' then

<reset all output signals here>

else

<main logic here>

end if;

end if;

end process;

이 비디오 자습서에서는 VHDL에서 클럭 프로세스를 만드는 방법을 배웁니다.

플립플롭 testbench의 최종 코드 :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T17_ClockedProcessTb is

end entity;

architecture sim of T17_ClockedProcessTb is

constant ClockFrequency : integer := 100e6; -- 100 MHz

constant ClockPeriod : time := 1000 ms / ClockFrequency;

signal Clk : std_logic := '1';

signal nRst : std_logic := '0';

signal Input : std_logic := '0';

signal Output : std_logic;

begin

-- The Device Under Test (DUT)

i_FlipFlop : entity work.T17_FlipFlop(rtl)

port map(

Clk => Clk,

nRst => nRst,

Input => Input,

Output => Output);

-- Process for generating the clock

Clk <= not Clk after ClockPeriod / 2;

-- Testbench sequence

process is

begin

-- Take the DUT out of reset

nRst <= '1';

wait for 20 ns;

Input <= '1';

wait for 22 ns;

Input <= '0';

wait for 6 ns;

Input <= '1';

wait for 20 ns;

-- Reset the DUT

nRst <= '0';

wait;

end process;

end architecture;

플립플롭 모듈의 최종 코드 :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T17_FlipFlop is

port(

Clk : in std_logic;

nRst : in std_logic; -- Negative reset

Input : in std_logic;

Output : out std_logic);

end entity;

architecture rtl of T17_FlipFlop is

begin

-- Flip-flop with synchronized reset

process(Clk) is

begin

if rising_edge(Clk) then

if nRst = '0' then

Output <= '0';

else

Output <= Input;

end if;

end if;

end process;

end architecture;

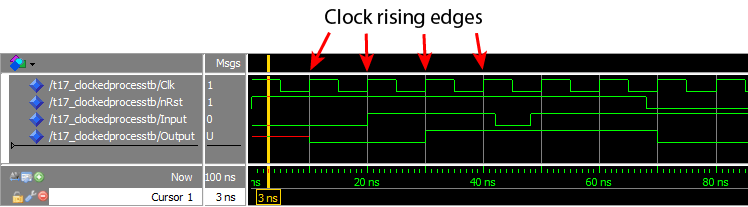

실행을 누르고 타임라인을 확대한 후 ModelSim의 파형 창:

파형에서 출력 신호가 클럭 신호의 각 상승 에지에서만 업데이트됨을 알 수 있습니다. 입력 신호는 클럭 신호가 '0'에서 '1'로 변경될 때만 샘플링됩니다. 약 45ns에서 시작하는 입력 신호의 음의 딥은 완전히 손실됩니다. 클럭의 두 상승 에지 사이에 있으므로 출력에 복사되지 않으므로 무시됩니다.

이 애니메이션은 출력이 변화하는 입력 및 클록 신호에 어떻게 반응하는지 보여줍니다.

수직선은 입력 신호가 클록의 상승 에지에 상대적인 방식을 나타냅니다.

20ns에서 시작하는 입력 신호의 하나의 양의 펄스에 특히 주의하십시오. 그것은 클록과 정확히 하나의 클록 주기와 동기적입니다. 출력은 순간적으로 반응하지 않고 한 클럭 주기만큼 지연됩니다.

내가 VHDL을 배울 때 나는 이것이 특히 이해하기 어렵다는 것을 알았다. 클럭의 상승 에지는 입력의 상승 에지와 동기화되므로 플립플롭은 어떻게 하나의 값 또는 다른 값을 선택할 수 있습니까?

시뮬레이터는 타임 스텝을 사용하여 예측 가능한 방식으로 이벤트를 모델링하고 신호는 제로 시간에 전파됩니다. 플립플롭은 출력을 업데이트할 때와 똑같은 시간 간격으로 입력을 읽기 때문에 입력의 이전 값을 보고 출력에 복사합니다.

VHDL 시간 단계에 대해 자세히 알아보기:델타 주기 설명

이 답변에 이것이 실제로 아니라는 점을 추가해야 합니다. 작동 방식. 물리적 세계에서 신호가 전파되는 데 시간이 필요합니다. 신호가 플립플롭에 언제 도착하는지 정확히 알 수 없습니다. 이러한 전파 지연은 VHDL 코드를 넷리스트로 변환하는 소프트웨어 프로세스(장소 및 경로)에 의해 자동으로 추정됩니다.

실제로 입력은 상승 클록 에지 전후에 몇 나노초 동안 안정적으로 유지되어야 합니다.

이러한 중요한 기간을 설정 및 유지 시간이라고 합니다. 다행히 이것은 일반적으로 고려해야 할 사항이 아닙니다. 순전히 클럭 로직으로 작업할 때 이러한 문제는 VHDL 코드를 넷리스트로 바꾸는 소프트웨어에 의해 처리됩니다.

if rising_edge(Clk) 프로세스가 클록의 상승 에지에서만 깨어나도록 합니다.

기본 VHDL 퀴즈 – 3부 »

또는

다음 튜토리얼로 이동 »

VHDL

변화는 그 자체로 주기이며 조직은 일생 동안 다양한 주기를 거칩니다. 프로세스 자동화, 특수 장비 도입, 중복 작업 및 이를 수행하는 사람의 간소화, 단순히 물리적 공장의 재배치 등 모든 변화는 불가피합니다. 모범 사례 통찰력 및 기술 회사인 CEB에서 준비한 변경 관리에 대한 백서가 이러한 관점을 증명합니다. 이 보고서는 평균적인 조직이 지난 3년 동안 5가지 중요한 변화를 경험했으며 조직의 73%가 향후 3년 동안 더 많은 변화 이니셔티브를 기대한다고 주장합니다. 이 백서는 다음과 같은 일반적인 기업 변경 사항을 식별합니다

3D 프린팅에는 항상 사용자에 따라 달라지는 일련의 요소가 있습니다. , 인쇄가 만족스럽거나 실패하는 경우가 많습니다. 각 사용자가 각 3D 프린트에서 사용하는 프린트 프로필에 모든 요소가 수집됩니다. 3D FDM 인쇄 프로필에서 무한한 수의 매개변수를 수정할 수 있습니다. :프린팅 온도 및 속도, 내부 및 외부 부품 제조 방법 및 3D 프린팅에 영향을 미치는 나머지 모든 매개변수. 이러한 이유로 가장 중요한 정보는 인쇄 프로필을 만들 때 아래에서 설명합니다. 고려할 측면 인쇄 매개변수를 수정하기 전에 직접적으로 영향을 미치