RTOS 공개 시리즈 보기 이 기사에서는 세마포어를 계속 살펴봅니다. 세마포어 유틸리티 서비스 Nucleus RTOS에는 세마포어와 관련된 유틸리티 기능을 제공하는 네 가지 API 호출이 있습니다. 세마포어 재설정, 세마포어에 대한 정보 반환, 애플리케이션의 세마포어 수 반환, 애플리케이션의 모든 세마포어에 대한 포인터 반환. 이 중 처음 세 가지는 Nucleus SE에서 구현됩니다. 세마포 재설정 이 API 호출은 세마포어를 사용되지 않은 초기 상태로 복원합니다. 이 API 기능은 다른 커널 개체에 사용할 수 있는 기능

RTOS 공개 시리즈 보기 사서함은 이전 기사에서 소개되었습니다. 신호 다음으로 Nucleus SE가 지원하는 태스크 간 통신의 두 번째로 간단한 방법일 것입니다. 작업 간에 간단한 메시지를 전달할 수 있는 저비용이지만 유연한 수단을 제공합니다. 사서함 사용 Nucleus SE에서 사서함은 빌드 시 구성됩니다. 응용 프로그램에 대해 최대 16개의 사서함이 구성될 수 있습니다. 사서함이 구성되어 있지 않으면 사서함과 관련된 데이터 구조 또는 서비스 호출 코드가 애플리케이션에 포함되지 않습니다. 사서함은 단순히 ADDR 유형의

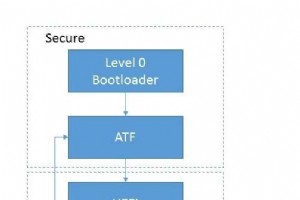

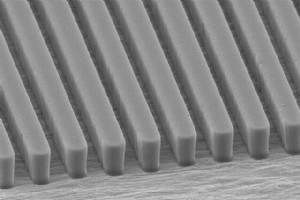

ARMv8 프로세서 아키텍처는 2011년 출시 이후 모바일 기기 시장에 널리 보급되었습니다. ARM Limited CEO의 예측에 따르면 이 세대의 프로세서는 2020년까지 세계 시장 점유율이 최대 25%에 달할 것이라고 합니다. 소프트웨어 지원이 확립되고 기능과 일반 역사적으로 형성된 기반 시설의 원칙. 시장의 서버 부문에서는 근본적으로 다른 상황이 관찰됩니다. X86 기반 서버는 오랫동안 이 영역을 지배해 왔으며 ARMv8은 이제 막 그 길을 찾고 있습니다(특정 비즈니스 부문에만 해당). ARM에 대한 이 시장의 참신함과 승인

편집자 주:우리의 좋은 친구 Max가 전자 계산기와 해결사에 대한 제안을 찾고 있습니다. 너무 크거나 너무 작은 것은 없습니다. EEWeb.com의 도구 목록에 포함할 가치가 있다고 생각하는 것을 그에게 알려주십시오. 이따금 예상치 못한 햇살이 구름을 뚫고 내 삶을 밝게 비춰줍니다. 그런 사건이 방금 일어났습니다. 얼마 전에 이 말을 쓰면서 권위의 속옷을 입고 권력의 복도를 걷는 사람들로부터 정보를 얻었습니다. 우리가 EEWeb의 전자 계산기 컬렉션에 추가할 것입니다. (출처:pixabay.com) 유일한 단

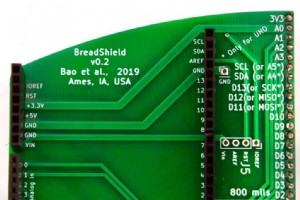

다양한 프로젝트를 위한 크라우드펀딩 캠페인을 시작한 사람들로부터 엄청나게 많은 이메일을 받았습니다. 이것은 아마도 내가 가끔 크라우드 펀딩의 물에 발을 담그고 내가 특히 내 취향을 바꾼 프로젝트에 대한 여러 칼럼을 게시했다는 사실 때문일 것입니다. 이러한 프로젝트 중 일부는 크고 복잡하며 비용이 많이 드는 반면, 다른 프로젝트는 작고 저렴하며 쉽게 머리를 감쌀 수 있습니다. 특히 Doh! 난 왜 그 생각을 못했지?” 그러고 보니 Forrest Bao라는 사람이 보낸 이메일을 받았는데, 그 내용은 다음과 같습니다. 안녕하세요,

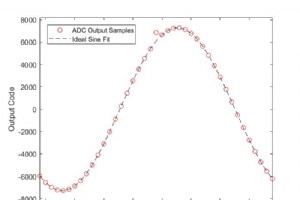

고속 ADC(아날로그-디지털 변환기)의 샘플링 속도가 증가함에 따라 ADC 출력 데이터의 코드 오류(스파클 코드라고도 함) 문제도 증가했습니다. 코드 오류는 정의된 임계값을 초과하는 ADC의 출력 코드 오류로 정의됩니다. 임계값은 가장 일반적으로 오류가 ADC 잡음의 예상 진폭을 초과하여 잡음이 있을 때 오류를 쉽게 식별할 수 있는 수준으로 정의됩니다. 이 오류 임계값 정의를 설명하는 또 다른 방법은 ADC의 가정된 가우스 분포 잡음이 주어진 경우 해당 진폭의 예상 확률을 초과하는 확률로 오류 진폭이 발생한다는 것입니다. 그림

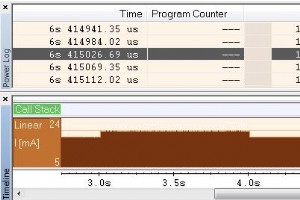

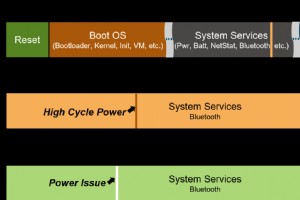

제 마지막 게시물인 Arm Cortex-M 저전력 모드 기본 사항에서 모든 Arm Cortex-M 프로세서에서 찾을 수 있는 저전력 모드의 기본 사항과 WFI 및 WFE 명령을 활용하여 프로세서를 배치하는 방법을 살펴보았습니다. 자다. 하지만 실제로 남아 있는 질문은 이러한 저전력 모드가 실제 마이크로컨트롤러에서 어떻게 구현되고 이러한 모드가 임베디드 시스템에 어떤 영향을 미칠까요? 이 게시물에서는 마이크로컨트롤러를 절전 모드로 전환하는 방법과 에너지 소비량을 확인하는 방법을 자세히 살펴보겠습니다. 저전력 모드 실험 저전력

전력에는 비용이 드는 경향이 있습니다. 높은 전력 비용이 많이 듭니다. 액튼 경의 유명한 인용문을 다소 강제로 적용한 것은 반도체 설계와 전력 소비의 두 가지 중요한 측면을 포착합니다. 시간 경과에 따른 평균 전력 소비를 살펴보면 전력 소모가 높은 칩에 높은 비용이 발생한다는 것이 분명합니다. 휴대용 장치에서 더 많은 전력은 더 크고 더 비싼 배터리를 의미하거나 배터리 수명을 단축시킵니다. 또한, 더 많은 전력은 결과적인 열을 발산하기 위해 더 고급화되고 더 비싼 패키징을 의미합니다. 이 세 가지 요소는 또한 제품 가격, 이윤, 시

최근 몇 년 동안 우리는 더 작은 패키지, 새로운 폼 팩터, 더 낮은 전력 소비 및 임베디드 신호 처리, 센서, 이미징 인터페이스 및 전력 관리 구성요소를 포함한 향상된 기능을 요구하는 새로운 전자 애플리케이션의 확산을 보아왔습니다. 유연한 기판. 이러한 경향은 기존의 PCB 기술에 수많은 도전을 제기하고 있습니다. 이전에는 평평한 표면의 단단한 PCB가 주류를 이루었지만 스마트 워치, IoT 장치 및 기타 소형 시스템의 출현으로 인해 계속 줄어들고 있는 패키지 크기의 윤곽에 맞게 설계된 첨단 소형 PCB 개발이 박차를 가했습니다.

디자인이 있었던 전자 디자인의 여명기부터 버그가 있었습니다. 그러나 버그가 있었던 위치에는 필연적으로 디버그가 있었고 결함, 버그 및 오류가 있는 장대한 레슬링 경기에 참여하여 어느 것이 우세하고 얼마나 철저하게 결정되는지를 결정했습니다. 여러 면에서 디버그 기술의 발전은 디자인의 모든 측면만큼 매력적입니다. 하지만 스포트라이트를 받는 경우는 거의 없습니다. 디버그는 단순한 자극-응답-관찰 접근 방식에서 점점 더 복잡해지는 설계를 처리하기 위해 고안된 정교한 도구, 장비 및 방법론으로 발전했습니다. 이제 2017년, 우리는 기능적

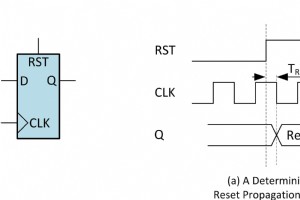

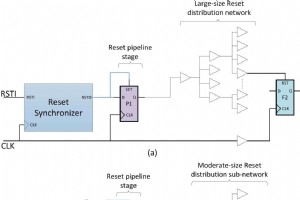

비동기식 리셋과 동기식 로직 클록 간의 조정 부족은 전원 공급 시 간헐적인 오류로 이어집니다. 이 일련의 기사에서는 비동기식 재설정의 요구 사항과 과제에 대해 논의하고 ASIC 대 FPGA 설계를 위한 고급 솔루션을 살펴봅니다. 비동기식 리셋은 일반적으로 전원이 켜진 후 동기식 회로를 알려진 상태로 만들기 위해 VLSI 설계에 사용됩니다. 비동기식 리셋 해제 동작은 리셋과 클럭 간의 가능한 경합으로 인한 동기화 실패를 제거하기 위해 동기식 로직 클럭 신호와 조정되어야 합니다. 이러한 조정이 부족하면 전원을 켤 때 간헐적인 오류가

비동기식 리셋과 동기식 로직 클록 간의 조정 부족은 전원 공급 시 간헐적인 오류로 이어집니다. 이 일련의 기사에서는 비동기식 재설정의 요구 사항과 과제에 대해 논의하고 ASIC 대 FPGA 설계를 위한 고급 솔루션을 살펴봅니다. 비동기식 리셋은 일반적으로 전원이 켜진 후 동기식 회로를 알려진 상태로 만들기 위해 VLSI 설계에 사용됩니다. 비동기식 리셋 해제 동작은 리셋과 클럭 간의 가능한 경합으로 인한 동기화 실패를 제거하기 위해 동기식 로직 클럭 신호와 조정되어야 합니다. 이러한 조정이 부족하면 전원을 켤 때 간헐적인 오류가

인터넷에는 수많은 실시간 운영 체제(RTOS)가 있습니다(작은 목록을 보려면 여기를 클릭하십시오). 그러나 이러한 오퍼링 중 상당수는 현재 중단되었거나 유지 관리되지 않는 프로젝트입니다. 나머지 제품 중 대부분은 하나의 마이크로컨트롤러 또는 하나의 마이크로컨트롤러 제품군만 지원합니다. 더 많은 것을 필터링하면 여러 마이크로컨트롤러를 지원하는 경우에도 일반적으로 USB, 이더넷, Wi-Fi, 6LoWPAN, 그래픽 LCD, SD 카드, FAT 파일 시스템, CAN 버스 등 필요한 모든 기능이 없다는 것을 알 수 있습니다. RS485

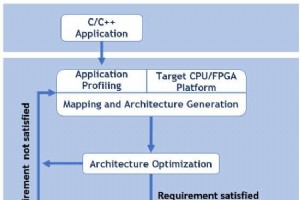

최근에 Brian Bailey는 CPU와 FPGA 지원이라는 두 부분으로 구성된 기사를 작성하는 라운드 테이블을 조직했습니다. . 전문가들은 FPGA와 CPU를 기반으로 하는 시스템 설계의 진화하는 현실에 대해 논의했습니다. 이 토론에서는 디자인 흐름의 최근 개발과 새로운 기술을 사용하여 소프트웨어 개발자가 CPU 및 FPGA 플랫폼의 시장 출시 시간을 단축하는 데 어떻게 도움이 되는지 설명합니다. 소개 인공 지능(AI)에 대한 관심 증가, 연결된 개체(IoT)의 출현, 데이터 센터 가속화 추세를 살펴보면 모두 다음과 같은 질문을

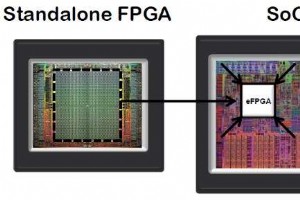

저는 Achronix에서 나오는 기술에 오랫동안 관심이 있었습니다. 2004/2005년경 비동기식 FPGA 패브릭으로 처음 관심을 끌었습니다. 결국 이것은 2GHz에서 클럭되는 동기식 FPGA와 동일한 속도에 도달했지만(만약 그러한 짐승이 있는 경우) 제한된 수의 알고리즘 및 데이터 흐름 애플리케이션에만 적용할 수 있었습니다. 2013년 Achronix는 타겟 애플리케이션에 중점을 둔 Speedster라는 고성능, 고밀도 독립형 FPGA 제품군을 출시했습니다. Achronix 제품 포트폴리오는 고성능, 임베디드 FPGA(eFPGA

히어러블(Hearable)과 진정한 무선 스테레오 이어버드가 인기를 얻고 있지만 아직 그 잠재력을 완전히 발휘하려면 멀었습니다. 이 작은 장치는 사람들이 주변 환경과 상호 작용하는 방식을 변화시켜 일상 생활에 향상된 청각 기능, 즐거움 및 안전을 추가할 수 있습니다. 무선 음악 경험을 위한 시장 채택이 이미 진행 중입니다. 가전 제품에서 액션 카메라에 이르기까지 더 많은 장치가 음성으로 활성화됨에 따라 이 작은 이어버드도 음성 인터페이스의 지능이 지속적으로 향상되고 있습니다. 그러나 표준화의 부족과 여러 기술을 하나의 완벽한 패

편집자 주:무선 설계는 연결된 장치 개발을 위한 최선의 계획을 방해할 수 있습니다. 특히 부적절하게 설계된 안테나 급전선은 테스트 중 개발이 끝날 때까지 발견하기 어려울 수 있습니다. 다음은 Wi-Fi 성능을 개선하는 데 필요한 접지된 동일 평면 도파관 RF 급전선의 설계를 개선하는 데 사용되는 접근 방식을 심층적으로 살펴보는 EEWeb의 친구들이 작성한 멋진 기사입니다. 최근 Arira Design의 Signal Integrity Group은 클라이언트 보드에서 Wi-Fi 하위 시스템의 성능을 개선하기 위해 기존 5GHz G

지난 몇 년 동안 자동 음성 인식(ASR)의 상당한 발전으로 인해 음성을 주요 인터페이스로 사용하는 장치와 응용 프로그램이 많이 생겼습니다. IEEE 스펙트럼 잡지는 2017년을 음성 인식의 해로 선언했습니다. ZDNet은 CES 2017에서 음성이 차세대 컴퓨터 인터페이스라고 보고했습니다. 그리고 많은 다른 사람들이 비슷한 견해를 공유합니다. 그렇다면 음성 인터페이스의 발전과 관련하여 우리는 어디에 있습니까? 이 게시물은 음성 인터페이스와 이를 가능하게 하는 기술의 현재 상태를 조사할 것입니다. 당신과 대화할 수 있는 기기가 몇

경력을 쌓는 동안 정말 흥미로운 프로젝트를 위해 여러 FPGA 디자인을 개발하는 일에 참여했습니다. 슬프게도, 나는 또한 잘못 길을 잃은 여러 FPGA 디자인을 구출하는 데 참여했습니다. 이러한 문제 설계에 대해 작업하면서 대상 응용 프로그램과 개발 팀 구성원이 다르지만 설계는 첫 번째 엔지니어가 첫 줄을 작성하기 전에 앉아도 실패할 수밖에 없는 몇 가지 공통점을 공유한다는 것이 분명해졌습니다. 의 HDL 코드. (출처:pixabay.com) 이를 염두에 두고 이 프로젝트를 구하는 과정에서 관찰한 5가지 일반적인 문제를 해결해

5세대 모바일 네트워크 또는 무선 시스템을 의미하는 5G라는 용어가 요즘 점점 더 많이 등장하고 있습니다. 이르면 2020년에 초기 배포에 대한 이야기가 있습니다. 덜 언급된 것은 5G 표준이 여전히 고려되고 정의되고 있으며 많은 측면이 여전히 유동적이라는 사실입니다. 그렇다면 5G는 무엇을 수반하는가? NGMN(Next Generation Mobile Networks) Alliance는 5G 표준이 충족해야 하는 다음 요구 사항을 정의합니다. 수만 명의 사용자를 위한 초당 수만 메가비트의 데이터 속도. 수도권 지역의 경우 초당

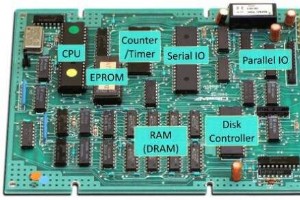

임베디드