나노물질

우리는 920°C에서 수정된 Bridgman 기술을 사용하여 이중 밀봉 석영 앰풀에서 성장한 p형 주석 모노셀레나이드(SnSe) 단결정을 보고합니다. X선 분말 회절(XRD) 및 에너지 분산 X선 분광법(EDX) 측정은 성장된 SnSe가 단결정 SnSe로 구성되어 있음을 명확하게 확인합니다. 벌크 단결정의 박리에 의해 제조된 다층 SnSe 나노플레이크의 전기적 수송은 SiO2에 Au 및 Ti 접점이 있는 백 게이트 전계 효과 트랜지스터(FET) 구조를 사용하여 수행되었습니다. /Si 기판은 다층 SnSe 나노플레이크가 SnSe 나노플레이크 표면의 Sn 공석으로 인해 p형 반도체 특성을 나타냄을 보여줍니다. 또한, 70-90nm 두께의 SnSe 나노플레이크 FET에서 강한 캐리어 스크리닝 효과가 관찰되었습니다. 또한, 다층 SnSe 나노플레이크 기반 FET에 대한 금속 접촉의 효과는 Ti/Au 및 Au 접촉과 같은 두 가지 다른 금속에서도 논의됩니다.

<섹션 데이터-제목="배경">과도 금속 칼코겐화물은 다양한 광학 및 광전자 응용 분야에 사용하기에 적합하도록 만드는 다양한 광학 밴드갭을 제공합니다[1]. PbTe, PbSe 및 Bi2를 포함한 이러한 재료의 박막 Se3 [2], 적외선 광전자 장치, 방사선 검출기, 태양 전지, 메모리 장치 및 홀로그램 기록 장치 [3,4,5,6,7,8]에서의 장래 사용으로 인해 상당한 주목을 받았습니다. 주석 모노 및 디셀렌화물(SnSe 및 SnSe2 ) 광전자 응용 분야에 유리한 높은 흡수 계수로 인해 연구의 각광을 받았습니다. 또한 이러한 재료는 열전 응용 분야에서 사용하기에 유망합니다[9,10,11,12,13,14,15,16,17,18,19,20,21,22,23,24]. 주석 모노셀레나이드(SnSe)는 ~0.9eV에 가까운 간접 허용 전이에 대한 밴드갭과 ~1.2eV에 가까운 직접 허용 전이에 대한 밴드갭이 있는 p형 반도체인 반면 주석 이셀레나이드(SnSe2 )는 n형 반도체이다[6]. SnSe의 결정 구조는 사방정계이며 단위 셀 매개변수는 a =11.496 Å, b =4.151 Å 및 c =4.444 Å; 이 사방정계 구조는 SnSe2의 융점보다 낮은 고온에서 정방정 구조로 변형됩니다. [25].

최근에, 대면적 공통 백 게이트를 갖는 전계 효과 트랜지스터(FET)를 포함하는 Sn 기반 이진 칼코게나이드 및 디칼코게나이드 전기 장치가 광범위하게 조사되었습니다. 특히 Sn 디칼코게나이드 기반 FET의 특성화에 많은 진전이 있었습니다[26, 27]. 2016년 Pei et al. 보고된 몇 층 SnSe2 ~10 4 의 높은 온/오프 비율을 보여주는 FET 고분자 전해질의 상부 캡핑 층으로 [27]. Guo et al. 또한 고이동성 소수층 SnSe2를 보고했습니다. 두께가 ~8.6nm인 FET[28]. 이전 연구에서 얇고 낮은 캐리어 농도의 SnSe 필름이 SnSe2의 높은 이동도와 전류 온/오프 비율을 생성함을 확인했습니다. FET. SnSe2를 활용하려는 이러한 노력에도 불구하고 그러나 단결정에서 박리하여 제조된 SnSe FET의 전기적 특성은 보고되지 않았습니다. 소수 및 다층 SnSe2에서 전기 전송의 상세한 특성화 단일 SnSe 결정은 ~7835cm 2 의 높은 캐리어 이동도를 나타낼 것으로 예상되기 때문에 SnSe 나노플레이크와 같은 주석 칼코겐화물의 전기적 수송 특성을 평가하기 위해 플레이크를 수행해야 합니다. /V s [29].

이 연구에서 우리는 수정된 Bridgman 방법을 사용하여 성장한 단결정 SnSe를 특성화했습니다. 벌크 단결정으로부터 박리에 의해 제조된 다층 SnSe 나노플레이크 FET의 전기 수송은 SiO2에서 백 게이트 FET 구조를 사용하여 처음으로 특성화되었습니다. /Si 기판. 더욱이, 다층 SnSe 나노플레이크 기반 FET에 대한 금속 접촉의 효과는 접촉 금속의 일함수가 쇼트키 장벽을 통한 정공 캐리어의 전도를 결정하기 때문에 두 가지 다른 유형의 접촉(Ti/Au 및 Au)에 대해서도 연구되었습니다. 금속-SnSe 나노플레이크 인터페이스.

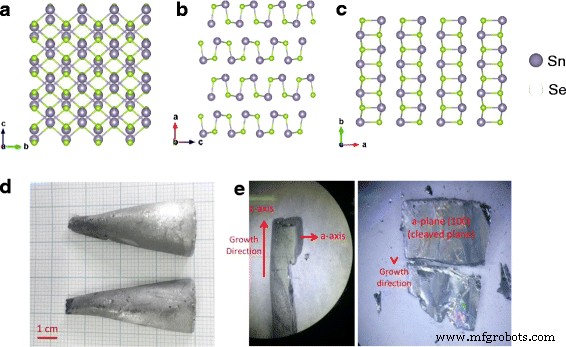

SnSe는 상온에서 층상 사방정계 결정 구조를 갖는다[24]. 그림 1a–c는 a를 따라 SnSe 결정 구조의 투시도를 보여줍니다. , b , 및 c 축 방향. 그림 1c에서 볼 수 있듯이 2개의 원자층을 가진 SnSe 슬라브는 홈이 있는 반면, (100) 평면을 따라 결정의 쉬운 분열이 발생합니다(그림 1b). 단일 SnSe 결정은 이전에 설명한 대로 수정된 브리지만 방법을 사용하여 성장되었습니다[24, 30]. Sn(99.999% 쇼트, Alfa Aesar) 및 Se(99.999% 분말, Alfa Aesar)의 화학량론적 양은 먼저 이중 밀봉 석영 앰플의 잉곳(~20g)으로 용융되었습니다. 원료를 천천히 500°C로 가열하고 10시간 동안 방치한 다음, 노를 끄기 전에 920°C에서 추가로 10시간 동안 유지했습니다. 얻어진 잉곳을 분말로 분쇄하고, 원추형 석영관에 채우고, 진공으로 하고, 화염 밀봉하였다. 이 대전된 원뿔 모양의 석영관을 더 큰 석영관에 넣었습니다. 외부 튜브는 폭발과 산화를 방지하기 위해 기체 Ar을 채운 다음 화염 밀봉했습니다. 장입된 석영 앰플은 수직관로에서 온도 구배가 가장 큰 위치에 놓았다. 수직 관로를 20시간 동안 970°C로 천천히 가열하고 10시간 동안 유지한 다음 0.5°C/h의 속도로 830°C까지 냉각했습니다. 퍼니스를 추가로 24시간 동안 830°C에서 유지한 다음 퍼니스를 끄기 전에 100°C/h의 속도로 500°C로 냉각했습니다.

<그림>

아 –ㄷ a에 따른 SnSe 결정의 결정 구조 -, b - 및 c -축 방향. d 성장한 단결정 SnSe의 사진. 이 a를 따라 절단된 SnSe 결정의 사진 -축(100) 평면. SnSe 단결정의 쪼개진 평면(100)의 평면도(오른쪽 이미지 d 후 )

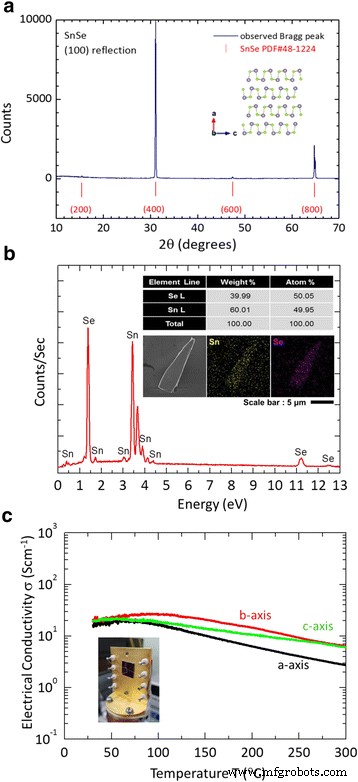

원뿔 모양의 SnSe 결정(직경, 30mm, 길이, 70mm)이 얻어졌으며 그림 1d-e에 나와 있습니다. 얻어진 결정은 석영 앰플에서 결정을 추출하는 과정에서 크랙이 발생하여 두 조각으로 나뉘었다(Fig. 1d). 성장한 SnSe 결정의 품질은 Cu Kα가 포함된 분말 X선 회절계(XRD, New D8-Advance, Bruker-AXS, Germany)를 사용하여 확인했습니다. (λ =1.5406 Å). 그림 2a는 사방정계 SnSe에 대한 전력 회절 파일(PDF) 48–1224의 XRD 패턴과 결정학적 a에 대한 패턴을 보여줍니다. SnSe 결정의 쪼개진 평면(100)에 수직인 축. 그림 2a에서 볼 수 있듯이 단결정 SnSe의 XRD 패턴은 공간군 Pnma를 갖는 단상 사방정계 결정을 강력하게 시사합니다. [31], (h00) 반사로 강한 선호 방향을 나타내며 이전 보고서 [32]와 잘 일치합니다. 또한, 2θ =에서 (400) 및 (800) 피크가 지배적이었습니다. 그림 2a [33]에서와 같이 각각 31.081° 및 64.818°입니다. 그림 2b에서 볼 수 있듯이 에너지 분산 X선 분광법(EDX)은 Sn:Se 원자 비율이 1:1임을 나타내어 Sn과 Se의 화학량론적 비율을 확인했습니다(그림 2b 삽입). 그림 2b의 삽입은 또한 90nm의 장치 두께를 가진 SnSe 나노플레이크 FET의 주사 전자 현미경(SEM) 이미지와 EDX 매핑을 보여줍니다. 이 결과는 이전 보고서[24, 33]와 잘 일치합니다. 또한 기존의 4점 프로브 방법을 사용하여 30~300K 범위의 온도에서 단결정 SnSe(그림 2b 삽입)의 전기 전도도를 측정했습니다. 그림 2c는 세 가지 다른 결정학적 방향에 따른 SnSe 단결정의 온도 의존적 전기 전도도를 보여주며, 이는 서로 다른 축 방향을 따라 SnSe의 서로 다른 정공 이동도로 인해 유사한 온도 의존적 거동과 이방성 거동을 나타냅니다. 그림 2c와 같이 b 방향의 전기 전도도는 - 및 c -300K에서 축은 ~6.00S cm −1 로 결정되었습니다. , 이는 a보다 ~2.2배 더 큽니다. -축(~2.7 S cm −1 ). 이 결과는 단결정 SnSe [24]에 대한 이전 결과와 잘 일치합니다. 그림 2c에서 단결정 SnSe의 온도 의존적 전기 전도도는 반도체 범위(30–100K)와 금속 범위(>100–300K)에 대해 표시됩니다. 100K 이상에서 성장한 SnSe 결정은 이전 관찰과 일치하는 금속 수송 거동을 나타냈습니다[24].

<사진>

아 명확한 (h00) 회절을 보여주는 SnSe 단결정의 XRD 패턴. ㄴ SnSe 단결정의 EDX 스펙트럼. 삽입 Sn과 Se의 원자비에 대한 자세한 정보를 보여줍니다. 삽입 장치 두께가 90nm인 SnSe 나노플레이크 FET의 SEM 이미지 및 EDX 매핑을 보여줍니다. ㄷ 4점 프로브 방법을 사용하여 측정한 30~300K 범위의 온도에 대한 SnSe 단결정의 온도 종속 전기 전도도

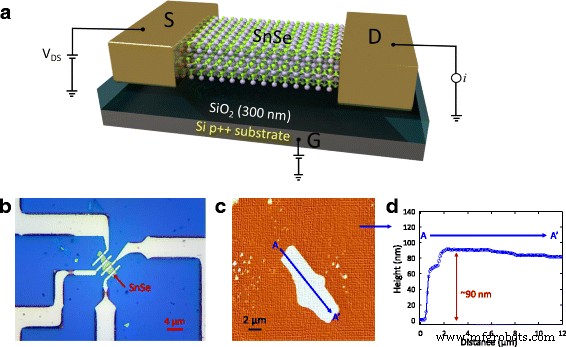

SnSe FET 소자는 다음과 같이 제작되었다. 먼저 SnSe 나노플레이크를 300nm 두께의 SiO2 위에 기계적으로 박리했습니다. /p

++

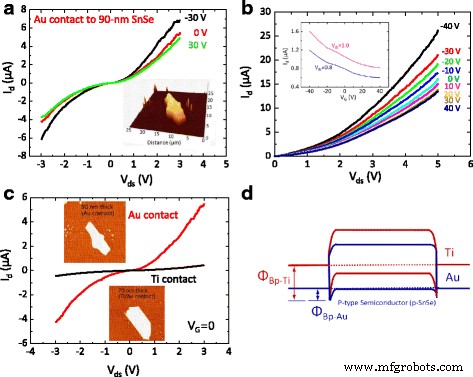

잘 알려진 스카치 테이프 방법을 사용하여 (100) 평면에서 쉽게 절단되는 단일 SnSe 결정의 Si 기판(그림 1e) [26, 27, 34]. 준비된 개별 SnSe 나노플레이크 FET의 전기 전송 측정은 백 게이트 FET 구성에서 실온에서 수행되었습니다. 그림 3a는 대면적 백 게이트가 있는 SnSe 나노플레이크 기반 FET 장치를 개략적으로 보여줍니다. 이 연구에서 2개의 SnSe 나노플레이크(70nm 및 90nm 두께의 SnSe 나노플레이크)가 SiO2 위에 준비되었습니다. /Si 기판. SnSe FET는 표준 전자빔 리소그래피 방법을 사용하여 제작된 후 두 가지 유형의 금속화, 즉 Au(두께, 100nm) 및 Ti/Au(두께, 10/100nm)가 SnSe 나노플레이크의 옴 접촉으로 간주되었습니다. 금속화 공정 전에 나노플레이크 표면의 폴리머 및 산화물 잔류물을 제거하기 위해 완충 산화물 에칭(BOE)을 수행했습니다. 그림 3b는 장치 두께가 90nm인 SnSe 나노플레이크 FET의 광학 이미지를 보여줍니다. SnSe 나노 플레이크의 두께는 실온에서 원자력 현미경(AFM)을 사용하여 측정되었습니다(그림 3c-d). 그림 3b와 그림 2b의 삽입도에서 볼 수 있듯이 제작된 90nm 두께의 SnSe FET는 채널 길이(L ) 5μm 및 너비(W ) 4.71μm, 70nm 두께 SnSe FET L 5μm 및 W 6μm였습니다. 모든 전류-전압(I -V ) 특성은 상온에서 전기적으로 차폐된 프로브 스테이션에서 반도체 매개변수 분석기(HP 4155C, Agilent Technologies, USA)를 사용하여 측정되었습니다. 그림 4a는 드레인 전류(I d ) 게이트 전압의 함수(V g ), 90nm 두께 SnSe 나노플레이크의 경우 소스-드레인 전압(V ds ) -30, 0, 30V의 실온에서 이는 이전에 보고된 바와 같이 주로 Sn 공석에 기인하는 명확한 p형 반도체 거동을 나타냅니다[15, 16, 22, 24, 35,36,37 ,38,39]. 그림 4a의 결과는 높은 일함수를 가진 금속성 AU가 SnSe 나노플레이크에서 약한 옴 접촉을 형성할 것으로 예상된다는 것을 의미하며, 이는 SnSe 나노플레이크의 전도대에 대한 쇼트키 장벽이 더 낮음을 나타냅니다. 다른 금속의 일함수에 대한 더 자세한 논의는 나중에 제공될 것입니다. 그림 4b는 I를 보여줍니다. d 대 V ds 다른 V g , −40–40V 범위, 10V 단계로. 그림 4b에서 정공 이동도(μ p )는 ~2.7cm

2

로 결정됩니다. /V, μ에서 가져옴 p =t m [엘 ⁄ (화장실 소 V ds)], 여기서 t m 트랜스 컨덕턴스(=dI d /dV g =2.89 × 10

− 8

A /V ), L 길이(~5.1μm), W 너비(~4.75μm), V ds SnSe FET의 드레인-소스 전압(~1 V), C 소 (=ε r ε 0 /d =11.5nF/cm

2

) ε r (유전율) 3.9 및 d (산화층의 두께) 300nm는 후면 게이트 SnSe 나노플레이크 FET의 단위 면적당 커패시턴스입니다. 기계적으로 박리된 SnSe 나노플레이크 FET의 평가된 정공 이동도는 에피택셜 SnSe 박막(~60cm

2

/V s) Se가 풍부한 타겟을 사용하여 MgO 기판에 펄스 레이저 증착으로 준비했습니다[40]. 그러나 여기서 얻은 값은 단결정 SnSe 나노플레이트(~1.5cm

2

/V s) [33]. 이러한 상대적으로 낮은 정공 이동성은 SnSe 표면의 Sn 공석으로 인한 강한 포논 산란과 Au 금속-SnSe 나노플레이크 계면의 상대적으로 높은 쇼트키 장벽 때문일 수 있습니다.> <그림>

아 SiO2에서 기계적으로 박리된 SnSe 나노플레이크 FET의 개략도 /p ++ Si 기판. ㄴ 전기 전송 측정에 사용된 제조된 SnSe 나노플레이크 FET의 광학 이미지. ㄷ SiO2에 있는 SnSe 나노플레이크의 AFM 이미지 /Si 기판. d FET 장치의 두께 추정 및 제작을 위한 SnSe 나노플레이크의 AFM 높이 프로파일

<그림>

아 드레인 전류(I d ) 인가된 소스-드레인 전압의 함수(V ds ), 게이트 전압(V) g ) -30, 0, 30V의 90nm 두께 SnSe 나노플레이크 FET의 경우 실온에서 ㄴ 나 d 대 V ds V를 위해 g 90nm 두께의 SnSe 나노플레이크 FET의 경우 10V 단위로 -40~40V 범위입니다. 삽입 나를 보여줍니다 d 대 V g V를 위해 ds 실온에서 측정한 0.8 및 1.0V의 ㄷ 나 d 대 V ds V 편향 없이 g (=0) SnSe 나노플레이크 FET의 Au 및 Ti 접촉. 삽입 SnSe 나노 플레이크의 AFM 스캔 이미지를 보여줍니다. d p형 SnSe 반도체에서 Au와 Ti 두 금속의 에너지 밴드 다이어그램 도식

또한, 우리는 I의 공핍 영역에서 컨덕턴스의 약한 게이트 튜닝을 관찰했습니다. d 대 V ds 곡선(그림 4c) 및 낮은 전류 온/오프 비율(V에서 ~2 ds Au 금속 접점이 있는 p-SnSe 나노플레이크 FET에서 1V, 그림 4c의 삽입. SnS FET(두께, ~50-80nm)[43], ~15.8nm 두께의 SnSe 나노플레이트[33], ~80 -nm 두께의 MoS2 [44] 및 ~84nm 두께의 SnSe2 [26]. 이러한 거동은 차폐 길이보다 두꺼운 두께를 가진 FET 장치에 표면 전도성 표면층이 존재하기 때문에 유한 캐리어 차폐 길이 효과로 설명될 수 있습니다. \( \left(\sqrt{\varepsilon {K}_B T}{e }^2 p\right) \), 여기서 ε , 케이 나 , 및 p 는 각각 반도체의 유전 상수, 볼츠만 상수, 정공 캐리어 밀도 [43]입니다.

금속 접촉은 2D FET 장치의 특성을 결정하는 중요한 요소입니다[45]. SnSe에 대한 금속의 일함수의 영향을 결정하기 위해 우리는 SnSe 나노플레이크의 금속 접점으로 Au(일함수, ~5.1eV)와 Ti(일함수, ~4.3eV)를 고려했습니다. 그림 4c는 일반적인 I를 보여줍니다. d 대 V ds 게이트 변조 없는 곡선(V g =0) Au 및 Ti 접점이 있는 SnSe 나노플레이크 FET의 경우 Au(~0.56MΩ)에 비해 Ti(~15.4MΩ)의 전체 저항이 더 높음을 나타냅니다. 따라서 금속-SnSe 계면의 쇼트키 장벽은 Ti의 경우 더 높습니다(그림 4c). 이 동작은 Ti 접점이 있는 모든 SnSe FET에서 항상 관찰됩니다. 그림 4d와 같이 금속의 일함수가 감소함에 따라 홀에 대한 쇼트키 장벽의 높이는 증가한다. 따라서 일함수가 큰 Pd, Au 및 Pt와 같은 금속은 p-SnSe 나노플레이크 FET의 옴 접촉으로 적합할 수 있습니다. 이러한 금속의 경우 정공 주입을 위한 쇼트키 장벽의 높이가 더 낮기 때문입니다. SnSe 나노플레이크에서 금속 접촉으로의 적합성을 결정하기 위해 추가 금속에 대한 접촉 저항을 측정해야 합니다. 이 문제는 현재 전송 길이 방법을 사용하여 해결되고 있습니다.

요약하면, 다층 SnSe 나노플레이크는 SiO2에 백 게이트 FET 구조가 있는 SnSe FET 채널에 대해 성장, 박리 및 특성화되었습니다. /Si 기판. 전기 전송 측정은 Au 금속 접촉이 있는 다층 SnSe 나노플레이크가 박리된 SnSe 나노플레이크 FET에서 상대적으로 낮은 쇼트키 장벽과 낮은 접촉 저항으로 p형 반도체 특성을 나타내는 것으로 나타났습니다. 또한, 우리는 이 연구가 기계적으로 박리된 SnSe 나노플레이크 기반 FET를 보고한 첫 번째 연구임을 강조하며, 우리의 SnSe 나노플레이크 FET가 2D 전기 장치와 미래 세대의 열전기를 포함한 에너지 수확 응용 분야에 매우 유망하다고 확신합니다. .

나노물질

초록 여기에서 ZrOx를 보고합니다. ± 1V V 미만의 45.06mV/decade 하위 임계값 스윙(SS)을 갖는 기반 음의 정전용량(NC) FET GS 이는 미래의 전압 확장 가능한 NCFET 애플리케이션에서 새로운 기회를 얻을 수 있는 범위입니다. Ge/ZrOx의 강유전체와 같은 거동 /TaN 커패시터는 산소 결손 쌍극자에서 비롯된 것으로 제안됩니다. 무정형 HfO2의 NC 효과 및 ZrOx 박막 소자는 게이트 누설의 급격한 감소, 음의 차동 저항(NDR) 현상, I의 향상으로 증명할 수 있습니다. DS 및 60 이하

관심 대상을 실시간으로 모니터링하는 분석 장치인 민감하고 선택적인 전자 바이오센서에 대한 수요는 광범위한 응용 분야에서 증가하고 있습니다. 이는 임상 환경, 약물 발견, 식품 안전 및 품질 관리, 환경 모니터링 내의 건강 관리에 이상적입니다. 전자 바이오센서는 단순성, 짧은 분석 시간, 낮은 제조 비용, 최소한의 샘플 준비 및 훈련받지 않은 직원이 현장에서 사용할 수 있는 가능성으로 인해 매력적입니다. Free University of Bozen-Bolzano와 ETH Zurich 연구원들은 전해질 개폐 탄소 나노튜브 전계 효과