간단히 말해 VHDL은 디지털 회로 설계에 사용되는 컴퓨터 언어입니다. 저는 VHDL을 Java 또는 C++와 같은 보다 일반적인 다른 프로그래밍 언어와 구별하기 위해 컴퓨터 언어라는 용어를 사용합니다. 그러나 VHDL은 프로그래밍 언어입니까? 예, 그렇습니다. 컴퓨터 프로그램을 만들 때 아무 소용이 없는 프로그래밍 언어입니다! VHDL은 이벤트 구동 병렬 프로그래밍 언어입니다. 컴퓨터의 CPU가 실행할 수 있는 프로그램을 만드는 데는 적합하지 않지만 실제 CPU를 만드는 데는 좋습니다. 하드웨어 설명 언어로 디지털 논리

VHDL 및 FPGA 도구는 종종 매우 비싸지만 학생이라면 무료로 최신 소프트웨어에 쉽게 액세스할 수 있습니다. VHDL 작업을 위한 여러 시뮬레이터, 편집기 및 IDE가 있습니다. 이 기사에서는 VHDL 엔지니어가 사용하는 가장 인기 있는 두 가지 프로그램을 설치하는 방법을 보여줍니다. VHDL 시뮬레이터 Siemens EDA(이전 Mentor Graphics)의 ModelSim은 가장 일반적인 VHDL 시뮬레이터이며, 첫 번째 VHDL 작업에서 프로그램의 ModelSim 또는 QuestaSim 플레이버를 사용해야 할 가능성이

새로운 프로그래밍 언어를 배울 때 저는 항상 인쇄하는 방법을 배우는 것으로 시작하는 것을 좋아합니다. Hello World! 출력을 마스터하면 환경이 작동하고 있음을 알 수 있습니다. 또한 언어의 기본 골격, 출력을 생성하는 데 필요한 최소한의 코드도 보여줍니다. 라고 생각할 수도 있지만 VHDL은 하드웨어 설명 언어인데 어떻게 텍스트를 출력할 수 있습니까? FPGA에 연결된 화면이 필요하고 그 사이에 모든 종류의 로직이 필요하며 이는 전혀 간단하지 않습니다. 이 모든 것이 사실이지만 FPGA와 ASIC은 잠시 잊고 VHDL 언어

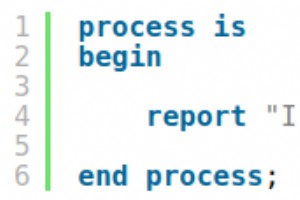

이전 튜토리얼에서 우리는 프로세스를 프로그램 스레드로 생각할 수 있다는 것을 배웠습니다. 또한 wait; 문으로 인해 프로그램이 무기한 일시 중지됩니다. 하지만 프로그램이 영원히가 아닌 다른 시간 값을 기다리게 하는 방법이 있습니까? wait;을 제거하면 프로그램을 컴파일하려고 하면 컴파일러는 무한 루프에 대해 불평할 것입니다. 컴파일러가 참조하는 루프는 프로세스 루프입니다. . VHDL의 프로세스 스레드는 절대 종료되지 않으며 begin 사이에서 계속 반복됩니다. 및 end process; 진술. wait이 있어야 합니다. 프로

이전 튜토리얼에서 wait for를 사용하여 시간을 지연시키는 방법을 배웠습니다. 성명. 프로세스 루프에 대해서도 배웠습니다. 이제 허용하면 프로세스 스레드가 프로세스 내에서 영원히 반복된다는 것을 알고 있습니다. 그러나 프로세스의 시작 부분에서 한 번만 무언가를 하고 싶다면 어떻게 해야 할까요? 그런 다음 끝에 다른 코드를 반복합니까? VHDL에서 가장 단순한 종류의 루프는 loop을 사용하여 생성할 수 있습니다. 성명서. 이 블로그 게시물은 기본 VHDL 자습서 시리즈의 일부입니다. 단순 루프의 구문은 다음과 같습니다.

이전 자습서에서 loop을 사용하여 무한 루프를 만드는 방법을 배웠습니다. 성명. 또한 exit을 사용하여 루프에서 벗어나는 방법도 배웠습니다. 성명. 그러나 루프가 특정 횟수만큼 반복되도록 하려면 어떻게 해야 할까요? For-Loop는 이를 수행하는 가장 쉬운 방법입니다. For-Loop를 사용하면 고정된 범위의 정수 또는 열거된 항목을 반복할 수 있습니다. 현재 반복에 속하는 항목은 암시적으로 선언된 상수를 통해 루프 내에서 사용할 수 있습니다. 이 블로그 게시물은 기본 VHDL 자습서 시리즈의 일부입니다. For 루프

이전 자습서에서 For-Loop를 사용하여 정수 범위를 반복하는 방법을 배웠습니다. 그러나 고정된 정수 범위보다 루프를 더 자세히 제어하려면 어떻게 해야 할까요? 이를 위해 While 루프를 사용할 수 있습니다. While 루프는 테스트하는 표현식이 true로 평가되는 한 계속해서 동봉된 코드를 반복합니다. . 따라서 While-Loop는 얼마나 많은 반복이 필요한지 미리 알 수 없는 상황에 적합합니다. 이 블로그 게시물은 기본 VHDL 자습서 시리즈의 일부입니다. While 루프의 구문은 다음과 같습니다. while <

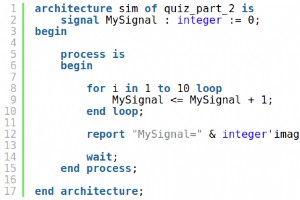

기본 VHDL 자습서 시리즈의 첫 번째 부분을 완료했습니다. 축하합니다! 진정한 VHDL 전문가가 되는 데 몇 시간, 몇 시간 밖에 남지 않았습니다. 하지만 첫 번째 단계를 완료했으며 지금이 가장 중요한 부분입니다! 더 진행하기 전에 다음 퀴즈를 통해 기술을 테스트해야 합니다. 이 과정에 어떤 문제가 있습니까? 포함 대기문 없음 세미콜론 누락 프로세스는 이후 프로세스 입력이 없습니다 옳은! 잘못된! - i의 값은 몇 번이나 인쇄됩니까? 무한 숫자 횟수 0 한 번 옳은! 잘못된! -

이전 튜토리얼에서 우리는 프로세스에서 변수를 선언하는 방법을 배웠습니다. 변수는 프로세스 내에서 알고리즘을 만드는 데 유용하지만 외부 세계에서는 액세스할 수 없습니다. 변수의 범위가 단일 프로세스에만 있는 경우 다른 논리와 어떻게 상호 작용할 수 있습니까? 이에 대한 해결책은 신호입니다. . 신호는 architecture <architecture_name> of <entity_name> is 사이에 선언됩니다. 줄 및 begin VHDL 파일의 명령문. 이것을 아키텍처의 선언적 부분이라고 합니다. 이 블로그

이전 튜토리얼에서 우리는 신호와 변수의 주요 차이점을 배웠습니다. 신호는 하나의 프로세스 내에서만 액세스할 수 있는 변수보다 범위가 더 넓다는 것을 배웠습니다. 그렇다면 여러 프로세스 간의 통신을 위해 신호를 어떻게 사용할 수 있습니까? 우리는 이미 wait; 사용법을 배웠습니다. 무한히 대기하고 wait for 특정 시간 동안 기다리기. VHDL에는 두 가지 유형의 대기 명령문이 더 있습니다. 이 블로그 게시물은 기본 VHDL 자습서 시리즈의 일부입니다. Wait On 문은 지정된 신호 중 하나가 변경될 때까지 프로세스를

이전 자습서에서는 Wait When 문과 함께 조건식을 사용했습니다. 표현식은 두 카운터가 동일한 경우에만 프로세스가 트리거되도록 했습니다. 그러나 프로세스의 프로그램이 다른 입력에 따라 다른 작업을 수행하도록 하려면 어떻게 해야 할까요? If-Then-Elsif-Else 문을 사용하여 프로그램에서 분기를 만들 수 있습니다. 변수의 값이나 표현식의 결과에 따라 프로그램은 다른 경로를 취할 수 있습니다. 이 블로그 게시물은 기본 VHDL 자습서 시리즈의 일부입니다. 기본 구문은 다음과 같습니다. if <condition

항상 민감성 목록을 사용해야 합니다. 생산 모듈에서 프로세스를 트리거합니다. 민감도 목록은 프로세스가 민감한 모든 신호를 나열하는 프로세스에 대한 매개변수입니다. 신호가 변경되면 프로세스가 깨어나고 그 안의 코드가 실행됩니다. 우리는 이미 wait on 사용법을 배웠습니다. 및 wait until 신호가 변경될 때 프로세스를 깨우기 위한 명령문. 하지만 솔직히 말해서 대부분의 프로세스를 쓰는 방식은 아닙니다. 이 블로그 게시물은 기본 VHDL 자습서 시리즈의 일부입니다. VHDL 코드를 작성할 때 작성 스타일은 코드가 시뮬레

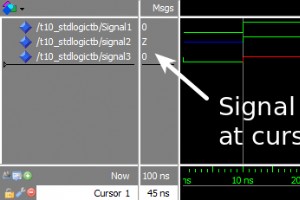

VHDL에서 사용되는 가장 일반적인 유형은 std_logic입니다. . 이 유형을 단일 물리적 와이어에 의해 전달되는 디지털 정보인 단일 비트로 생각하십시오. std_logic integer보다 디자인의 리소스를 더 세밀하게 제어할 수 있습니다. 이전 자습서에서 사용한 유형입니다. 일반적으로 우리는 디지털 인터페이스의 와이어가 1 값을 갖기를 원합니다. 또는 0 . 이 두 값은 비트, 즉 이진수가 가질 수 있는 유일한 값입니다. 그러나 실제로 물리적 디지털 신호는 std_logic과 같은 여러 상태에 있을 수 있습니다. type

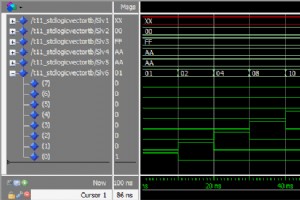

std_logic_vector 유형은 VHDL에서 신호 버스를 만드는 데 사용할 수 있습니다. std_logic VHDL에서 가장 일반적으로 사용되는 유형이며 std_logic_vector 배열 버전입니다. std_logic 동안 단일 와이어로 전달할 수 있는 값을 모델링하는 데는 훌륭하지만 구성 요소에서 오가는 와이어 컬렉션을 구현하는 데는 그다지 실용적이지 않습니다. std_logic_vector 하위 요소의 모음임을 의미하는 복합 유형입니다. std_logic_vector의 신호 또는 변수 유형은 임의의 수의 std_logi

Basic VHDL Tutorial 시리즈의 자습서 6-11을 완료한 후 이 VHDL 퀴즈로 코딩 기술을 테스트하십시오! 블로그 게시물을 읽고 비디오를 보고 연습을 했다면 퀴즈의 대부분의 질문에 답할 수 있는 자격을 갖추었을 것입니다. 퀴즈는 의도적으로 약간 도전적으로 만들어졌습니다. 답을 모른다면 추론 능력을 사용하여 가장 가능성 있는 답을 찾아보십시오. 각 답변 뒤에 나오는 설명을 읽으십시오. 거기에 약간의 미세 학습이 있습니다. 이 코드는 무엇을 출력할까요? MySignal=-2147483648 MySignal

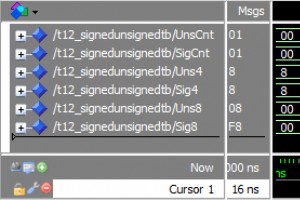

VHDL의 부호 있는 유형과 부호 없는 유형은 std_logic_vector 유형과 마찬가지로 비트 벡터입니다. 차이점은 std_logic_vector가 데이터 버스를 구현하는 데는 훌륭하지만 산술 연산을 수행하는 데는 쓸모가 없다는 것입니다. std_logic_vector 유형에 숫자를 추가하려고 하면 ModelSim에서 컴파일 오류가 발생합니다. 중위 연산자 +에 대해 가능한 항목이 없습니다. 이는 컴파일러가 이 비트 모음을 벡터로 해석하는 방법을 모르기 때문입니다. 이 블로그 게시물은 기본 VHDL 자습서 시리즈의 일부입니

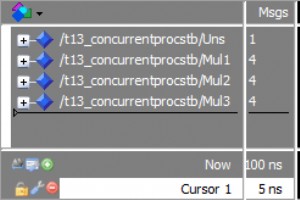

VHDL의 동시 명령문은 아키텍처 내에서 신호 할당이지만 정상적인 프로세스 구성 외부에 있습니다. 동시 명령문은 동시 할당 또는 동시 프로세스라고도 합니다. 동시 명령문을 생성할 때 실제로는 명확하게 정의된 특정 특성을 가진 프로세스가 생성됩니다. 동시 명령문은 항상 민감도 목록을 사용하는 프로세스와 동일하며, 여기서 신호 할당 연산자의 오른쪽에 있는 모든 신호는 민감도 목록에 있습니다. 이러한 속기 표기법 프로세스는 단일 신호를 할당하는 간단한 논리를 생성하려는 경우에 유용합니다. 민감도 목록과 그 모든 것이 포함된 전체 프로

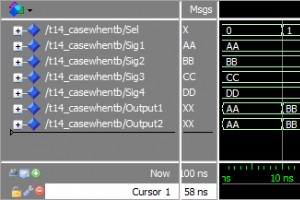

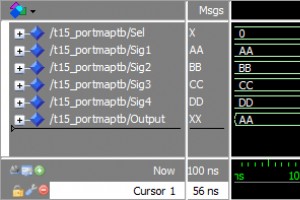

Case-When 문은 신호, 변수 또는 표현식의 값에 따라 프로그램이 여러 경로 중 하나를 선택하도록 합니다. 여러 Elsif가 있는 If-Then-Elsif-Else 문에 대한 보다 우아한 대안입니다. 다른 프로그래밍 언어는 switch와 같은 키워드를 사용하여 유사한 구조를 가지고 있습니다. , 대소문자 , 또는 선택 . 무엇보다도 Case-When 문은 VHDL에서 멀티플렉서를 구현하는 데 일반적으로 사용됩니다. 계속 읽으시거나 동영상을 시청하여 방법을 알아보세요! 이 블로그 게시물은 기본 VHDL 자습서 시리즈의 일부입

모듈은 VHDL 코드의 독립된 단위입니다. 모듈은 엔티티를 통해 외부 세계와 통신합니다. . 항구 지도 모듈의 입력과 출력이 연결될 로컬 신호를 선언하는 모듈 인스턴스화의 일부입니다. 이 시리즈의 이전 자습서에서는 기본 VHDL 파일에 모든 코드를 작성했지만 일반적으로 그렇게 하지 않습니다. 시뮬레이터가 아닌 FPGA 또는 ASIC 설계에 사용할 목적으로 로직을 생성합니다. 시뮬레이터에서 실행하기 위해 생성된 VHDL 모듈에는 일반적으로 입력 또는 출력 신호가 없습니다. 완전히 독립적입니다. 그래서 우리 디자인의 엔터티가 비어

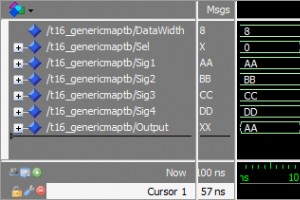

모듈을 만드는 것은 코드를 재사용하는 좋은 방법이지만 디자인 전체에 걸쳐 더 작은 변형을 가진 동일한 모듈이 필요한 경우가 많습니다. 이것이 제네릭과 제네릭 맵의 용도입니다. 이를 통해 모듈의 특정 부분을 컴파일 타임에 구성할 수 있습니다. 상수는 같은 값을 반복해서 입력하지 않으려는 경우에 사용됩니다. 컴파일 타임에 신호 벡터의 비트 너비를 정의하는 데 사용할 수 있으며 일반 상수에도 매핑할 수 있습니다. 상수는 코드의 어느 곳에서나 신호 및 변수 대신 사용할 수 있지만 컴파일 시간 이후에는 값을 변경할 수 없습니다. 이 블로

VHDL