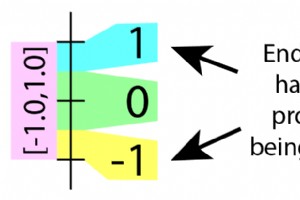

VHDL에는 의사 난수 생성기가 내장되어 있지만 0과 1 사이의 부동 소수점 수만 생성할 수 있습니다. 다행히도 이로부터 필요한 다른 임의의 데이터 형식을 파생할 수 있습니다. 이 기사를 계속 읽고 real를 생성하는 방법을 알아보세요. 또는 integer 임의의 std_logic_vector 뿐만 아니라 모든 범위의 값 시퀀스 및 time 가치. uniform IEEE MATH_REAL 패키지의 절차는 이 기사에서 설명하는 알고리즘의 기초입니다. uniform 난수를 생성하는 소프트웨어에 의존합니다. 따라서 이러한 알고리즘

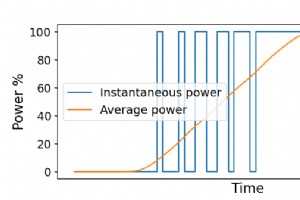

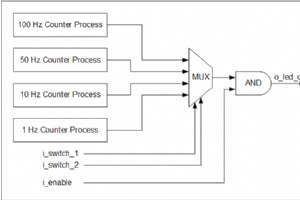

펄스 폭 변조(PWM)는 순수 디지털 FPGA 핀에서 아날로그 전자 장치를 제어하는 효율적인 방법입니다. 아날로그 전압을 조절하는 대신 PWM은 아날로그 장치에 최대 전력으로 공급 전류를 빠르게 켜고 끕니다. 이 방법을 사용하면 소비자 기기에 제공되는 에너지의 이동 평균을 정밀하게 제어할 수 있습니다. PWM의 좋은 후보가 되는 사용 사례의 예로는 오디오 변조(스피커), 광도 제어(램프 또는 LED) 및 유도 모터가 있습니다. 후자는 서보 모터, 컴퓨터 팬, 펌프, 전기 자동차용 브러시리스 DC 모터를 포함하며 그 목록은 계속

나는 지난 몇 년 동안 내가 구입한 많은 가제트가 LED 깜박임에서 주도 호흡으로 바뀌었다는 것을 알게 되었습니다. 대부분의 전자 장치에는 장치 내부에서 일어나는 일을 알려주는 상태 LED가 포함되어 있습니다. 내 전동 칫솔은 충전이 필요할 때 LED가 깜박이고, 내 휴대폰은 다양한 이유로 LED를 사용하여 내 주의를 환기시킵니다. 그러나 LED는 예전처럼 깜박이지 않습니다. 지속적으로 변화하는 강도의 아날로그 펄스 효과와 비슷합니다. 아래 GIF 애니메이션은 이 효과를 사용하여 배터리를 충전 중임을 나타내는 Logitech 마

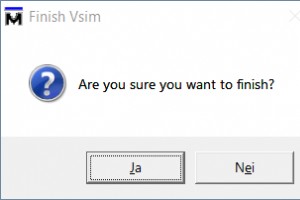

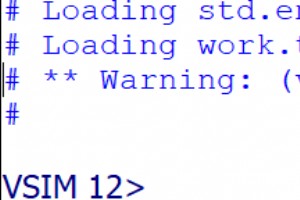

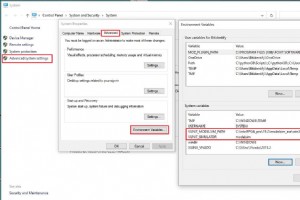

시뮬레이션이 완료되면 VHDL 시뮬레이터를 어떻게 중지합니까? 여러 가지 방법이 있습니다. 이 기사에서는 성공적인 테스트벤치 실행을 종료하는 가장 일반적인 방법을 살펴보겠습니다. 여기에 제시된 VHDL 코드는 보편적이며 가능한 모든 VHDL 시뮬레이터에서 작동해야 합니다. Tcl과 관련된 방법의 경우 ModelSim 및 Vivado 시뮬레이터에 대한 명령을 나열하겠습니다. ModelSim이 설치된 경우 이 기사에서 4개의 다른 테스트벤치가 있는 예제 프로젝트를 다운로드할 수 있습니다. Zip 파일을 받으려면 아래 양식에 이메일

대부분의 VHDL 시뮬레이터는 Tcl(Tool Command Language)을 스크립팅 언어로 사용합니다. 시뮬레이터의 콘솔에 명령을 입력하면 Tcl을 사용하고 있습니다. 또한 시뮬레이터에서 실행되고 VHDL 코드와 상호 작용하는 Tcl로 스크립트를 생성할 수 있습니다. 이 기사에서는 VHDL 모듈이 올바르게 작동하는지 확인하기 위해 VHDL 대신 Tcl을 사용하는 자체 검사 테스트벤치를 만들 것입니다. 참조:Tcl을 배워야 하는 이유Tcl을 사용한 대화형 테스트벤치 아래 양식을 사용하여 이 문서 및 ModelSim 프

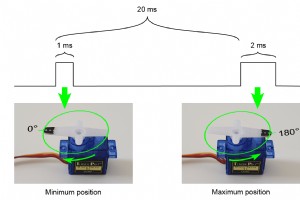

무선 제어(RC) 모델 서보는 일반적으로 애호가 모델 비행기, 자동차 및 보트에 사용되는 작은 액추에이터입니다. 이를 통해 운전자는 무선 링크를 통해 원격으로 차량을 제어할 수 있습니다. RC 모델은 오랫동안 사용되어 왔기 때문에 사실상의 표준 인터페이스는 디지털 방식이 아니라 PWM(펄스 폭 변조)입니다. 다행히 FPGA가 출력 핀에 가할 수 있는 정확한 타이밍으로 PWM을 구현하는 것은 쉽습니다. 이 기사에서는 PWM을 사용하는 모든 RC 서보에서 작동하는 일반 서보 컨트롤러를 만들 것입니다. RC 서보의 PWM 제어 작동

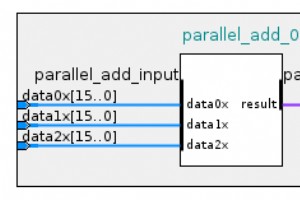

VHDL의 generate 문은 동일한 신호, 프로세스 및 인스턴스가 있는 클로저에 코드 블록을 자동으로 복제할 수 있습니다. 연결된 프로세스 또는 모듈 인스턴스를 생성할 수 있는 아키텍처 영역에 대한 for 루프입니다. 프로세스나 하위 프로그램에만 존재할 수 있는 일반적인 for 루프와 달리 생성 문은 VHDL 파일의 아키텍처 영역에 직접 배치됩니다. 제네릭과 함께 사용하면 설계 전반에 걸쳐 재사용이 가능한 맞춤형 VHDL 모듈을 설계하기 위한 강력한 도구가 됩니다. 문 구문 생성 생성 문의 구문은 다음과 같습니다. [la

VHDL의 텍스트 문자열은 일반적으로 고정 길이 문자 배열로 제한됩니다. VHDL은 하드웨어를 설명하고 일반 길이 문자열에는 동적 메모리가 필요하기 때문에 이는 의미가 있습니다. 문자열 배열을 정의하려면 저장하려는 최대 문자열 수에 대해 컴파일 타임에 공간을 할당해야 합니다. 그리고 더 나쁜 것은 문자열의 최대 길이를 결정하고 모든 항목을 해당 문자 수로 채워야 한다는 것입니다. 아래 코드는 이러한 구문의 사용 예를 보여줍니다. type arr_type is array (0 to 3) of string(1 to 10); si

이 가이드에서는 통합 논리 분석기(ILA) 사용에 대해 설명합니다. 및 가상 입력/출력(VIO) Xilinx Vivado IDE에서 VHDL 설계를 디버그 및 모니터링하기 위한 코어. 많은 경우 설계자는 온칩 검증을 수행해야 합니다. 즉, 검증 목적으로 FPGA 설계에서 내부 신호의 동작에 액세스하는 것입니다. 한 가지 옵션은 이러한 신호를 FPGA 핀으로 가져와 LED에 연결하여 시각적으로 동작을 확인하는 것입니다. 이 옵션은 쉽고 빠르며 간단한 경우에 잘 작동하지만 유연하거나 확장 가능하거나 현실적이지 않습니다. 또 다른

안전이 중요한 FPGA 애플리케이션을 위해 VHDL을 설계할 때 최선을 다해 테스트벤치를 작성하는 것만으로는 충분하지 않습니다. 모듈이 의도한 대로 작동하고 바람직하지 않은 부작용 없이 작동한다는 증거를 제시해야 합니다. 형식 검증 기술을 사용하면 요구 사항을 테스트에 매핑하여 VHDL 모듈이 사양을 준수하는지 증명할 수 있습니다. 의료 애플리케이션을 검증하거나 항공 FPGA 솔루션에 대한 DO-254 인증을 획득하기 위한 도구입니다. VHDLwhiz는 공식적인 검증을 이해하기 위해 Michael Finn Jørgensen의

VUnit은 현재 사용 가능한 가장 인기 있는 오픈 소스 VHDL 검증 프레임워크 중 하나입니다. Python 테스트 스위트 러너와 전용 VHDL 라이브러리를 결합하여 테스트 벤치를 자동화합니다. 이 무료 VUnit 튜토리얼을 제공하기 위해 VHDLwhiz는 컴퓨터에서 다운로드하여 실행할 수 있는 간단한 VUnit 예제 프로젝트를 포함하여 이 기사의 나머지 부분을 담당하는 Ahmadmunthar Zaklouta를 모집합니다. 아흐마드에게 말을 전합시다! 이 튜토리얼은 설계 검증 프로세스에서 VUnit 프레임워크를 사용하는

VUnit 검증 프레임워크를 통해 Quartus IP 코어를 포함하는 VHDL 시뮬레이션을 실행하고 싶었던 적이 있습니까? 이것이 FPGA 엔지니어인 Konstantinos Paraskevopoulos가 염두에 두었지만 적절한 튜토리얼을 찾지 못했습니다. 다행히 그는 자신의 재능을 활용하여 이 게스트 기사를 통해 VHDLwhiz와 공유하는 방법을 알아냈습니다. . 콘스탄티노스에게 한마디 합시다! VUnit으로 시스템을 시뮬레이션할 때 Quartus IP 카탈로그에서 미리 정의된 IP를 설계에 통합하는 것이 종종 바람직합니다.

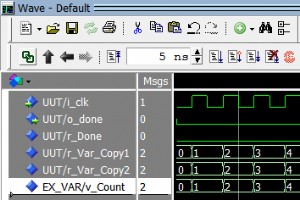

VHDL의 변수는 C의 변수와 유사하게 작동합니다. 해당 값은 변수가 수정되는 코드의 정확한 위치에서 유효합니다. 따라서 신호가 before 변수의 값을 사용하는 경우 할당하면 이전 변수 값을 갖게 됩니다. 신호가 after 변수의 값을 사용하는 경우 할당은 새 변수 값을 갖습니다. 변수 규칙: 변수는 프로세스 내에서만 사용할 수 있습니다. 한 프로세스에서 생성된 변수는 다른 프로세스에서 사용할 수 없습니다. 변수는 키워드 process 뒤에 정의해야 합니다. 그러나 키워드 시작 전에 변수는 :=을 사용하여 할당됩니다. 할

모든 디지털 디자이너는 수학이 FPGA 또는 ASIC 내부에서 어떻게 작동하는지 이해해야 합니다. 이를 위한 첫 번째 단계는 부호 있는 신호 유형과 부호 없는 신호 유형이 작동하는 방식을 이해하는 것입니다. numeric_std에 서명된 유형과 서명되지 않은 유형이 있습니다. ieee 라이브러리의 일부인 패키지. 수학 연산을 수행하는 데 자주 사용되는 또 다른 패키지 파일이 있습니다. std_logic_arith . 그러나 std_logic_arith는 공식 ieee 지원 패키지 파일이 아니므로 디지털 디자인에 사용하지 않는 것이

VHDL의 Record 구문을 사용하여 코드를 단순화할 수 있습니다. 레코드는 C의 구조와 유사합니다. . 레코드는 새로운 VHDL 유형을 정의하는 데 가장 자주 사용됩니다. 이 새로운 유형에는 사용자가 원하는 모든 신호 그룹이 포함됩니다. 대부분 인터페이스를 단순화하는 데 사용됩니다. 이것은 항상 동일한 많은 신호 목록이 있는 인터페이스에서 매우 편리합니다. 예를 들어 오프칩 메모리에 대한 인터페이스는 크고 설계 전반에 걸쳐 동일한 신호를 계속해서 가질 수 있습니다. 레코드를 사용하여 코드 크기를 줄이고 엔터티에서 유지해야 할 신

프로시저는 서브프로그램이라고 하는 구조 그룹의 일부입니다. 프로시저는 코드 전체에서 재사용되는 작업을 수행하는 코드의 작은 섹션입니다. 이것은 코드를 정리하고 재사용을 허용하는 역할을 합니다. 프로시저는 입력을 받고 출력을 생성할 수 있습니다. 일반적으로 함수보다 복잡할 수 있습니다. 절차에 신호를 전달할 필요는 없습니다. 아래 예에는 표준 논리 벡터를 1씩 증가시키고 결과로 신호를 생성하는 것이 목적인 프로시저 p_INCREMENT_SLV가 있습니다. wait 문 사용에 대한 추가 참고 사항: 프로시저를 호출하는 프로세스에

Numeric_Std 및 Std_Logic_Arith 패키지 파일 모두 사용 다음은 VHDL에서 사용되는 가장 일반적인 변환입니다. 페이지는 두 섹션으로 나뉩니다. 페이지의 전반부는 Numeric_Std 패키지 파일을 사용한 변환을 보여줍니다. 페이지의 후반부는 Std_Logic_Arith 패키지 파일을 사용한 변환을 보여줍니다. Std_Logic_Arith를 사용해서는 안 되므로 Numeric_Std 패키지를 사용하는 것이 좋습니다. 많은 사람들이 여전히 사용을 주장하기 때문에 두 가지 예를 모두 아래에서 보여줍니다. 아래의

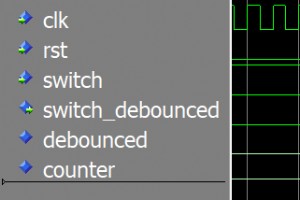

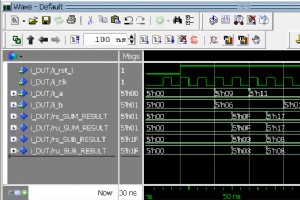

1부:VHDL 또는 Verilog 설계 이 튜토리얼은 지정된 주파수에서 LED를 깜박이는 VHDL 및 Verilog 코드의 구성을 보여줍니다. VHDL과 Verilog가 모두 표시되며 먼저 배우고 싶은 것을 선택할 수 있습니다. 설계 코드가 작성될 때마다 FPGA 설계자는 의도한 대로 작동하는지 확인해야 합니다. 최선의 노력에도 불구하고 초기 설계에는 항상 실수가 있습니다. 이러한 실수를 찾는 가장 좋은 방법은 시뮬레이션 환경입니다. 이 튜토리얼은 2단계로 나뉩니다: HDL 설계 HDL 시뮬레이션 이 두 단계는 성공적인

VHDL 프로세스 또는 Verilog Always Blocks 사용 이 튜토리얼은 Process에 포함된 VHDL 또는 Verilog 블록을 작성하는 방법을 보여줍니다. 또는 항상 차단 각기. 프로세스(VHDL에서) 및 항상 차단(Verilog에서)은 기본이며 잘 이해해야 합니다. 그것들은 정확히 같은 방식으로 작동하므로 둘 다 여기에서 소개됩니다. 지금 한 언어만 배우고 있다면 해당 특정 언어에 초점을 맞춘 예제에 주의를 기울이십시오. 프로세스 또는 항상 차단은 두 가지 주요 시나리오에서 사용됩니다. 조합 블록을 정의하려면 논

VHDL은 끔찍한 약어입니다. V를 나타냅니다. HSIC H 하드웨어 D 설명 L 앙앙. 약어 안의 약어, 굉장합니다! VHSIC는 V를 나타냅니다. 에리 H 응 S 오줌 나 통합된 C 일렉트릭. 따라서 확장된 VHDL은 V입니다. ery 고속 집적 회로 H 하드웨어 D 설명 L 앙앙. PHEW 한 입입니다. VHDL은 교육 및 비즈니스에서 FPGA 및 ASIC을 설계하는 데 사용하는 두 가지 언어 중 하나입니다. 이러한 매혹적인 회로에 익숙하지 않은 경우 먼저 FPGA 및 ASIC에 대한 소개를 통해 이점을 얻을 수 있습니다. V

VHDL