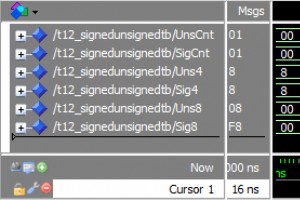

VHDL의 부호 있는 유형과 부호 없는 유형은 std_logic_vector 유형과 마찬가지로 비트 벡터입니다. 차이점은 std_logic_vector가 데이터 버스를 구현하는 데는 훌륭하지만 산술 연산을 수행하는 데는 쓸모가 없다는 것입니다. std_logic_vector 유형에 숫자를 추가하려고 하면 ModelSim에서 컴파일 오류가 발생합니다. 중위 연산자 +에 대해 가능한 항목이 없습니다. 이는 컴파일러가 이 비트 모음을 벡터로 해석하는 방법을 모르기 때문입니다. 이 블로그 게시물은 기본 VHDL 자습서 시리즈의 일부입니

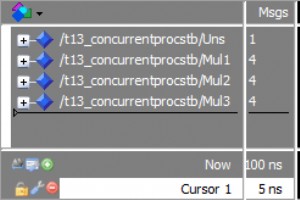

VHDL의 동시 명령문은 아키텍처 내에서 신호 할당이지만 정상적인 프로세스 구성 외부에 있습니다. 동시 명령문은 동시 할당 또는 동시 프로세스라고도 합니다. 동시 명령문을 생성할 때 실제로는 명확하게 정의된 특정 특성을 가진 프로세스가 생성됩니다. 동시 명령문은 항상 민감도 목록을 사용하는 프로세스와 동일하며, 여기서 신호 할당 연산자의 오른쪽에 있는 모든 신호는 민감도 목록에 있습니다. 이러한 속기 표기법 프로세스는 단일 신호를 할당하는 간단한 논리를 생성하려는 경우에 유용합니다. 민감도 목록과 그 모든 것이 포함된 전체 프로

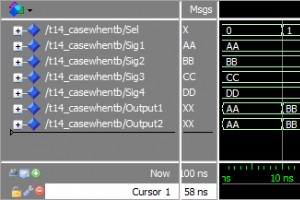

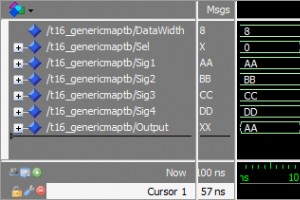

Case-When 문은 신호, 변수 또는 표현식의 값에 따라 프로그램이 여러 경로 중 하나를 선택하도록 합니다. 여러 Elsif가 있는 If-Then-Elsif-Else 문에 대한 보다 우아한 대안입니다. 다른 프로그래밍 언어는 switch와 같은 키워드를 사용하여 유사한 구조를 가지고 있습니다. , 대소문자 , 또는 선택 . 무엇보다도 Case-When 문은 VHDL에서 멀티플렉서를 구현하는 데 일반적으로 사용됩니다. 계속 읽으시거나 동영상을 시청하여 방법을 알아보세요! 이 블로그 게시물은 기본 VHDL 자습서 시리즈의 일부입

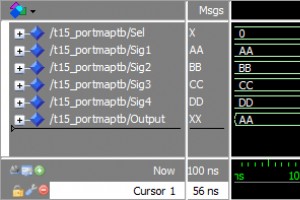

모듈은 VHDL 코드의 독립된 단위입니다. 모듈은 엔티티를 통해 외부 세계와 통신합니다. . 항구 지도 모듈의 입력과 출력이 연결될 로컬 신호를 선언하는 모듈 인스턴스화의 일부입니다. 이 시리즈의 이전 자습서에서는 기본 VHDL 파일에 모든 코드를 작성했지만 일반적으로 그렇게 하지 않습니다. 시뮬레이터가 아닌 FPGA 또는 ASIC 설계에 사용할 목적으로 로직을 생성합니다. 시뮬레이터에서 실행하기 위해 생성된 VHDL 모듈에는 일반적으로 입력 또는 출력 신호가 없습니다. 완전히 독립적입니다. 그래서 우리 디자인의 엔터티가 비어

모듈을 만드는 것은 코드를 재사용하는 좋은 방법이지만 디자인 전체에 걸쳐 더 작은 변형을 가진 동일한 모듈이 필요한 경우가 많습니다. 이것이 제네릭과 제네릭 맵의 용도입니다. 이를 통해 모듈의 특정 부분을 컴파일 타임에 구성할 수 있습니다. 상수는 같은 값을 반복해서 입력하지 않으려는 경우에 사용됩니다. 컴파일 타임에 신호 벡터의 비트 너비를 정의하는 데 사용할 수 있으며 일반 상수에도 매핑할 수 있습니다. 상수는 코드의 어느 곳에서나 신호 및 변수 대신 사용할 수 있지만 컴파일 시간 이후에는 값을 변경할 수 없습니다. 이 블로

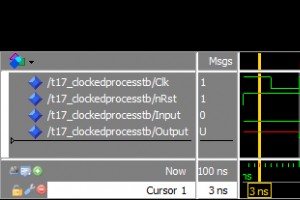

대부분의 VHDL 디자인은 클럭 로직을 사용합니다. , 동기 논리라고도 함 또는 순차 논리 . 클럭된 프로세스는 마스터 클럭 신호에 의해서만 트리거되고 다른 입력 신호가 변경될 때는 트리거되지 않습니다. 클럭 로직의 기본 구성 요소는 플립플롭이라는 구성 요소입니다. . 다양한 변형이 있으며 이 튜토리얼에서는 네거티브 리셋이 있는 포지티브 에지 트리거 플립플롭에 중점을 둘 것입니다. 플립플롭은 샘플 앤 홀드 회로로, 클록 신호의 상승 에지가 도착할 때 입력에서 출력으로 값을 복사합니다. 그런 다음 출력은 클록의 다음 상승 에

기본 VHDL 자습서 시리즈의 자습서 12-17을 완료한 후 이 VHDL 퀴즈로 진행 상황을 테스트하세요! 서명된 유형에 대한 설명으로 옳은 것은? 부호 없는 유형보다 높은 값을 나타냄 맨 왼쪽 비트는 1입니다. 값은 음수여야 합니다. 오버플로는 런타임 오류 옳은! 잘못된! - 이 동시 프로세스에 해당하는 것은 무엇입니까? 옳은! 잘못된! - 이 코드를 실행한 후 출력은 어떤 값을 갖게 될까요? 0000 0001 UUUU XXXX

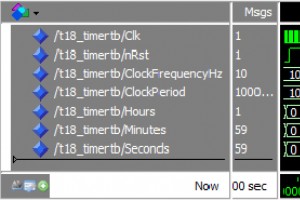

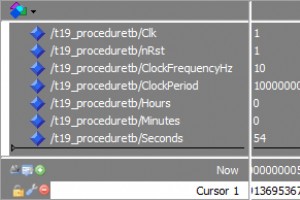

이전 자습서에서는 wait for를 사용했습니다. 시뮬레이션에서 시간을 지연시키는 명령문. 그러나 생산 모듈은 어떻습니까? wait for 문을 사용할 수 없습니다. 회로의 전자에게 주어진 시간 동안 일시 중지하도록 말할 수 없기 때문에 시뮬레이션에서만 작동합니다. 그렇다면 디자인 모듈에서 어떻게 시간을 추적할 수 있습니까? 답은 단순히 클럭 사이클을 계산하는 것입니다. 모든 디지털 설계는 알려진 고정 주파수에서 진동하는 클록 신호에 액세스할 수 있습니다. 따라서 클럭 주파수가 100MHz라는 것을 알면 1억 클럭 사이클을 세어

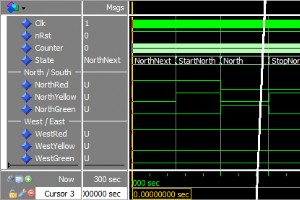

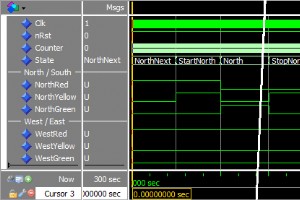

절차는 코드 반복을 방지하는 데 도움이 되는 VHDL의 하위 프로그램 유형입니다. 때로는 설계 전반에 걸쳐 여러 위치에서 동일한 작업을 수행해야 할 필요가 있습니다. 모듈을 생성하는 것은 사소한 작업에는 과도할 수 있지만 절차가 필요한 경우가 많습니다. 프로시저는 모든 선언적 영역 내에서 선언할 수 있습니다. 절차의 범위는 선언된 모든 곳, 아키텍처, 패키지 또는 프로세스로 제한됩니다. 프로시저를 호출할 때마다 호출된 위치에 프로시저 코드가 삽입된 것처럼 작동합니다. 프로시저는 함수처럼 값을 반환하지 않지만 out을 선언하여 값

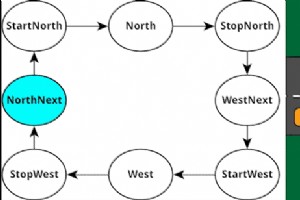

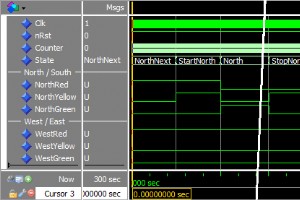

유한 상태 기계(FSM)는 출력이 입력의 현재 상태뿐만 아니라 과거 입력 및 출력 값에 따라 달라지는 메커니즘입니다. VHDL에서 일종의 시간 종속 알고리즘을 생성해야 할 때마다 또는 FPGA에서 컴퓨터 프로그램을 구현하는 문제에 직면한 경우 일반적으로 FSM을 사용하여 해결할 수 있습니다. VHDL의 상태 머신은 상태 신호 값에 의해 출력이 제어되는 클럭 프로세스입니다. 상태 신호는 이전 반복에서 발생한 일의 내부 메모리 역할을 합니다. 이 블로그 게시물은 기본 VHDL 자습서 시리즈의 일부입니다. 이 교차로의 신호등 상

함수는 자주 사용되는 알고리즘을 구현하는 데 사용할 수 있는 VHDL의 하위 프로그램입니다. 함수는 0개 이상의 입력 값을 사용하며 항상 값을 반환합니다. 반환 값 외에도 함수를 프로시저와 구분하는 것은 Wait 문을 포함할 수 없다는 것입니다. 이는 함수가 항상 시뮬레이션 시간을 0으로 소비한다는 것을 의미합니다. 다른 프로그래밍 언어의 함수나 메서드에 익숙하다면 VHDL 함수를 이해하기 쉬워야 합니다. VHDL에서는 반환 값을 생략하거나 void를 반환할 수 없으며, 함수는 항상 무언가를 반환해야 하고 반환 값은 무언가에 할당

불순한 함수는 범위 내의 모든 신호를 읽거나 쓸 수 있으며 매개변수 목록에 없는 신호도 읽을 수 있습니다. 함수에 부작용이 있다고 말합니다. . 부작용이 의미하는 바는 함수가 동일한 매개변수로 호출될 때마다 동일한 값을 반환한다는 보장이 없다는 것입니다. 함수가 매개변수 목록에 없는 신호를 읽을 수 있는 경우 반환 값도 이러한 그림자 매개변수에 따라 달라질 수 있습니다. 또한 함수는 반환 값에서 할당되지 않은 외부 신호를 변경할 수 있습니다. 이 블로그 게시물은 기본 VHDL 자습서 시리즈의 일부입니다. 순수 함수를 선언할

프로시저에서 외부 신호를 구동할 수 있습니다. 신호가 프로시저 범위 내에 있는 한 매개변수 목록에 나열되지 않더라도 읽기 또는 쓰기를 위해 액세스할 수 있습니다. 아키텍처의 선언적 영역에 선언된 프로시저는 외부 신호를 구동할 수 없습니다. 이는 단순히 컴파일 시간에 해당 범위에 신호가 없기 때문입니다. 반면에 프로세스 내에서 선언된 프로시저는 프로세스가 볼 수 있는 모든 신호에 액세스할 수 있습니다. 이 블로그 게시물은 기본 VHDL 자습서 시리즈의 일부입니다. 이러한 절차는 동일한 작업이 여러 번 발생하는 프로세스에서 알고

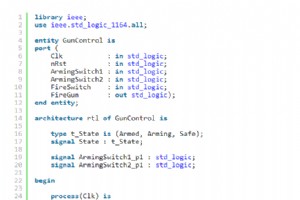

기본 VHDL 자습서 시리즈의 4부를 완료한 후 이 VHDL 퀴즈로 진행 상황을 테스트하세요! VHDL에서 실시간을 어떻게 측정합니까? 사용하여 1ns 대기 문 계산하여 시계 주기 악용하여 전파 지연 옳은! 잘못된! - 어떤 문장이 참인지 프로시저는 대기 문을 포함할 수 없습니다. 프로시저 매개변수 항상 입력입니다 사용 시 프로시저에서 return 키워드는 값이 없어야 합니다. 옳은! 잘못된! - 이 화재 제어 시스템의 근본적인 결함을 설명하는 설명은 무엇입니까? 재설정 누락 주 신

연결 목록은 동적 데이터 구조입니다. 연결 리스트는 요소의 총 개수를 미리 알 수 없을 때 사용할 수 있습니다. 메모리에 포함된 항목 수에 따라 메모리가 늘어나고 줄어듭니다. 연결 목록은 객체 지향 프로그래밍 언어의 클래스를 사용하여 가장 편리하게 구현됩니다. VHDL에는 사용자로부터 구현의 복잡성을 추상화하는 데 사용할 수 있는 몇 가지 개체 지향 기능이 있습니다. 이 기사에서는 액세스 유형, 레코드 및 보호 유형을 사용하여 VHDL에서 연결 목록을 구현합니다. 모든 연결 목록 코드를 작성할 새 VHDL 패키지를 만들 것입니다

자가 점검 테스트벤치는 출력을 수동으로 검사하기 위해 작업자에 의존하지 않고 테스트 대상 장치(DUT)의 정확성을 검증하는 VHDL 프로그램입니다. 자체 검사 테스트벤치는 완전히 자체적으로 실행되며 마지막에 OK 또는 Failed 메시지를 출력합니다. 모든 VHDL 모듈에는 자체 검사 테스트벤치가 연결되어 있어야 합니다. 모든 모듈이 언제든지 의도한 동작을 하는지 확인할 수 있는 것이 중요합니다. 예를 들어, DUT, 하위 모듈 또는 인터페이스 모듈을 변경할 때. 우리 모두는 물건이 깨질 수 있다는 것을 알고 있으며 이러한 문제를

대화형 테스트벤치는 테스트벤치가 실행되는 동안 작업자가 테스트 대상 장치(DUT)에 대한 입력을 제공하는 시뮬레이터 설정입니다. 대부분의 경우 이는 시뮬레이터 콘솔에 명령을 입력하여 DUT에 자극을 제공하는 것을 의미합니다. 항상 자체 검사 테스트벤치를 만들어야 하지만 대화형 테스트벤치는 훌륭한 보완책이 될 수 있습니다. 자체 검사 테스트벤치의 코드를 변경하는 것보다 대화형 테스트벤치로 임시 테스트를 수행하는 것이 더 쉽습니다. 종종 실험실에서 테스트벤치에서 시험해보고 싶은 문제를 발견하게 될 것입니다. 대화형 테스트벤치를 사용

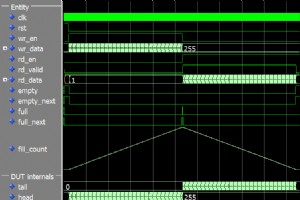

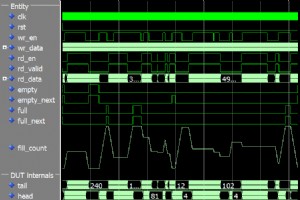

순환 버퍼는 순차 프로그래밍 언어로 대기열을 생성하는 데 널리 사용되는 구성이지만 하드웨어에서도 구현할 수 있습니다. 이 기사에서는 블록 RAM에서 FIFO를 구현하기 위해 VHDL에서 링 버퍼를 생성할 것입니다. FIFO를 구현할 때 많은 설계 결정을 내려야 합니다. 어떤 종류의 인터페이스가 필요합니까? 자원에 제약이 있습니까? 덮어쓰기 및 덮어쓰기에 탄력적이어야 합니까? 대기 시간이 허용됩니까? FIFO를 생성하라는 요청을 받았을 때 떠오르는 질문 중 일부입니다. 온라인에는 많은 무료 FIFO 구현과 Xilinx LogiCO

제한된 무작위 검증은 테스트 대상 장치(DUT)에 대한 의사 무작위 트랜잭션 생성에 의존하는 테스트벤치 전략입니다. 목표는 DUT와의 무작위 상호 작용을 통해 미리 정의된 여러 이벤트의 기능 범위에 도달하는 것입니다. OSVVM(Open Source VHDL Verification Methodology)은 제한된 무작위 테스트벤치를 생성하기 위한 여러 편리한 패키지를 포함하는 무료 VHDL 라이브러리입니다. 우리는 특히 이 기사에서 사용할 RandomPkg 및 CoveragePck에 관심이 있습니다. 이 라이브러리의 기능에 대해

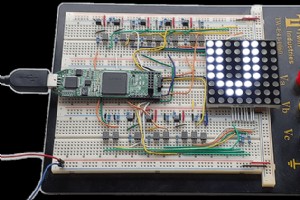

지난 6개월 동안 작업한 VHDL 및 FPGA 과정이 완료되기 시작했음을 알리게 되어 기쁩니다. 이 과정은 현재 베타 버전이며 올 가을에 처음으로 시작할 계획입니다. FPGA 과정은 누구를 위한 것입니까? FPGA 과정은 다른 프로그래밍 언어에 대한 지식이 있지만 VHDL 및 FPGA가 처음인 개발자를 대상으로 합니다. 이 과정은 초급 또는 중급 수준에서 고급 VHDL 코딩 구성을 이해하고 사용할 수 있도록 안내합니다. 이 과정은 FPGA 개발 업무를 맡은 전문 소프트웨어 엔지니어에게 적합합니다. 또한 하드웨어 설계에 관심이 있

VHDL