Pt/Nd:SrTiO3 접합에서 다단계 저항 스위칭 메모리 및 메모리 상태 종속 광전압에 관한 연구

초록

Pt/Nd:SrTiO3 (STO)/In 장치는 Nd 도핑된 단결정 STO에 Schottky-contact Pt 및 Ohmic-contact In 전극을 증착하여 제작되었습니다. Pt/Nd:STO/In 장치는 적용된 펄스 폭 또는 크기로 제어할 수 있는 다중 레벨 저항 스위칭(RS) 메모리 및 메모리 상태 종속 광전압(PV) 효과를 보여줍니다. RS와 PV는 모두 Pt/Nd:STO 인터페이스에서 높이와 너비 모두에서 인터페이스 장벽의 바이어스 유도 변조와 관련이 있습니다. 결과는 RS/PV 효과와 인가된 전기장에 의해 트리거된 Nd:STO 인터페이스 변조 사이에 강력한 연결을 설정하고 여러 비휘발성 메모리 상태를 비파괴적으로 감지하기 위해 개방 회로 전압을 사용하여 새로운 경로를 제공합니다.

<섹션 데이터-제목="배경">

배경

SrTiO3 (STO)는 큰 밴드갭(3.2eV) 절연체입니다. 넓은 온도 범위에서 단순한 입방 구조로 인해 모델 페로브스카이트 재료로 간주됩니다[1]. STO는 도너 또는 억셉터 유형의 전이 금속을 도핑하여 직접 조작할 수 있는 풍부한 광전 성능을 가지고 있습니다. STO 시스템의 적용 범위는 매우 넓습니다[2, 3]. 최근 STO 시스템은 RRAM(Resistive Random Access Memory)을 구축하기 위한 좋은 후보로 볼 수 있는 RS(Resistive Switching) 현상으로 많은 과학적 관심을 받고 있다[4, 5].

STO 기반 RS 소자는 일반적으로 금속/STO/금속 구조이다. STO 시스템의 RS 특성, 즉 억셉터에서 도너 도핑된 STO까지 광범위하게 조사되었습니다. 스위칭 동작을 설명하기 위해 다양한 물리적 메커니즘이 제안되었습니다. 억셉터 도핑(예:Fe 및 Cr) STO의 경우, 연구는 RS가 전위를 따라 산소 결손의 빠른 이동 또는 전기장에 의한 산소 결손 이동에 기인한 결정 벌크의 특성 변화를 강조합니다. 또는 높은 전기적 스트레스에서 산소 결손 어레이의 형성 [6,7,8,9,10,11]. 한편, 도너 도핑(예, Nb) STO 기반 RS 소자의 경우 금속과 n형 Nb:STO 사이의 쇼트키형 접촉이 필요하며 많은 연구에서 강조되고 있다. 그러나 일부 보고서에서는 RS를 금속/Nb:STO 접합에서 전자 공핍층의 변화와 연결했는데, 이는 얇은 계면층 내의 산소 화학량론[12,13,14] 또는 공칭 양이온 화학량론의 편차로 인해 발생합니다. 표면 근처 영역[15, 16] 및 일부 보고서에 따르면 RS 프로세스 동안 계면 장벽이 변경되지 않고 유지되지만 전도성 필라멘트가 저항 변화에 중요한 역할을 한다고 제안합니다[17,18,19].

상기 보고된 사항을 고려할 때 도너형 STO의 스위칭 메커니즘에 대한 합의가 이루어지지 않은 것은 자명하다. 인터페이스와 벌크 저항 변화에 대한 두 가지 관점이 지금까지 공존하고 있습니다. RS에 대한 구체적인 이유에 관해서는 여전히 많은 보고된 물리적 메커니즘이 있습니다. 불분명한 물리적 메커니즘은 STO 소재를 기반으로 한 RRAM의 진행을 가로막고 있습니다. RS 메커니즘을 명확히 하고 도너형 STO 시스템을 기반으로 하는 RRAM 소자를 개발하기 위해서는 다양한 금속 도핑 STO 재료를 연구하는 것이 유리하다.

STO의 전자 수송 특성은 전이 금속 도핑을 통해 조절될 수 있습니다[20]. 박막과 비교할 때 단결정은 전체 영역에 걸쳐 균일한 특성을 가지며 결함 물리 및 화학이 잘 정립되어 있습니다. 지금까지 RS 장치에 대해 보고된 Nb 원소가 포함된 도너 도핑된 STO 단결정만 찾았습니다. Nd 도핑된 STO 단결정(Nd:STO)의 경우 Sr

2+

의 이온 반경 , Ti

4+

및 Nd

3+

(Nd

2+

)은 각각 0.118, 0.0605 및 0.0983(0.129) nm이며, 이는 Nd

3+

Sr

2+

을(를) 쉽게 대체할 수 있습니다. Ti

4+

보다는 Nd

3+

사이의 유사한 반경으로 인해 및 Sr

2+

[21]. 이 치환 부위는 n형 Nb:STO와 다릅니다. 따라서 Nd:STO 단결정은 도너가 도핑된 물질이며 나중에 홀 효과로 증명될 n형 전도도입니다. Nd:STO 단결정은 RS용의 새로운 n형 STO로 아직까지 보고된 작품을 찾지 못했다.

일반적으로 PV(photovoltaic) 효과는 내부 전기장과 관련이 있는 것으로 알려져 있습니다[22,23,24,25,26]. 따라서 RS가 주로 금속 및 n-형 STO 인터페이스 근처의 공핍층에 의해 결정되는 경우 PV 효과는 메모리 상태에 따라 달라질 것으로 예상됩니다. 반대로 RS가 전도성 필라멘트에 의해 유도되는 경우 PV는 메모리 상태와 관련이 없습니다. 이 작업에서 우리는 n형 Nd:STO 단결정에 쇼트키 접촉 Pt 및 옴 접촉 In 전극을 제작했습니다. Pt/Nd:STO/In 소자의 스위칭 메커니즘을 명확히 하기 위해 RS 메모리와 PV 효과를 함께 연구했습니다. 흥미롭게도 결과는 Pt/Nd:STO/In 장치가 스위칭 바이어스에 의해 변조될 수 있는 다중 레벨 메모리 및 메모리 상태 제어 PV 효과를 가지고 있음을 분명히 보여줍니다. 결과는 RS 및 PV에 대한 공유 메커니즘이 Pt/Nd:STO 인터페이스 장벽의 변조와 관련이 있음을 시사하며, 이는 캐리어의 주입 및 트래핑 또는 디트랩핑에 의해 유도됩니다.

방법

5mm 크기의 단결정 Nd:STO(100)× 5mm × 0.05wt% Nd 도핑이 있는 0.5mm가 기판으로 선택되었습니다. In 전극(주황색 전극)을 Nd:STO의 거친 표면에 직접 눌러 옴 접점을 형성했습니다. 직경 0.1mm의 Pt 전극을 섀도우 마스크(파란색 전극)를 통해 Nd:STO 단결정 위에 스퍼터링했습니다. 두 개의 가까운 Pt 전극 사이의 거리는 0.5mm였습니다. 그림 2a의 삽입은 Pt/Nd:STO/In 및 In/Nd:STO/In 장치의 구성을 보여줍니다. 전류-전압(I-V) 및 RS 특성은 Keithley 2400 SourceMeter에서 측정되었습니다. 양의 전기장은 In에서 Pt 전극으로 흐르는 전류로 정의됩니다.

Nd 도핑에 의해 유도된 캐리어 농도를 조사하기 위해 Ecopia HMS-3000 홀 측정 시스템을 사용하여 홀 효과를 수행했습니다. STO의 결정 구조는 Cu Kα 방사선을 사용하여 x-선 회절(XRD, Bruker, D8-Advance)에 의해 조사되었습니다. 라만 산란 측정은 여기 소스로 파장 632.8nm의 가시 레이저 광선을 사용하여 공초점 마이크로 라만 분광계(Renishaw R-1000)에서 수행되었습니다.

결과 및 토론

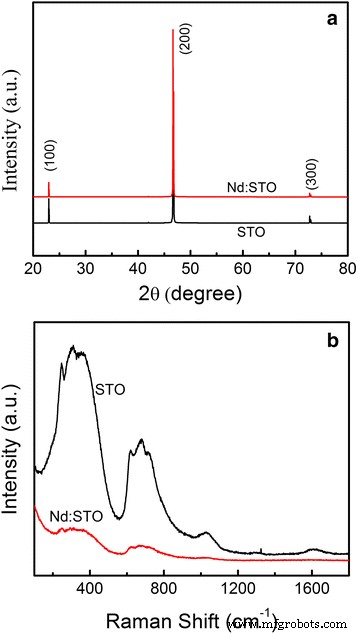

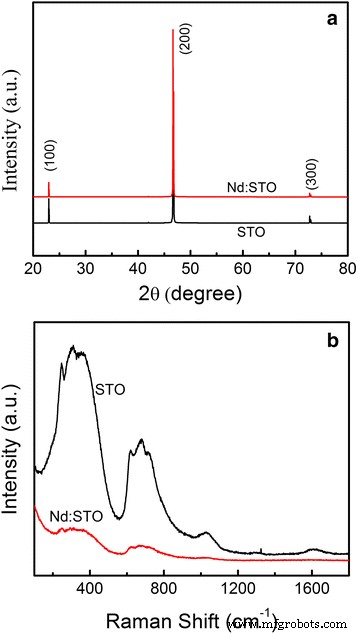

그림 1a는 도핑되지 않은 STO 및 Nd:STO 단결정의 XRD 패턴을 보여줍니다. 모든 피크는 페로브스카이트 위상에 해당하며 격자 상수 a ≈ 3.905 Å를 사용하여 입방 공간 그룹 Pm3m으로 인덱싱될 수 있습니다. 피크는 Nd 주입 후 관찰 가능한 변화를 나타내지 않으며, 이는 Nd 도핑이 벌크 구조에 거의 영향을 미치지 않는다는 것을 나타냅니다. 도핑되지 않은 STO 및 Nd:STO 단결정의 라만 스펙트럼은 그림 1b에 나와 있습니다. 도핑되지 않은 STO의 라만 스펙트럼은 200–400cm

−1

를 중심으로 하는 2차 산란에서 비롯된 두 개의 뚜렷한 광대역을 보여줍니다. 및 600–800cm

−1

이상적인 입방 페로브스카이트 구조에 속합니다. 이 두 밴드의 위치는 출판된 문헌[27, 28]과 일치합니다. Nd:STO에서 감소된 2차 광대역과 함께 확장된 선도 관찰되며, 이는 Nd 도핑에 의해 유도된 국부적 무질서의 결과로 약한 중심 대칭을 나타냅니다. XRD 패턴과 비교하여 라만 결과는 Nd 도핑에 의해 유도되어야 하는 Nd:STO 단결정 표면에 일부 구조적 결함이 있음을 나타냅니다.

<그림><그림><소스 유형="이미지/webp" srcset="//media.springerature.com/lw685/springer-static/image/art%3A10.1186%2Fs11671-018-2433-5/MediaObjects/ 11671_2018_2433_Fig1_HTML.gif?as=webp">

아 XRD 패턴 및 b 도핑되지 않은 STO 및 Nd 도핑된 STO 단결정의 라만 스펙트럼

일반적으로 도핑되지 않은 STO 단결정은 절연 물질로 알려져 있다. STO 단결정의 전기적 특성에 대한 Nd 도핑 영향을 조사하기 위해 홀 효과를 측정했습니다. 홀 결과는 Nd:STO 단결정이 n형 전도도에 있고 캐리어 농도가 약 2 ×임을 보여줍니다. 10

19

cm

−1

. 이 n형 전도도는 Nd

3+

Sr

2+

으로 사이트.

그림 2a의 삽입은 In/Nd:STO/In 및 Pt/Nd:STO/In 장치의 개략도를 보여줍니다. 나 –V In/Nd:STO/In 및 Pt/Nd:STO/In 장치의 특성은 각각 그림 2a, b에 표시되어 있습니다. 스위핑 전압은 50mA 준수 전류에서 0V → 5V → 0V → − 5V → 0V로 적용되었습니다. In/Nd:STO/In 장치에는 선형 I가 있습니다. –V 곡선(그림 2a 참조)이고 눌려진 In 전극과 Nd:STO 단결정 사이에 우수한 옴 접촉을 나타내지만 RS 효과는 나타나지 않는 반면 Pt/Nd:STO/In 장치는 가역적인 RS 속성을 보여줍니다. 그림 2b. 인가 전압이 증가하면 저항 천이가 발생하며 천이 방향은인가 전압의 극성에 따라 다릅니다. 인가 전압이 감소하면 고저항 및 저저항 상태(HRS 및 LRS)가 유지되어 저항 상태가 형성 후 안정되고 비휘발성임을 나타냅니다. 큰 나 –V 히스테리시스는 Pt/Nd:STO/In 장치에 메모리 속성이 있음을 보여줍니다. 프로토타입 다이오드 동작은 쇼트키 장벽이 Pt 및 n형 Nd:STO 인터페이스에 형성되고 Pt/Nd:STO/In 장치의 저항을 지배한다는 것을 나타냅니다. 따라서 Pt/Nd:STO/In 소자의 RS 효과는 Pt와 Nd:STO 단결정 사이의 쇼트키 계면에서 비롯된다고 쉽게 결론지을 수 있습니다. RS가 쇼트키 인터페이스에 의존하는 이 결과는 n형 Nb:STO 단결정에 대한 보고된 작업과 일치합니다[29].

<그림><그림><소스 유형="이미지/webp" srcset="//media.springerature.com/lw685/springer-static/image/art%3A10.1186%2Fs11671-018-2433-5/MediaObjects/ 11671_2018_2433_Fig2_HTML.gif?as=webp">

나 –V a의 특성 In/Nd:STO/In 및 b Pt/Nd:0V → 5V → 0V → − 5V → 0V 전압 범위의 STO/In 장치, 50mA 규정 준수 전류. 삽입은 장치 개략도를 보여줍니다.

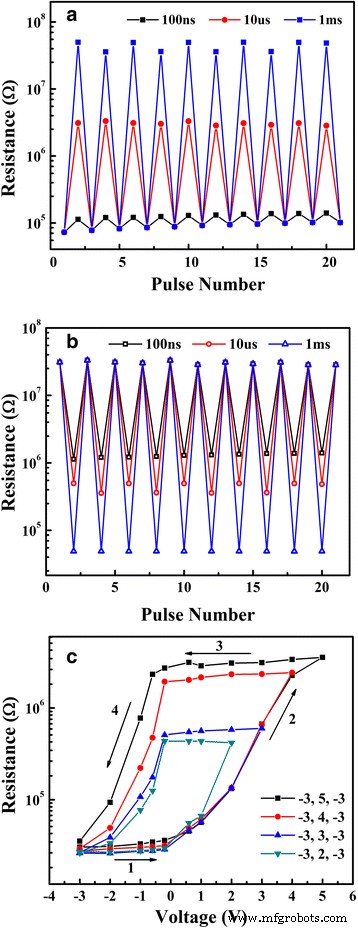

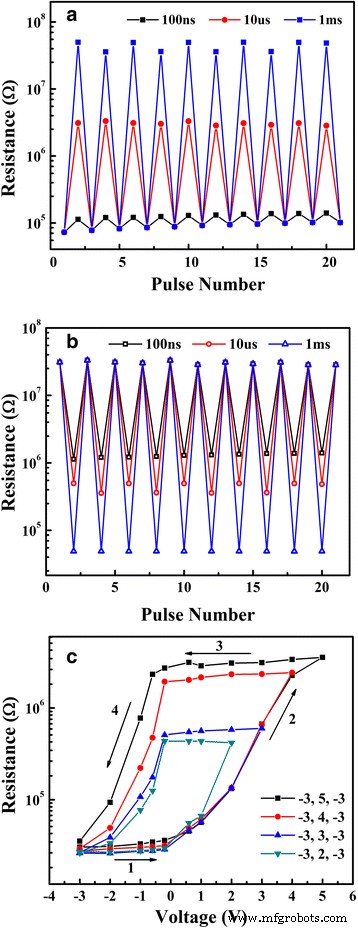

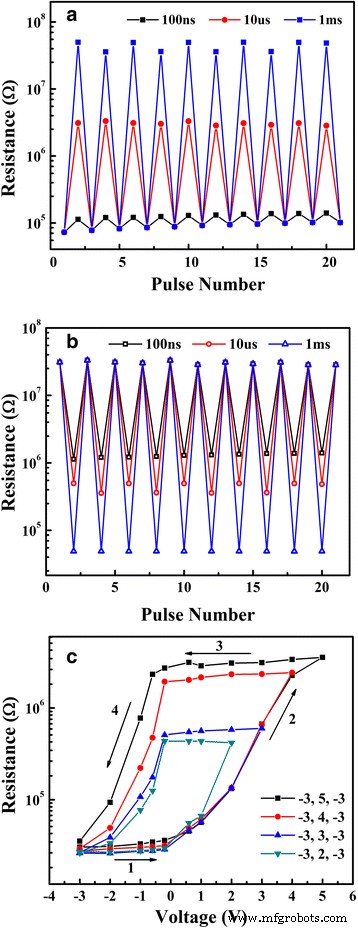

다중 메모리에서 Pt/Nd:STO/In 장치의 적용 가능성을 평가하기 위해 펄스 폭과 진폭이 저항 상태에 미치는 영향을 조사하고 그림 3a–c에 표시했습니다. 장치는 먼저 100ms 너비의 − 5V 펄스로 LRS로 설정한 다음 각각 100ns, 10μs 및 10ms의 다양한 펄스 너비로 + 5V 펄스에 의해 인가되었습니다. 저항은 0.1V에서 판독되었습니다. 그림 3a와 같이 LRS에서 중간 저항 상태 또는 HRS로의 해당 저항 전환이 달성되었습니다. 그림 3b는 반대 극성 펄스에 의해 유도된 HRS에서 LRS까지의 연속적인 RS 사이클을 보여줍니다. 결과는 다양한 폭의 펄스 전압에 의해 다중 레벨 저항을 얻을 수 있음을 확인합니다. 각 저항 상태의 유지 속성을 추가로 조사한 결과 저항 크기의 큰 변화는 관찰되지 않았습니다(추가 파일 1:그림 S1 참조). 그림 3c는 펄스 전압으로 제어되는 일반적인 비휘발성 저항성 메모리 루프를 보여줍니다. Pt/Nd:STO/In 장치는 먼저 − 3 V의 펄스에 의해 LRS로 설정되었고, 그 다음 펄스 전압을 + 2 V(또는 + 3, + 4 및 + 5 V)로 스위핑하고 다시 - 3으로 설정했습니다. 100ms 펄스 폭의 V. 저항은 0.1V에서 판독되었습니다. 일련의 중간 저항 상태는 펄스 크기를 조정하여 얻을 수 있습니다. 그림 3a–c에서 Pt/Nd:STO/In 장치의 다중 레벨 저항 상태는 펄스 폭 또는 크기를 조정하여 달성할 수 있으며, 이는 장치가 멤리스터처럼 동작함을 나타냅니다[23, 30 ].

<그림><그림><소스 유형="이미지/webp" srcset="//media.springerature.com/lw685/springer-static/image/art%3A10.1186%2Fs11671-018-2433-5/MediaObjects/ 11671_2018_2433_Fig3_HTML.gif?as=webp">

연속 RS 주기 a LRS에서 HRS 및 b로 HRS에서 LRS로. 이 장치는 먼저 100ms 너비의 − 5V(+ 5V) 펄스에 의해 LRS(HRS)로 설정된 다음 100ns, 10μs, 및 10ms입니다. LRS(HRS)에서 중간 저항 상태 또는 HRS(LRS)로의 해당 저항 전환. ㄷ R –V 펄스 전압에 의해 제어되는 히스테리시스 루프. Pt/Nd:STO/In 장치는 먼저 − 3 V의 펄스로 LRS로 설정한 다음 펄스를 + 2 V(또는 + 3, + 4, + 5 V)로 스위핑하고 다시 - 3 V로 스윕합니다. 100ms 펄스 폭. 모든 저항은 0.1V

에서 읽혔습니다.

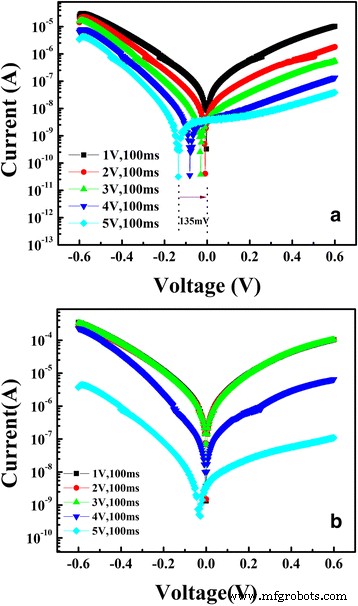

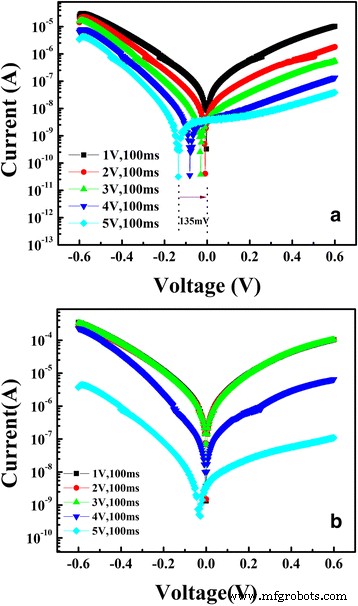

일반적으로 조명된 파장이 활성 물질의 광학 밴드갭과 일치할 때 전하 캐리어의 광여기가 발생하는 것으로 알려져 있습니다. 생성된 전자와 정공은 내부 전기장에 의해 분리되어 PV 효과가 발생합니다[23,24,25]. Pt/Nd:STO/In 장치의 경우 다중 레벨 메모리 상태가 주로 Pt/Nd:STO 인터페이스 근처의 공핍층에 의해 결정되면 PV 효과는 메모리 상태에 따라 달라질 것으로 예상됩니다. 장치. 반대로 RS 프로세스 동안 공핍층이 변경되지 않은 상태로 유지되면 PV는 메모리 상태와 관련이 없습니다. 더 흥미롭게도 우리는 Pt/Nd:STO/In 장치에 대한 메모리 상태 종속 PV 효과를 발견했습니다. 그림 4a, b는 I를 보여줍니다. –V 100ms로 + 1 ~ + 5 V의 일련의 펄스로 전환한 후 저 바이어스 영역(- 0.6 ~ + 0.6 V)에서 곡선 , 각각. 조명 아래에서 나 –V HRS의 곡선은 전압 축을 따라 현저한 이동을 나타내며 개방 회로 전압(Voc)(제로 전류에서의 전압)은 ~ 135mV만큼 높습니다. 일련의 중간 저항 상태에 해당하는 Voc은 장치 저항이 감소함에 따라 점차 감소하며 LRS의 경우 무시할 수 있을 정도로 작습니다. I의 경우 거의 변화가 관찰되지 않았습니다. –V 어둠 속에서 측정한 곡선. 유사한 결과가 Hu et al. [23]. 또한, Voc에 대한 테스트 방법은 Shang et al.에 의해 보고되었습니다. [24,25,26]. 이 방법에 따라 LRS와 HRS에서 Voc를 추가로 측정하였다. 예상대로 전압 상승은 조명에 의해 생성되고 Voc는 접합 저항에 따라 달라집니다(추가 파일 1:그림 S2 참조). 위의 결과는 Voc의 크기가 Pt/Nd:STO/In 소자의 메모리 상태에 의존함을 증명한다.

<그림><그림><소스 유형="이미지/webp" srcset="//media.springerature.com/lw685/springer-static/image/art%3A10.1186%2Fs11671-018-2433-5/MediaObjects/ 11671_2018_2433_Fig4_HTML.gif?as=webp">

나 –V a에서 100ms(LRS에서 중간 저항 상태 및 HRS로 전환)로 + 1 ~ + 5 V의 일련의 전압 펄스로 전환한 후 저 바이어스 영역(- 0.6 ~ + 0.6 V)의 곡선 조명 조명 및 b 각각 어둡게

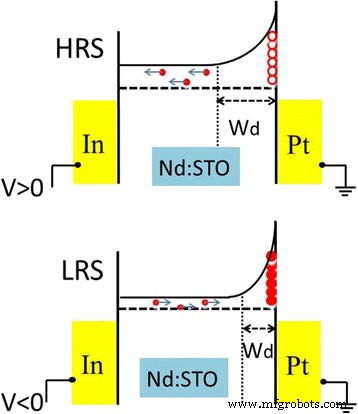

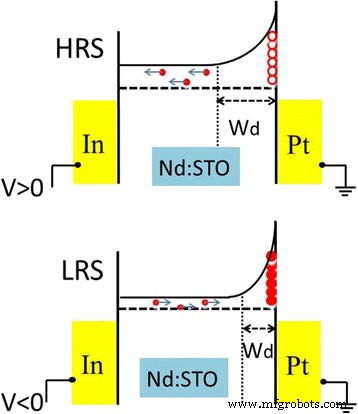

Pt/Nd:STO/In 장치의 다중 레벨 메모리 및 메모리 상태 종속 PV 효과는 메모리 상태가 주로 Pt/Nd:STO 인터페이스 근처의 공핍층에 의해 결정된다는 것을 분명히 암시합니다. 즉, Pt/Nd:STO 인터페이스 근처의 쇼트키 장벽 너비와 높이는 스위핑 전압에 의해 변조됩니다. 그림 1b의 Raman 결과에 따르면 Nd:STO 표면에 일부 결함(예:산소 결손)이 존재합니다. 소자에 음의 전압이나 펄스가 가해지면 In 전극에서 주입된 전자가 Pt/Nd:STO 계면의 결함에 의해 포획됩니다. 갇힌 전자는 더 좁고 더 낮은 쇼트키 장벽으로 이어져 LRS가 발생합니다. 대조적으로, 다가오는 포지티브 바이어스 스위핑 동안, 갇힌 전자는 공핍 영역의 존재로 인해 방출되어 HRS가 발생합니다. 또한 결함의 공간적 분포가 고르지 않아야 합니다. 고밀도 결함에 페르미 피닝(Fermi Pinning)이 형성될 수 있어 인가된 바이어스가 제거될 때 HRS와 LRS를 유지할 수 있다. 공핍층은 펄스 폭이나 크기로 조정할 수 있으므로 다중 레벨 메모리 상태가 관찰되었습니다. 그림 5는 Pt/Nd:STO 인터페이스에서 전자 트랩핑 또는 디트래핑 프로세스에 대한 개략도를 보여줍니다.

<그림><그림><소스 유형="이미지/webp" srcset="//media.springerature.com/lw685/springer-static/image/art%3A10.1186%2Fs11671-018-2433-5/MediaObjects/ 11671_2018_2433_Fig5_HTML.gif?as=webp">

HRS 및 LRS에서 에너지 밴드 구조 및 인터페이스 상태 Pt/NSTO/In 시스템의 개략도. 인터페이스의 빨간색 속이 빈 구체와 속이 빈 구체는 각각 비어 있는 인터페이스 상태와 점유된 인터페이스 상태를 나타냅니다.

메모리 상태 종속 PV 효과는 다른 메모리 상태에서 Pt/Nd:STO 인터페이스 장벽의 다른 너비와 높이에 의해 유도됩니다. 공핍 영역이 더 넓은 HRS는 조명 조명 아래 공핍 영역에서 더 많은 전자-정공 쌍을 생성합니다. 광 생성된 전자는 HRS에서 강한 상향 밴드 굽힘에 의해 Nd:STO 벌크로 구동되고 홀은 장벽을 통해 터널링되어 더 높은 Voc를 생성합니다. 반대로, 더 낮고 더 좁은 공핍 영역을 갖는 LRS는 더 낮은 Voc를 초래합니다. 일반적으로 Voc는 Pt/Nd:STO/In 장치의 다중 레벨 메모리 상태에 해당하는 인터페이스 장벽 너비와 높이에 따라 달라집니다.

메모리 상태와 PV 효과는 모두 스위칭 바이어스에 대한 유사한 의존성을 나타내며, 이는 Nd:STO 인터페이스의 전자 고갈/축적과 관련된 공유 메커니즘을 나타내며, 이는 인터페이스 장벽 및 인터페이스 전하 재분배의 중요성을 나타냅니다(그림 1). 5). PV 효과는 내부 전기장에 의해 분리된 광 생성 전자와 정공에 의해 유도됩니다. 따라서 Pt/Nd:STO/In 장치에서 관찰된 메모리 상태 종속 PV 효과는 RS가 전도성 필라멘트의 형성이 아니라 Pt/Nd:STO 인터페이스의 쇼트키 장벽의 바이어스 유도 변조에 의해 유도된다는 것을 증명합니다. Voc은 메모리 상태에 의존하므로 이러한 저항 상태 의존 PV 효과는 기존의 저항 판독값 외에 RS 장치의 메모리 상태를 감지하기 위해 Voc를 사용하여 새로운 경로를 제공합니다[23]. 조명이 장치의 메모리 상태를 변경하지 않기 때문에 이 새로운 판독 경로는 비파괴적이고 신뢰할 수 있습니다.

결론

요약하면, 우리는 단결정 Nd:STO 기반 멤리스틱 소자의 RS 및 PV 특성을 조사했습니다. RS 효과는 Pt와 n형 Nd:STO 단결정 계면 근처의 쇼트키 접합과 관련이 있습니다. 메모리 상태는 펄스 폭 또는 크기로 변조될 수 있습니다. Pt/Nd:STO/In 장치의 메모리 상태 종속 PV 효과는 스위칭 전압에 의해 얻어집니다. 이러한 보완 효과는 Pt/Nd:STO 인터페이스에서 캐리어 주입 및 트래핑/디트래핑 프로세스로 인해 발생하는 Pt/Nd:STO 인터페이스의 높이와 너비 모두에서 인터페이스 장벽의 바이어스 유도 변조에 기인합니다. . 결과는 RS/PV 효과와 인가된 전기장에 의해 트리거된 Nd:STO 인터페이스 변조 사이에 강력한 연결을 설정하고 Voc를 사용하여 여러 비휘발성 메모리 상태를 비파괴적으로 감지함으로써 새로운 경로를 제공합니다.

약어

- HRS:

-

고저항 상태

- 나 –V :

-

전류-전압

- LRS:

-

저저항 상태

- PV:

-

광전압

- RRAM:

-

저항 랜덤 액세스 메모리

- RS:

-

저항 전환

- XRD:

-

X선 회절