나노물질

본 논문에서는 TCAD 시뮬레이션을 통해 실리콘 기반의 T자형 게이트 듀얼 소스 터널 전계 효과 트랜지스터(TGTFET)를 제안하고 조사한다. 대조 연구로서 TGTFET, LTFET, UTFET의 구조, 특성, 아날로그/RF 성능에 대해 논의한다. T자형 게이트에 의해 도입된 게이트 오버랩은 터널링 접합의 효율성을 향상시킬 수 있습니다. TGTFET의 이중 소스 영역은 온 상태 전류(I 켜기 ) 이중 터널링 접합 영역을 제공함으로써. 장치 성능을 더욱 향상시키기 위해 TGTFET에 n+ 포켓을 도입하여 대역 간 터널링 속도를 더욱 높였습니다. 시뮬레이션 결과는 TGTFET의 I 켜기 및 스위칭 비율(I 켜기 /나 꺼짐 ) 81μA/μm 및 6.7 × 10 10 에 도달 1V 게이트에서 소스 전압(V g ). TGTFET의 평균 하위 임계값 스윙(SSavg , 0~0.5V V g ) 51.5mV/dec에 도달하고 TGTFET의 최소 하위 임계값 스윙(SSmin) , 0.1V V에서 g ) 24.4mV/dec에 도달합니다. 더욱이, TGTFET는 DIBL(드레인 유도 장벽 저하) 효과에 대한 강력한 강인함을 가지고 있음이 밝혀졌습니다. TGTFET 설계 지침을 작성하기 위해 도핑 농도, 기하학적 치수 및 인가 전압이 소자 성능에 미치는 영향을 조사합니다. 또한, 트랜스컨덕턴스(g m ), 출력 컨덕턴스(g ds ), 게이트 대 소스 커패시턴스(C gs ), 게이트-드레인 커패시턴스(C 지 ), 차단 주파수(f T ) 및 TGTFET의 이득 대역폭(GBW)은 0.5V 드레인-소스 전압(V d ), 각각. TGTFET는 구조적 이점을 활용하여 UTFET 및 LTFET에 비해 더 나은 DC/AC 특성을 얻습니다. 결론적으로, 상당히 우수한 성능으로 인해 TGTFET는 차세대 저전력 및 아날로그/RF 애플리케이션을 위한 매우 매력적인 선택이 되었습니다.

<섹션 데이터-제목="배경">금속 산화물 반도체 전계 효과 트랜지스터(MOSFET)의 축소는 집적 회로(IC) 전력 소비, 스위칭 특성, 회로 기능 및 IC 밀도에서 상당한 개선을 가져옵니다[1, 2]. 그러나 공급 전압의 스케일링과 오프 상태 누설 전류의 감소 사이의 양립할 수 없는 모순(I 꺼짐 ) 결국 허용할 수 없는 높은 전력 소비를 초래할 것입니다[3]. 동시에, 단채널 효과(SCE)로 인한 신뢰성 저하가 점점 더 심각해지고 있습니다[4, 5]. 이러한 문제를 해결하려면 하위 임계값 스윙(SS)과 장치의 공급 전압을 줄이는 것이 유효합니다. 대역 간 터널링 메커니즘을 기반으로 하는 터널 전계 효과 트랜지스터(TFET)는 60mV/dec 미만의 하위 임계값 스윙(SS)에 도달하고 공급 전압을 효과적으로 낮출 수 있습니다[6,7,8,9,10]. . 또한 소스 근처에 터널링 접합이 있기 때문에 TFET는 일반적으로 작은 게이트 대 소스 커패시턴스(C gs ) [1, 11] 장치 주파수 성능에 유리합니다.

최근 연구에 따르면 TFET는 미래의 저전력 애플리케이션[12,13,14,15,16] 및 아날로그/RF 애플리케이션[17,18,19]을 위한 유망한 후보인 것 같습니다. 그러나 작은 유효 터널링 영역으로 인해 제한된 터널링 전류가 기존 P-I-N TFET의 고유한 단점이 되어 낮은 온 상태 작동 전류(I 켜기 ). TFET 성능을 향상시키기 위해 최근 몇 년 동안 많은 새로운 구조가 제안되었습니다[20,21,22,23,24,25]. 리세스된 게이트의 이점을 활용하여 L자형 터널 전계 효과 트랜지스터(LTFET)[23, 24] 및 U자형 터널 전계 효과 트랜지스터(UTFET)[25]가 높은 I 켜기 컴팩트한 장치 구조로 그러나 LTFET 및 UTFET에서는 여전히 개선의 여지가 많으며 이러한 장치의 아날로그/RF 성능을 연구하기 위해 더 많은 노력을 기울여야 합니다.

이 논문에서는 이중 소스를 갖는 T자형 게이트 이중 소스 터널 전계 효과 트랜지스터(TGTFET)를 제시하고 TCAD 시뮬레이션을 통해 연구합니다. 설계된 TGTFET는 LTFET 및 UTFET에 비해 터널링 접합 영역을 두 배로 늘릴 수 있습니다. 설계된 T자형 게이트에 의해 도입된 게이트 중첩은 대역 대 대역 터널링 속도(BBT rate)를 향상시킬 수 있습니다. 시뮬레이션 결과는 제안된 TGTFET가 더 높은 I 켜기 (8.1 × 10 − 5 V에서 A/μm d =1 V) 동일한 조건에서 LTFET 및 UTFET보다 둘 다 SSmin (V에서 g =0.1 V) 및 SS평균 (0~0.5V V g ) TGTFET의 60mV/dec(각각 24.4mV/dec 및 51.5mV/dec)보다 낮습니다. TGTFET는 더 나은 입력/출력 특성을 얻습니다(g m =232μS/μm, g ds =214μS/μm) UTFET 및 LTFET보다 또한 TGTFET, UTFET, LTFET의 커패시턴스 특성에 대해 자세히 설명합니다. 마지막으로, TGTFET는 더 나은 아날로그/RF 성능을 얻습니다(f T =11.9GHz 및 GBW =2.3GHz) UTFET 및 LTFET와 비교 그 결과, 상당히 우수한 성능을 갖는 TGTFET를 얻을 수 있다. 이 논문의 구조는 다음과 같다:"방법" 섹션에는 TGTFET, LTFET[23, 24] 및 UTFET[25]의 구조 및 매개변수에 대한 설명이 포함되어 있습니다. ] 뿐만 아니라 TCAD 시뮬레이션 방법. "결과 및 토론" 섹션에는 시뮬레이션 결과에 대한 설명이 포함되어 있습니다. 이 섹션에서는 TGTFET의 메커니즘, 특성 및 아날로그/RF 성능을 연구하고 LTFET 및 UTFET과 비교합니다. TGTFET에 대한 장치 매개변수의 영향도 자세히 분석됩니다. "결론" 섹션은 이 백서의 결론을 제공합니다.

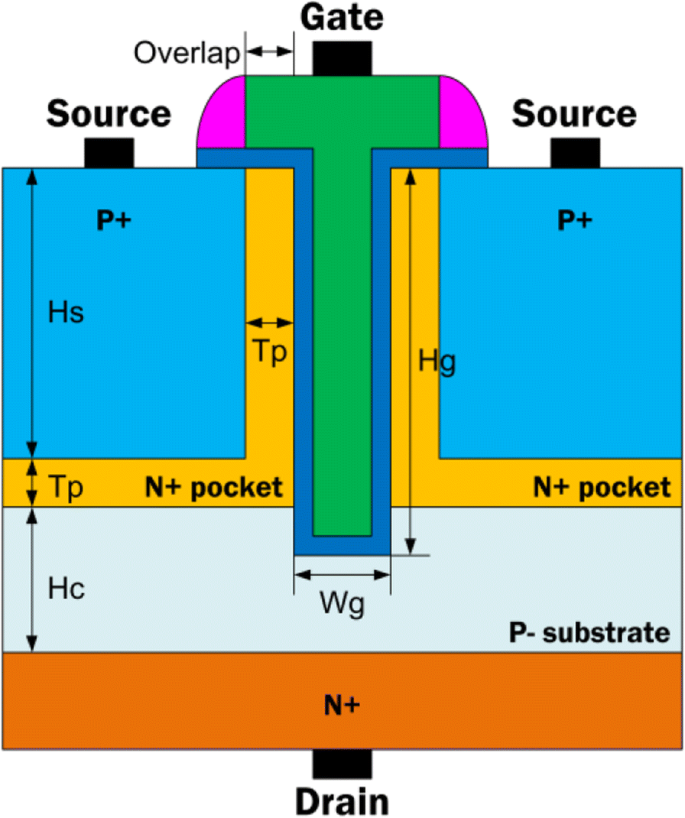

T자형 게이트 듀얼 소스 터널 전계 효과 트랜지스터(TGTFET)의 구조는 그림 1에 나와 있습니다. 게이트의 모양은 알파벳 문자 "T"(녹색 영역)와 유사합니다. 이중 소스 영역은 게이트의 두 측면(사파이어 영역)에 있습니다. 채널 터널링 속도를 높이기 위해 두 개의 n+ 포켓(노란색 영역)이 삽입되었습니다[20,21,22]. n+ 드레인은 채널 바닥에 배치됩니다. 따라서 T자형 게이트는 수직 및 측면 방향 모두에서 n+ 포켓과 중첩됩니다. 이러한 방식으로 터널링 접합 상단의 전기장이 증가할 수 있습니다. 전기장 향상은 에너지 밴드를 더 가파르게 휘게 만듭니다. 마지막으로 코너 전계 향상으로 인해 전자 터널링 속도가 향상됩니다[26].

<그림>

제안된 T자형 게이트 이중 소스 터널 전계 효과 트랜지스터(TGTFET)의 개략도

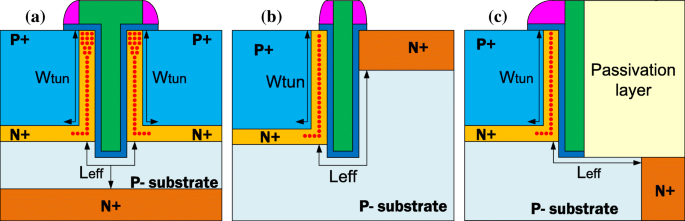

그림 2는 LTFET[23, 24], UTFET[25] 및 TGTFET의 장치 구조를 보여줍니다. 게이트 오버랩은 TGTFET의 터널링 효율을 향상시키는 데 도움이 될 수 있습니다. TGTFET의 이중 소스 영역은 LTFET 및 UTFET에 비해 터널링 접합 영역을 두 배로 늘릴 수 있습니다.

<그림>

a의 비교 제안된 TGTFET, b UTFET 및 c LTFET

시뮬레이션에 사용된 실리콘 기반 TGTFET, UTFET 및 LTFET의 매개변수는 Hs =30nm(소스 영역 높이), Hg =40nm(리세스 게이트 높이), Wg =6nm(폭 게이트 영역), Hc =15nm(채널 영역 높이), Tp =5nm(n+ 포켓의 두께), ϕ =4. 33eV(게이트 작업 함수), Tox =2nm(HfO2의 두께 게이트 유전체), N S =1 × 10 20 cm −3 (p+ 소스 도핑 농도), N D =1 × 10 19 cm −3 (n+ 드레인 도핑 농도), N 서브 =1 × 10 17 cm −3 (p- 기판 도핑 농도) 및 N P =5 × 10 18 cm −3 (n+ 포켓 도핑 농도). 시뮬레이션의 너비 계수는 기본적으로 1μm입니다.

TGTFET, UTFET 및 LTFET의 시뮬레이션은 실바코 아틀라스 TCAD 도구에서 수행됩니다. Non-local BTBT 모델이 이 시뮬레이션에서 도입되어 에너지 대역 공간 변화를 고려하여 BTBT 터널링 프로세스의 정확도를 높이는 데 도움이 될 수 있습니다. Lombardi 이동성 모델은 채널 이동성을 보다 정확하게 만들기 위해 고려됩니다(가로 필드 및 도핑 농도를 포함한 표면 산란 고려). 페르미 통계 및 밴드 갭 축소 모델은 고도로 도핑된 영역의 효과에 맞게 고려됩니다. 본 논문에서도 Shockley-Read-Hall 재조합 모델을 고려하였다.

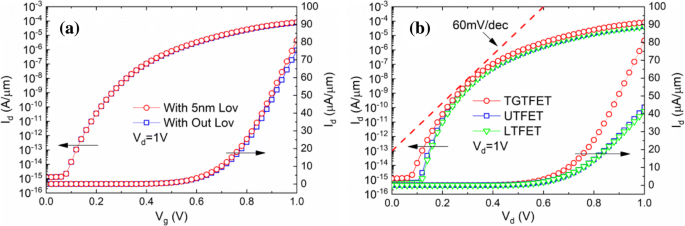

그림 3a는 게이트 중첩이 있거나 없는 TGTFET의 전달 특성을 보여줍니다. 추가 게이트 오버랩으로 I 켜기 7.5 × 10 −5 에서 증가 ~ 8.1 × 10 −5 A/μ m at V g =V d =1 V. 그림 3b는 TGTFET, UTFET 및 LTFET의 전달 특성 곡선을 보여줍니다. 보다 정확한 비교를 위해 이 세 장치의 시뮬레이션 모델과 기하학적 치수를 동일하게 설정했습니다. 결과적으로 TGTFET는 I 켜기 그림 3b와 같이 LTFET 및 UTFET와 비교합니다. SS분 TGTFET의 값은 V에서 24.4mV/dec입니다. g =0.1 V 및 SS평균 0V <V일 때 51.5mV/dec g <0.5 V. 스위칭 비율(I 켜기 /나 꺼짐 ) 6.7 × 10 10 V에서 g =V d =1 V 및 6.5 × 10 8 V에서 g =V d =0.5 V.

<그림>

시뮬레이션된 a 게이트 오버랩이 있거나 없는 TGTFET의 전송 특성 및 b TGTFET, UTFET 및 LTFET의 전송 특성

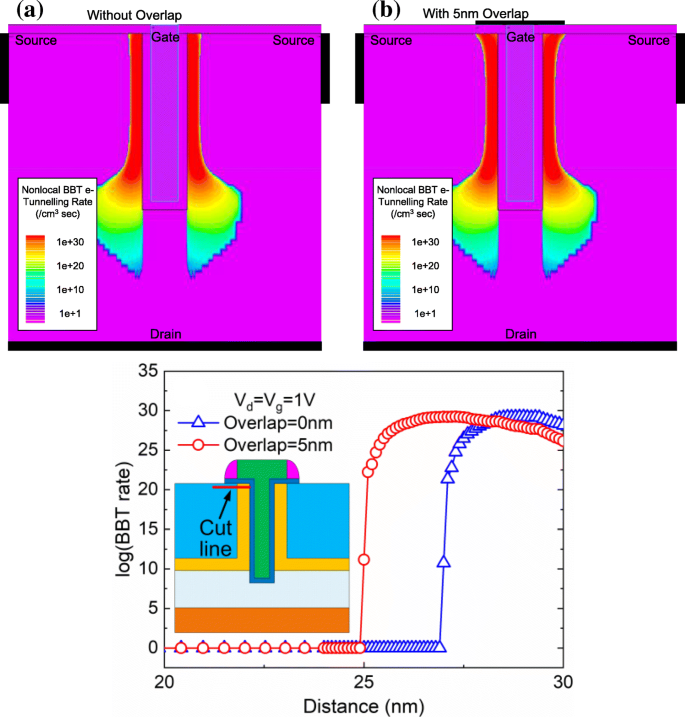

그림 4a, b는 5nm 게이트 오버랩이 있거나 없는 TGTFET의 BBT 속도를 보여줍니다. 그림 4c에서 5nm 게이트 오버랩이 있는 장치가 장치 표면 아래에 더 넓은 전자 터널링 영역을 가지고 있음을 분명히 알 수 있습니다. 이는 I 켜기 증가합니다.

<그림>

a의 시뮬레이션된 BBT 전자 터널링 속도 다이어그램 게이트 겹침이 없는 장치, b 5nm 게이트 오버랩이 있는 장치 및 c 기기 표면 아래 1nm에서 두 기기의 BBT 전자 터널링 속도 V g =V d =1 V

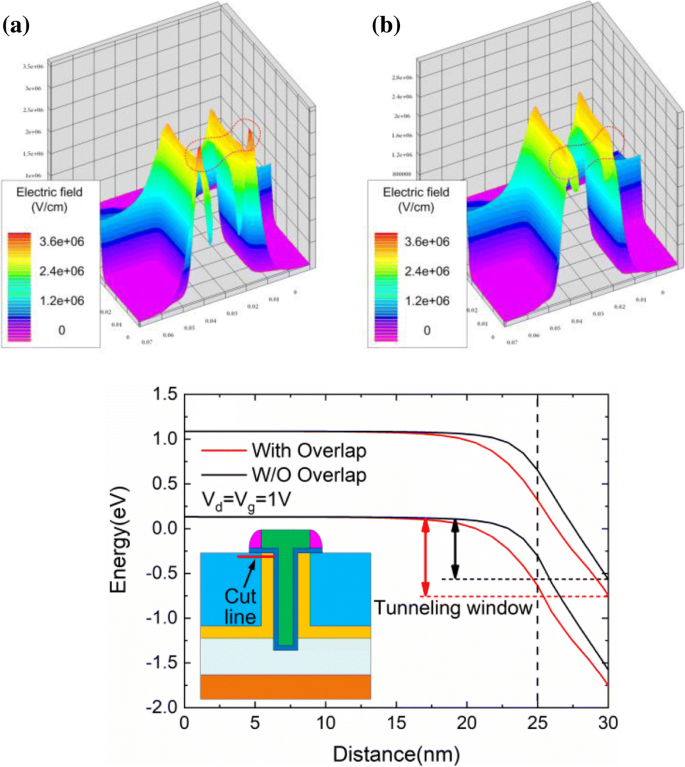

그림 5a, b는 게이트 중첩이 있거나 없는 TGTFET의 전기장의 3D 다이어그램을 보여줍니다. 두 개의 전기장 피크가 그림 5a의 점선 원에 표시된 것처럼 5nm 게이트 중첩과 함께 TGTFET에 나타납니다. 게이트 겹침이 없기 때문에 그림 5b에는 전기장 피크가 나타나지 않습니다. 그림 5c는 기기 표면 아래의 에너지 밴드 구조를 보여줍니다. 그림 5c의 삽입은 절단선 위치를 보여줍니다. 게이트 오버랩을 사용하면 더 큰 터널링 창을 얻을 수 있습니다. 따라서 더 높은 BBT 비율과 I 켜기 달성할 수 있습니다.

<그림>

a 장치의 전기장의 3D 개략도 중복 및 b 겹치지 않고; 시뮬레이션된 c 소스에서 포켓 영역까지의 에너지 밴드 다이어그램(산화물 인터페이스 아래 1nm)

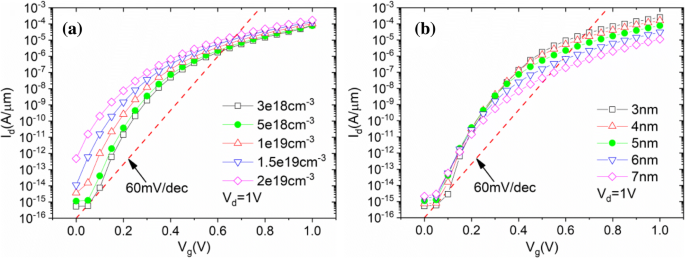

그림 6은 n+ 포켓이 TGTFET의 성능에 미치는 영향을 보여줍니다. 나 꺼짐 그림 6a와 같이 n+ 포켓 도핑 농도가 증가함에 따라 급격히 증가합니다. 더 낮은 SS와 더 큰 I 켜기 N일 때 n+ 포켓(Tp)의 두께를 7nm에서 3nm로 줄임으로써 얻을 수 있습니다. P =5 × 10 18 cm −3 , 그림 6b와 같이. 동시에 그림 6b에는 중요한 하위 임계값 전류가 표시되지 않습니다. 그림 6a에서 n+ pocket의 상대적으로 낮은 도핑 농도가 subthreshold 전류를 억제하는 데 도움이 됨을 확인할 수 있습니다.

<그림>

n+ 포켓 a가 다른 시뮬레이션된 드레인 전류 농도 및 b V에서의 두께 d =1 V

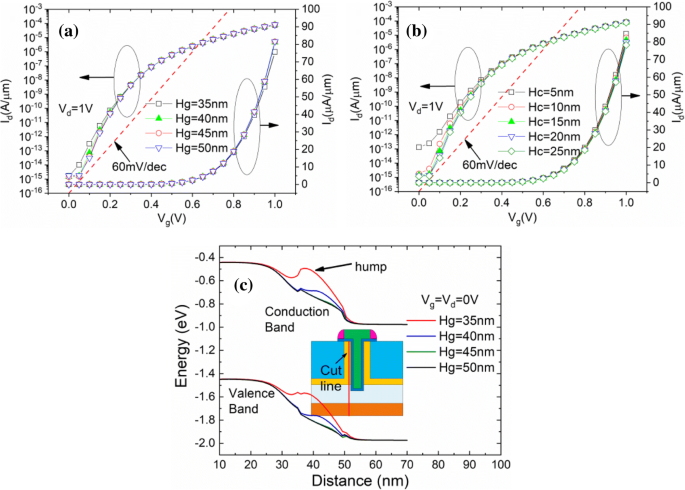

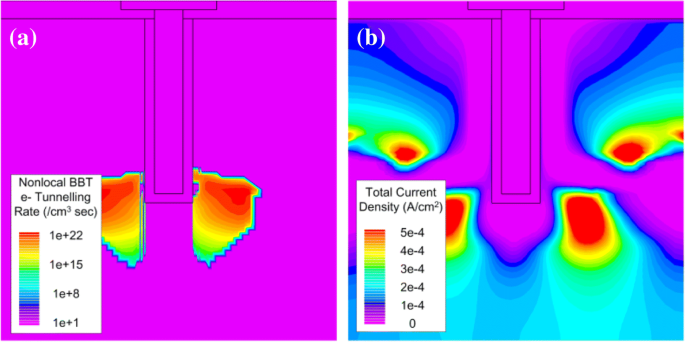

게이트 높이(Hg)와 채널 두께(Hc)의 영향은 그림 7a, b에 별도로 나와 있습니다. 작은 나 켜기 Hg가 증가하면 SS 개선이 나타납니다. Hg =35 nm 일 때 온 상태 전류 경로에 명백한 에너지 밴드 혹이 있기 때문에 그림 7c와 같이 운이 좋은 전자(터널링 접합을 통과한 전자)에 특정 장애물이 되어 다음과 같은 결과를 초래할 수 있습니다. 나 켜기 감소하다. Hg가 증가하면 에너지 밴드 혹이 약해져서 I 켜기 및 SS 개선. 약간의 나 켜기 그림 7b와 같이 Hc가 감소함에 따라 개선이 이루어집니다. 그러나 Hc가 5nm로 감소하면 임계값 이하 특성의 심각한 저하가 관찰될 수 있습니다. 이는 그림 8과 같이 n+ 포켓의 모서리에서 하위 임계값 터널링 전류가 증가하는 것으로 설명할 수 있습니다. 그림 8a는 Hc =5nm일 때 명백한 오프 상태 대역 대 대역 터널링 현상을 보여주고 그림 8b는 그림 8b를 보여줍니다. 나 꺼짐 Hc =5 nm일 때의 전류 밀도.

<그림>

a가 있는 TGTFET의 시뮬레이션된 전송 특성 다른 Hg, b 다른 Hc 및 c 현재 경로의 전도대 혹

<그림>

오프 상태 a의 시뮬레이션된 다이어그램 BTBT 전자 터널링 속도 및 b Hc =5 nm

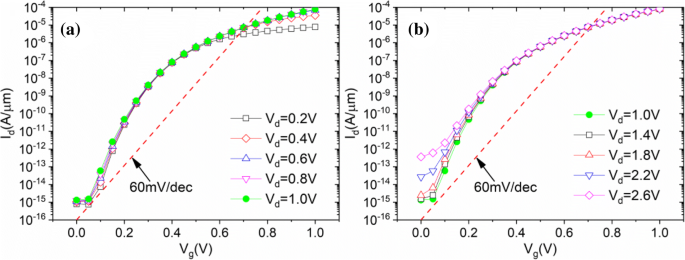

일 때의 전류 밀도그림 9와 같이 드레인 대 소스 전압의 영향(V d )도 이 논문에서 고려된다. V를 위해 d <0.6 V, 나 켜기 V가 증가함에 따라 분명히 증가합니다. d , 그림 9a와 같이. 이는 V가 증가함에 따라 p-채널의 잠재력이 서서히 증가하고 있다는 사실로 설명됩니다. d 결과적으로 p-채널의 저항이 감소합니다. V를 위해 d> 1.8 V, 그림 9b에 표시된 I 켜기 V가 증가함에 따라 거의 증가하지 않음 d 하지만 나 꺼짐 상당히 증가합니다. 이는 V가 증가함에 따라 급격히 증가하는 n+ 포켓의 모서리에서 하위 임계값 터널링 전류 때문입니다. d . 마지막으로 0.6V <V의 경우 d <1.8V, TGTFET는 양호하고 안정적인 성능을 나타냅니다. 결과적으로 TGTFET는 DIBL(드레인 유도 장벽 저하)에 강하고 더 큰 적용 전압 동적 범위에서 우수하고 안정적인 성능을 나타냅니다.

<그림>

a에 대한 시뮬레이션된 드레인 전류 V d ≤ 1 V 및 b V d ≥ 1 V

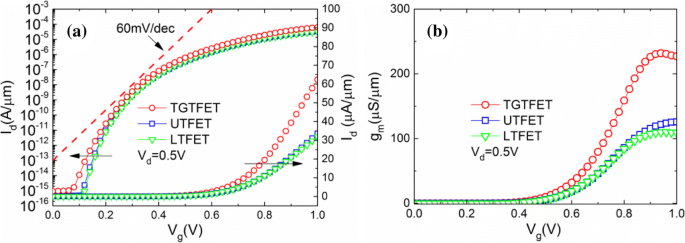

그림 10은 V에서 TGTFET, UTFET, LTFET의 전달 특성 및 트랜스컨덕턴스 곡선을 보여줍니다. d =0.5 V. 트랜스컨덕턴스(g m )은 Eq와 같이 전달 특성 곡선의 1차 도함수로부터 얻을 수 있습니다. (1) [27,28,29]:

$$ {g}_{\mathrm{m}}={dI}_{\mathrm{d}s}/{dV}_{\mathrm{gs}} $$ (1) <그림><소스 유형="image/webp" srcset="//media.springerature.com/lw685/springer-static/image/art%3A10.1186%2Fs11671-018-2723-y/MediaObjects/11671_2018_2723_Fig10_HTML.png?

아 전송 특성 및 b V에서 TGTFET, UTFET 및 LTFET의 트랜스컨덕턴스 곡선 d =0.5V

결과적으로 TGTFET(232μS/μm)의 최대 트랜스컨덕턴스는 그림 10과 같이 UTFET(120μS/μm) 및 LTFET(110μS/μm)보다 약 2배 더 큽니다. 듀얼 소스 및 게이트 오버랩으로 인한 전류 게인

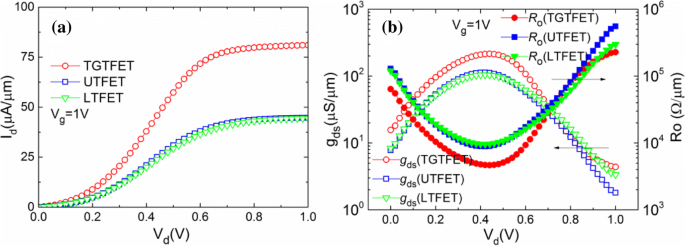

그림 11은 출력 특성, 출력 컨덕턴스(g ds ) 및 출력 임피던스(R 오 ) TGTFET, UTFET 및 LTFET의 곡선. 그림 11a와 같이 V의 증가에 따라 소자의 출력전류가 증가함을 명확히 알 수 있다. d , 그러나 V일 때 d 0.6V 이상에 도달하면 출력 전류가 포화되는 경향이 있습니다. 관찰을 통해 TGTFET의 출력 전류가 UTFET 및 LTFET의 출력 전류보다 2배 더 크다는 것을 쉽게 알 수 있다. 그림 11b는 출력 컨덕턴스를 보여줍니다(g ds ) 및 출력 임피던스(R 오 ) TGTFET, UTFET 및 LTFET의 곡선. 지 ds 식과 같이 출력 전류의 유도를 통해 얻을 수 있습니다. (2) [27, 29] 동안 R 오 출력 컨덕턴스의 역수로 표현할 수 있습니다.

$$ {g}_{\mathrm{ds}}={dI}_{\mathrm{ds}}/{dV}_{\mathrm{ds}} $$ (2) <그림><소스 유형=" image/webp" srcset="//media.springerature.com/lw685/springer-static/image/art%3A10.1186%2Fs11671-018-2723-y/MediaObjects/11671_2018_2723_Fig11_HTML.p">

아 출력 특성, b 출력 컨덕턴스(g ds ) 및 c 출력 임피던스(R 오 ) TGTFET, UTFET 및 LTFET의 곡선

출력 전류의 이점으로 인해 TGTFET는 가장 높은 g를 얻습니다. ds 최소 R 오 이 세 가지 장치 중. 1V 게이트 바이어스 조건에서 TGTFET는 최대 g ds 214μS/μm 및 최소 R 오 4.6kΩ/μm의 0.45V V 미만 d . 동일한 게이트 바이어스 조건에서 UTFET 및 LTFET는 최대 g ds 113μS/μm 및 105μS/μm 및 최소 R 오 0.4V V 미만에서 9.0kΩ/μm 및 9.6kΩ/μm d .

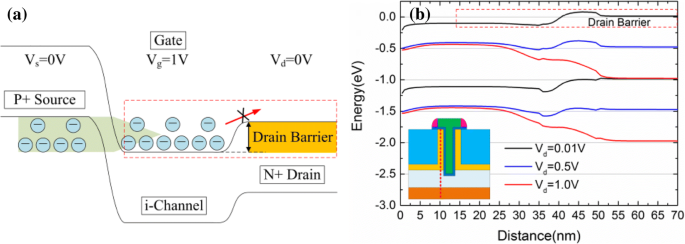

또한, 그림 11에서 디바이스 출력 특성의 선형 영역이 일정한 비선형성을 보이는 것을 찾는 것은 어렵지 않다. 그림 11a와 같이 R 오 먼저 감소한 다음 V가 증가함에 따라 증가합니다. d . 일부 연구 그룹에서는 이 현상에 대한 해당 물리적 과정을 제시하고 있지만[7, 30], 아직 명확하게 설명되지 않은 문제가 있습니다. 우리가 알고 있듯이, R 오 채널 영역과 터널링 접합의 저항에 의해 결정됩니다. V일 때 d <0.4 V, R 오 V가 증가함에 따라 감소합니다. d . V일 때 다음 상황을 고려하십시오. d =0 V 및 V g =1 V, 행운의 전자 중 어느 것도 드레인 쪽으로 스위프될 수 없으며 거의 모든 전자는 그림 12a, b의 빨간색 점선 프레임에 표시된 것처럼 비교적 높은 드레인 장벽에 의해 채널 영역에 갇힙니다. 0 V <V일 때 d <0.4 V, V 증가 d , 배수 장벽이 약해집니다(그림 12b 참조). 따라서 채널 영역에 트랩된 전자는 드레인 장벽을 통과한 다음 드레인에 의해 수집될 수 있습니다. 이것은 채널에서 드레인으로 전자의 열 여기 과정입니다. 마지막으로 터널링 접합이 완전히 켜졌기 때문에(V g =1 V), 터널링 전류는 항상 초과 상태이며 터널링 접합에 의해 도입된 저항은 무시할 수 있습니다. 이때 R 오 채널 저항 및 R에 의해 결정됩니다. 오 드레인 장벽을 가로지르는 전자 열 여기 과정에 의해 결정됩니다. 따라서 R 오 V가 증가함에 따라 감소합니다. d . V일 때 d> 0.6V, 이 세 장치는 점차 포화 영역에 들어가고 R 오 더 커집니다. V d 크면 터널링 접합을 통과하는 거의 모든 전자가 상대적으로 높은 전기장에 의해 드레인 쪽으로 휩쓸립니다. 터널링 전류는 드레인 전류의 한계가 됩니다. 이 상태에서 R 오 주로 터널링 접합부에 의해 결정됩니다. 그러나 터널링 효율성은 V 동안 크게 증가할 수 없습니다. d 증가하고있다. V d 그림 12b와 같이 터널링 접합(n+ 포켓 측)의 에너지 밴드 구조에 작은 영향을 미칩니다. 결과적으로 터널링 전류는 분명히 증가할 수 없으며 I 켜기 지속적으로 증가하는 V로 증가 d (V일 때 d> 0.6V), 이는 임피던스가 증가함을 의미합니다. 또한 0.4 V <V일 때 d <0.6 V, R 오 채널 저항과 터널링 접합에 의해 결정됩니다.

<그림>

아 V에서 에너지 밴드의 개략도 d =0 V 및 V g =1 V. b V의 다양한 바이어스에서 에너지 밴드 다이어그램의 시뮬레이션 결과 d

위의 분석에서 R 오 TFET의 감도는 터널링 프로세스와 채널 전자 열 여기 프로세스 모두에 의해 영향을 받습니다. 주요 물리적 메커니즘은 R을 지배할 수 있습니다. 오 V로 이동 d 변화. 마지막으로 R 오 먼저 감소한 다음 증가하므로 출력 특성의 비선형성이 발생합니다. 덧붙여서, 그림 11b의 관찰을 통해 TGTFET의 출력 임피던스가 UTFET 및 LTFET의 출력 임피던스보다 훨씬 작다는 것을 쉽게 알 수 있다. 이는 TGTFET의 듀얼 소스 및 측면 게이트 오버랩 구조로 인한 터널링 효율성 이점 때문입니다.

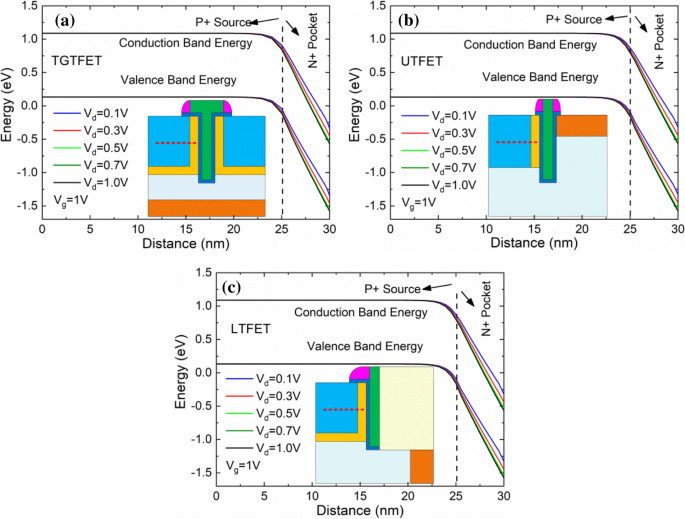

그림 13은 인가 전압이 다른 TGTFET, UTFET, LTFET의 에너지 대역 구조를 보여줍니다. 삽입된 빨간색 점선은 에너지 밴드를 그릴 위치를 나타냅니다(표면 아래 15nm, 소스 영역의 1/2 높이). V d 0.1V에서 0.5V로 증가하면 TGTFET, UTFET, LTFET의 밴드 구조가 휘어지는 경향이 뚜렷합니다. 이것은 드레인 전압이 드레인 측 근처의 터널링 접합의 전위를 끌어내릴 수 있기 때문입니다. 이는 TGTFET, UTFET 및 LTFET의 경우 V d 0.1~0.5V는 터널링 효율성에 유리합니다. 그러나 V d> 0.5V, V에 따른 에너지 대역의 변화 d 증가는 언급할 가치가 없습니다. 이는 그림 12b의 분석 결과와 일치한다.

<그림>

a의 에너지 밴드 구조 TGTFET, b UTFET 및 c V에서의 LTFET g =1

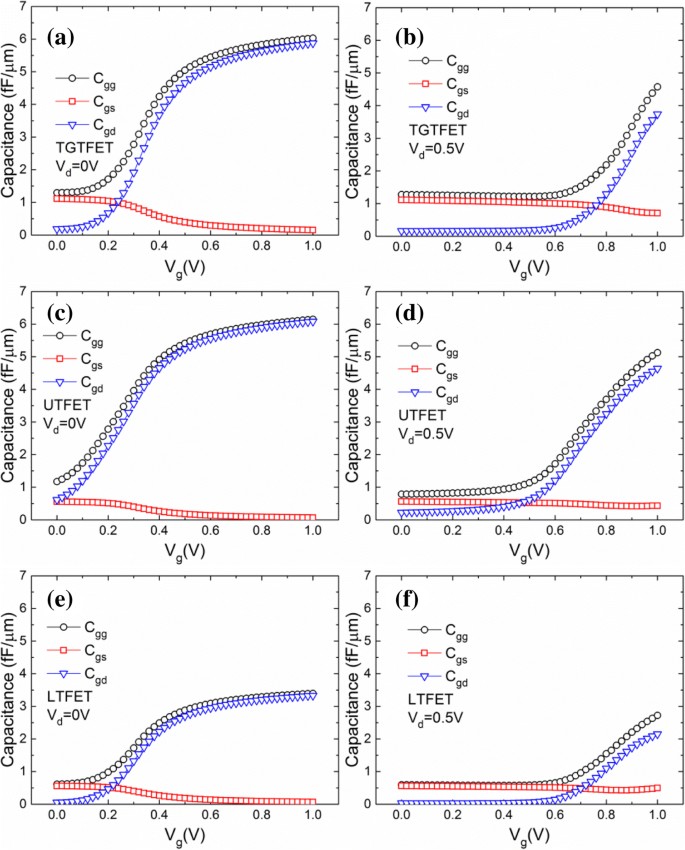

우리가 알고 있는 바와 같이, 게이트 커패시턴스(C gg )는 집적 회로의 주파수 특성에 큰 영향을 미칠 수 있습니다. TGTFET, UTFET 및 LTFET의 경우 C gg 일반적으로 C로 구성 gs (게이트 대 소스의 커패시턴스) 및 C 지 (게이트-드레인 커패시턴스). 따라서 C의 특성은 gg , C gs , 및 C 지 기기의 주파수 특성과 아날로그 적용 능력을 평가하는데 큰 의미가 있습니다. 특히 TFET의 경우 정전용량 특성이 MOSFET과 상당히 다릅니다. 소스 영역에 터널링 접합이 있기 때문에 TFET는 일반적으로 작은 C gs [1, 11]. 따라서 C gg TFET는 주로 C에 의해 결정됩니다. 지 . 그림 14는 V에 대한 TGTFET, UTFET 및 LTFET의 커패시턴스를 보여줍니다. g V 아래 d =0.5 V 및 V d =0 V, 별도로.

<그림>

TGTFET의 커패시턴스 대 V g a 아래 V d =0 V 및 b V d =0.5 V. UTFET 대 V의 커패시턴스 g c 아래 V d =0 V 및 d V d =0.5 V. LTFET의 커패시턴스 대 V g e 아래 V d =0 V 및 f V d =0.5V

그림 14a, b의 관찰을 통해 C gs 1V 게이트 전압에서 TGTFET의 값은 V에서 0.15fF/μm입니다. d =0 V 및 0.7 fF/μm(V) d =0.5 V, C보다 훨씬 작음 지 (V에서 5.8 fF/μm d =0V 및 V에서 3.7fF/μm d =0.5V). 따라서 C gg TGTFET의 는 주로 C에 의해 결정됩니다. 지 . V일 때 d =0 V, C gg 및 C 지 V가 증가함에 따라 빠르게 증가 g , 그림 14a와 같이. V가 증가하기 때문입니다. g , 전자는 장치 채널의 게이트 인터페이스에 집결되어 커패시턴스가 빠르게 상승합니다. V일 때 d =0.5 V, C 지 V까지 증가하지 않음 g 그림 14b와 같이 0.6V 이상으로 증가합니다. V g 낮으면 소수의 운 좋은 전자만이 터널링 접합을 통과하여 채널로 들어갈 수 있습니다. 이 행운의 전자 중 일부는 재결합 과정에 참여하고 나머지 대부분은 0.5V 드레인 전압으로 인해 드레인에 의해 빠르게 수집됩니다. 따라서 이러한 행운의 전자가 장치 채널에 머무르는 것은 매우 어렵습니다. 그러나 V g 증가하면 행운의 전자의 수가 급격히 증가합니다. 이 순간, 드레인 수집이나 전자-정공 재결합 과정 중 어느 것도 이러한 행운의 전자를 빠르게 고갈시킬 수 없습니다. 따라서 채널의 전자 농도가 증가하고 커패시턴스가 급격히 증가합니다. 결과적으로 커패시턴스 특성 곡선은 V가 오른쪽으로 이동하는 경향이 있습니다. d 그림 14a, b와 같이 증가합니다. 위의 분석 및 현상은 그림 14c–f와 같이 UTFET 및 LTFET에도 적용할 수 있습니다. 또한 0V 및 0.5V V에서 UTFET의 게이트 커패시턴스 d 각각 6.2fF/μm 및 5.1fF/μm에 도달했으며 LTFET의 경우 각각 3.4fF/μm 및 2.7fF/μm에 도달했습니다.

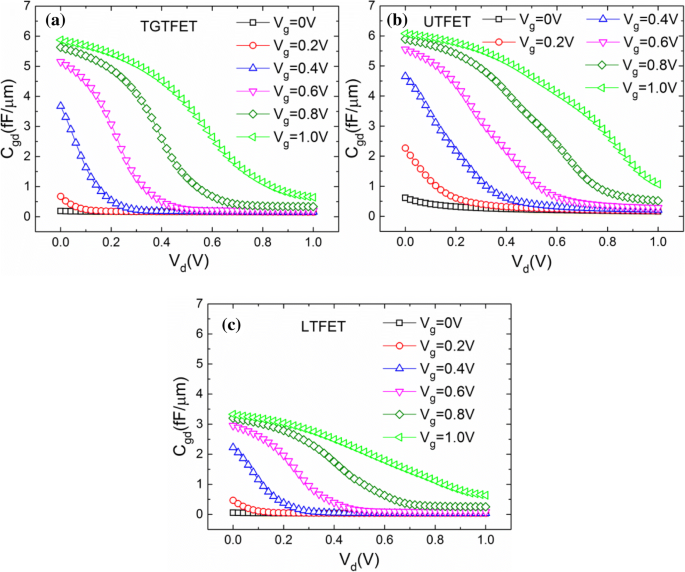

LTFET의 게이트와 드레인 사이에 직접적인 중첩이 없고 게이트와 드레인 사이의 거리가 비교적 멀기 때문에 LTFET가 가장 좋은 정전용량 특성과 가장 작은 C gg . 대조적으로, UTFET의 게이트와 드레인 사이에는 직접적인 겹침이 있습니다. 따라서 드레인 측 근처의 전자는 게이트에 의해 더 쉽게 제어되므로 큰 C gg UTFET의. TGTFET의 경우 게이트와 드레인 사이의 거리가 가깝지만 게이트와 드레인을 분리할 수 있는 약하게 도핑된 채널 영역이 있습니다. 따라서 TGTFET의 커패시턴스는 UTFET의 커패시턴스보다 좋지만 LTFET보다 약간 떨어집니다. 그림 15는 C를 보여줍니다. 지 TGTFET, UTFET 및 LTFET 대 V의 특성 d 다른 V 아래 g . 그림 15a-v의 관찰에서 C 지 이 세 장치의 특성은 유사합니다. 즉, 고정된 V g , C 지 V가 증가함에 따라 감소합니다. d . 반면에 고정된 V의 경우 d , C 지 V 증가에 따라 증가 g .

<그림>

C 지 a의 특성 TGTFET, b UTFET 및 c LTFET 대 V d 다른 V 아래 g

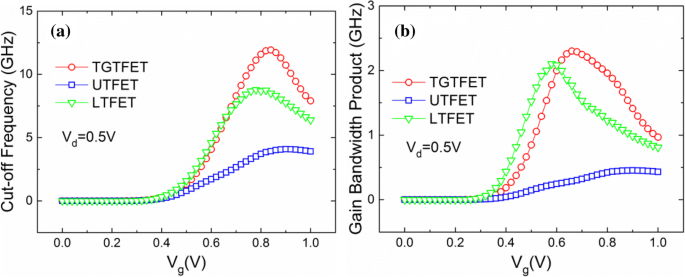

우리가 알고 있는 바와 같이, 차단 주파수(f T ) 및 이득 대역폭(GBW)은 장치의 주파수 특성을 평가하기 위한 평가 기준입니다. f T g의 비율에 따라 다릅니다. m C에게 gg , 식과 같이 (3) [30, 31]. 10과 동일한 특정 DC 이득의 경우 GBW는 g의 비율로 표현할 수 있습니다. m C에게 지 , 식과 같이 (4) [17]:

$$ {f}_T=\frac{g_{\mathrm{m}}}{2\pi {C}_{\mathrm{gs}}\sqrt{1+2{C}_{\mathrm{gd} }/{C}_{\mathrm{gs}}}}\approx \frac{g_{\mathrm{m}}}{2\pi \left({C}_{\mathrm{gs}}+{C }_{\mathrm{gd}}\right)}=\frac{g_{\mathrm{m}}}{2\pi {C}_{\mathrm{gg}}} $$ (3) $$ \ mathrm{GWB}={g}_{\mathrm{m}}/2\pi 10{C}_{\mathrm{gd}} $$ (4)그림 16은 f의 특성 곡선을 보여줍니다. T 및 TGTFET, UTFET 및 LTFET의 GBW. T자형 게이트에 의해 도입된 이중 소스 및 측면 게이트 중첩과 같은 구조적 이점의 이점을 통해 TGTFET는 UTFET 및 LTFET에 비해 가장 뛰어난 주파수 특성을 얻습니다. V 조건에서 d =0.5V, f T TGTFET의 GBW와 GBW는 각각 11.9GHz와 2.3GHz의 최대값에 도달했습니다. 게이트와 드레인 사이의 긴 거리와 게이트/드레인 겹침이 없는 이점을 통해 LTFET는 작은 C를 얻습니다. gg 그리고 좋은 주파수 특성. f T LTFET의 GBW는 8.7GHz와 2.1GHz에 각각 도달합니다. UTFET의 정전 용량 특성은 TGTFET 및 LTFET에 비해 열등합니다. 다이렉트 게이트/드레인이 겹치기 때문입니다. 결과적으로 f의 최대값은 T UTFET의 GBW는 각각 4.1GHz와 0.5GHz에만 도달할 수 있습니다.

The characteristic curves of a f T 그리고 b GBW of TGTFET, UTFET, and LTFET versus V g V에서 d = 0.5 V

In this paper, a T-shape gate dual-source tunnel field-effect transistor (TGTFET) with good performance is proposed and investigated. The structure, mechanism, and the influence of device parameter on the characteristic of TGTFET are discussed. In addition, the characteristics of TGTFET, UTFET, and LTFET are discussed and compared in this paper. The dual-source regions are introduced to double the area of the tunneling junction. The gate overlap and the n+ pockets can obviously enhance the tunneling efficiency of the tunneling junction in TGTFET. Finally, the TGTFET with impressive characteristics (I ON = 8.1 × 10 −5 A/μm, I ON /나 OFF = 6.7 × 10 10 and SSmin = 24.4 mV/dec) is obtained. At the same time, TGTFET is robust to DIBL, which means TGTFET can exhibit a good and stable performance in a larger applied voltage dynamic range. Furthermore, the analog/RF performance of TGTFET is studied and compared with UTFET and LTFET. The key parameter such as input/output characteristics, capacitance characteristics, GBW, and f T are analyzed. Benefiting from the no direct overlap between the gate and drain, TGTFET obtains a relatively small C gd 및 C gg . Finally, TGTFET with remarkable frequency characteristics (f T = 11.9 GHz and GBW = 2.3 GHz) is obtained. As a conclusion, it is expected that TGTFET can be one of the promising alternatives for the next generation of device in low-power and analog/RF applications.

Gate to drain capacitance

Gate to source capacitance

Cut-off frequency

Gain bandwidth

Output conductance

Transconductance

Height of the channel layer

Height of the gate electrode

Height of the source layer

L-shape gate tunnel field-effect transistor

Doping concentration of n+ drain

Doping concentration of n+ pocket

Doping concentration of p+ source

Doping concentration of p− substrate

Output impedance

T-shape gate dual-source tunnel field-effect transistor

Thickness of the HfO2 gate dielectric

Thickness of n+ pocket

U-shape gate tunnel field-effect transistor

Drain to source voltage

Gate to source voltage

Width of the gate electrode

나노물질

초록 본 논문에서는 생체분자 검출을 위한 바이오센서 기반의 유전체 변조 이중 소스 트렌치 게이트 터널 FET(DM-DSTGTFET)를 제안한다. DM-DSTGTFET는 이중 소스 및 트렌치 게이트를 채택하여 온 전류를 향상시키고 양방향 전류를 생성합니다. 제안된 구조에서 생체 분자를 채우기 위해 1nm 게이트 산화물 위에 두 개의 공동이 에칭됩니다. TCAD(Technology Computer-Aided Design)의 2D 시뮬레이션은 민감도 연구의 분석을 위해 채택되었습니다. 결과는 낮은 공급 전압에서 DM-DSTGTFET의

초록 본 논문에서는 양방향 게이트 제어 S/D 대칭 및 교체 가능한 양방향 터널 전계 효과 트랜지스터(B-TFET)를 제안하여 기존의 비대칭 TFET에 비해 양방향 스위칭 특성 및 CMOS 집적 회로와의 호환성의 이점을 보여줍니다. N+의 도핑 농도와 같은 구조적 매개변수의 영향 지역 및 P+ 지역, N+의 길이 고유 영역의 영역 및 길이, 장치 성능, 예:전달 특성, I 켜기 –나 꺼짐 비율 및 하위 임계값 스윙, 내부 메커니즘에 대해 자세히 논의하고 설명합니다. 소개 전력 소비는 집적 회로 산업의 주요 문제 중 하나입니다