Verilog 수학 함수는 상수 표현식 대신 사용할 수 있으며 정수 그리고 진짜 수학. 정수 수학 함수 함수 $clog2 log2의 상한선을 반환합니다. 주어진 인수의. 이것은 일반적으로 주어진 크기의 메모리를 처리하는 데 필요한 최소 너비를 계산하는 데 사용됩니다. 예를 들어 디자인에 7개의 병렬 가산기가 있는 경우 7개의 가산기를 모두 나타내는 데 필요한 최소 비트 수는 $clog2입니다. 7 중 3을 산출합니다. module des #(parameter NUM_UNITS = 7) // Use of

디스플레이 시스템 작업은 주로 로그 파일에서 시뮬레이션 흐름을 추적하기 위해 정보 및 디버그 메시지를 표시하는 데 사용되며 더 빠른 디버그에도 도움이 됩니다. 값을 인쇄할 수 있는 다양한 표시 작업 및 형식 그룹이 있습니다. 표시/쓰기 작업 구문 $display 둘 다 및 $write 인수 목록에 나타나는 순서대로 인수를 표시합니다. $display(<list_of_arguments>); $write(<list_of_arguments>); $write 줄 바꿈 문자 를 추가하지 않습니다.

클록은 서로 다른 블록이 서로 동기화될 수 있도록 하므로 디지털 회로를 구축하는 데 기본입니다. 시계의 속성 디지털 시계의 주요 속성은 주파수입니다. 시계 주기를 결정합니다. , 듀티 사이클 및 시계 단계 다른 시계와 관련하여. 시계 기간 빈도는 특정 기간에 몇 개의 사이클을 찾을 수 있는지 나타냅니다. 따라서 시계 주기는 1주기를 완료하는 데 걸리는 시간입니다. 클록 듀티 사이클 클록이 해당 기간에 비해 높은 시간이 듀티 사이클을 정의합니다. 시계 단계 시계의 한 주기를 360도의 완전한 원으로 볼 수 있다면 다른

Verilog 디자인과 테스트벤치는 일반적으로 always로 구성된 많은 코드 라인을 가지고 있습니다. 또는 initial 블록, 연속 할당 및 시뮬레이션 과정에서 다른 시간에 활성화되는 기타 절차적 진술. Verilog 모델에서 신호 값의 모든 변경은 업데이트 이벤트로 간주됩니다. . always과 같은 프로세스 및 assign 이러한 업데이트 이벤트에 민감한 블록은 임의의 순서로 평가되며 평가 이벤트라고 합니다. . 이러한 이벤트는 서로 다른 시간에 발생할 수 있으므로 이벤트 대기열로 일정을 예약하여 더 잘 관리되고 올바른 실

Verilog 시뮬레이션은 시뮬레이터가 #1이 시간 측면에서 무엇을 의미하는지 알아야 하기 때문에 시간이 정의되는 방식에 따라 다릅니다. `timescale 컴파일러 지시문은 뒤에 오는 모듈의 시간 단위와 정밀도를 지정합니다. 구문 `timescale <time_unit>/<time_precision> // Example `timescale 1ns/1ps `timescale 10us/100ns `timescale 10ns/1ns time_unit time_precision 동안 지연 및 시뮬레

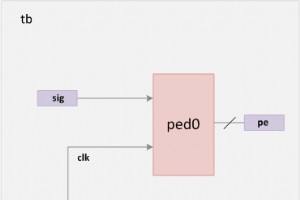

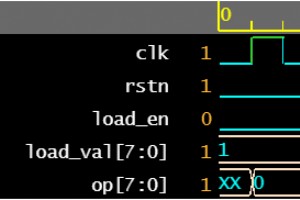

Verilog는 하드웨어 설명 언어이며 설계자가 RTL 설계를 시뮬레이션하여 논리 게이트로 변환할 필요가 없습니다. 시뮬레이션이 필요한 이유는 무엇입니까? 시뮬레이션은 RTL 코드가 의도한 대로 동작하는지 확인하기 위해 다른 시간에 다른 입력 자극을 설계에 적용하는 기술입니다. 기본적으로 시뮬레이션은 설계의 견고성을 검증하기 위해 잘 따라야 하는 기술입니다. 또한 가공된 칩이 실제 세계에서 사용되는 방식과 다양한 입력에 반응하는 방식과 유사합니다. 예를 들어, 위의 디자인은 출력 pe 보여진 바와 같이. 시뮬레이션을 통해

nand과 같은 표준 Verilog 프리미티브 및 not 복잡한 논리를 표현하기에는 항상 쉽거나 충분하지 않을 수 있습니다. UDP라는 새로운 기본 요소 또는 사용자 정의 프리미티브 조합 논리 또는 순차 논리를 모델링하도록 정의할 수 있습니다. 모든 UDP에는 0, 1 또는 X가 될 수 있고 Z가 될 수 없는 정확히 하나의 출력이 있습니다(지원되지 않음). Z 값을 갖는 모든 입력은 X로 처리됩니다. Verilog UDP 기호 Verilog 사용자 정의 프리미티브는 module과 동일한 수준에서 작성할 수 있습니다. 정의, 그러

Verilog는 또한 트랜지스터 레벨 모델링에 대한 지원을 제공하지만, 회로의 복잡성으로 인해 스위치 레벨 모델링을 사용하는 것보다 더 높은 수준의 추상화로 이동해야 하기 때문에 오늘날 디자이너는 거의 사용하지 않습니다. NMOS/PMOS module des (input d, ctrl, output outn, outp); nmos (outn, d, ctrl); pmos (outp, d, ctrl); endmodule module tb; reg d, ctrl; wire outn,

디지털 요소는 이진 항목이며 0과 1의 두 값 중 하나만 유지할 수 있습니다. 그러나 0에서 1로, 1에서 0으로의 전환에는 전환 지연이 있으므로 각 게이트 요소도 값을 입력에서 출력으로 전파합니다. 예를 들어, 2개의 입력 AND 게이트는 두 입력이 모두 1이 되면 출력을 1로 전환하고 입력 중 하나가 0이 되면 다시 0으로 전환해야 합니다. 이러한 게이트 및 핀 대 핀 지연은 로직 프리미티브를 인스턴스화할 때 Verilog에서 지정할 수 있습니다. 상승, 하강 및 종료 지연 게이트의 출력이 어떤 값에서 1로 변하는 데 걸리

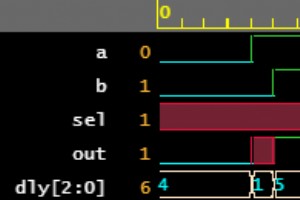

주요 기본 제공 프리미티브 중 일부는 이전 기사에서 논의되었으며 간단한 and 사용에 대한 몇 가지 실용적인 예를 보는 것이 좋습니다. , nor 및 not 게이트. 게이트를 사용하여 Verilog 코드를 작성하려면 요소를 연결하는 방법을 알아야 합니다. 이것은 요소의 선택과 연결이 합성 도구에 맡겨지는 경우의 행동 설명과 매우 다릅니다. 예시 #1:2x1 멀티플렉서 모듈의 출력은 wire 유형이어야 합니다. 프리미티브의 출력 포트에 연결하기 위해. module mux_2x1 ( input a, b, sel,

대부분의 디지털 디자인은 RTL과 같은 더 높은 수준의 추상화에서 수행되지만 및과 같은 조합 요소를 사용하여 더 낮은 수준에서 더 작은 결정론적 회로를 구축하는 것이 직관적이 되는 경우가 있습니다. 및 또는 . 이 수준에서 수행되는 모델링을 일반적으로 게이트 수준 모델링이라고 합니다. 게이트를 포함하므로 하드웨어 회로도와 Verilog 코드 간에 일대일 관계가 있습니다. Verilog는 primitives로 알려진 몇 가지 기본 논리 게이트를 지원합니다. 이미 사전 정의되어 있으므로 모듈처럼 인스턴스화할 수 있습니다. 및/또는/X

대부분의 프로그래밍 언어에는 scope라는 특징이 있습니다. 변수 및 메서드에 대한 특정 코드 섹션의 가시성을 정의합니다. 범위는 네임스페이스를 정의합니다. 동일한 네임스페이스 내에서 서로 다른 개체 이름 간의 충돌을 방지합니다. Verilog는 모듈, 기능, 작업, 명명된 블록 및 생성 블록에 대한 새로운 범위를 정의합니다. module tb; reg signal; // Another variable cannot be declared with // an already existing name in the sam

Verilog 지연 문은 할당 연산자의 왼쪽 또는 오른쪽에 지연을 지정할 수 있습니다. 과제 간 지연 // Delay is specified on the left side #<delay> <LHS> = <RHS> 간 과제 지연 문에는 할당 연산자의 LHS에 지연 값이 있습니다. 이는 명령문 자체가 이후 실행되었음을 나타냅니다. 지연이 만료되며 가장 일반적으로 사용되는 지연 제어 형식입니다. module tb; reg a, b, c, q; initial begin $

Verilog에는 두 가지 유형의 타이밍 컨트롤이 있습니다 - 지연 및 이벤트 표현. 지연 제어는 시뮬레이터가 명령문을 만나는 시간과 실제로 실행하는 시간 사이에 지연을 추가하는 방법일 뿐입니다. 이벤트 표현 순 또는 변수의 값 변경이 될 수 있는 시뮬레이션 이벤트가 발생할 때까지 명령문이 지연되도록 허용합니다(암시적 이벤트 ) 또는 다른 프로시저에서 트리거되는 명시적으로 명명된 이벤트입니다. 시뮬레이션 시간은 다음 방법 중 하나로 앞당길 수 있습니다. 내부 지연을 갖도록 모델링된 게이트 및 네트도 시뮬레이션 시간을 앞당깁니다

Verilog는 본질적으로 컴파일러가 특정 방식으로 코드를 처리하도록 지시하는 몇 가지 컴파일러 지시문을 지원합니다. 예를 들어, 코드의 일부는 특정 기능의 구현을 나타낼 수 있으며 기능이 사용되지 않는 경우 디자인에 코드를 포함하지 않는 방법이 있어야 합니다. 이것은 조건부로 해결할 수 있습니다. 디자이너가 컴파일러 지시문 내에서 코드를 래핑할 수 있는 컴파일에서 지정된 명명된 플래그가 설정될 때 컴파일을 위해 코드를 포함하거나 제외하도록 컴파일러에 지시합니다. 구문 Verilog `ifdef을 사용하여 조건부 컴파일을 수행할

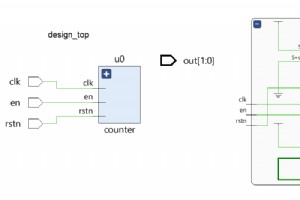

매개변수는 다른 사양으로 모듈을 재사용할 수 있도록 하는 Verilog 구성입니다. 예를 들어, 4비트 가산기는 비트 수에 대한 값을 허용하도록 매개변수화될 수 있으며 모듈 인스턴스화 중에 새 매개변수 값이 전달될 수 있습니다. 따라서 N비트 가산기는 4비트, 8비트 또는 16비트 가산기가 될 수 있습니다. 함수 호출 중에 전달되는 함수에 대한 인수와 같습니다. parameter MSB = 7; // MSB is a parameter with a constant value 7 paramet

function 입력에 대해 일부 처리를 수행하고 단일 값을 반환하는 반면 task 더 일반적이며 여러 결과 값을 계산하고 출력을 사용하여 반환할 수 있습니다. 그리고 inout 유형 인수. 작업에는 @와 같이 시간이 많이 소요되는 시뮬레이션 요소가 포함될 수 있습니다. , 포제지 다른 사람. 구문 작업은 포트 목록에 인수 집합을 가질 필요가 없으며, 이 경우 비워 둘 수 있습니다. // Style 1 task [name]; input [port_list]; inout [port_list]; outpu

종종 우리는 RTL 내에서 반복적이고 여러 번 호출되는 특정 코드 조각을 찾습니다. 대부분 시뮬레이션 시간을 소비하지 않으며 다른 데이터 값으로 수행해야 하는 복잡한 계산이 포함될 수 있습니다. 이러한 경우 function을 선언할 수 있습니다. 함수 내부에 반복적인 코드를 배치하고 결과를 반환하도록 합니다. 이제 함수 호출만 하면 되므로 이렇게 하면 RTL의 줄 수가 크게 줄어듭니다. 계산을 수행해야 하는 데이터를 전달합니다. 사실 이것은 C의 함수와 매우 유사합니다. 함수의 목적은 표현식에 사용할 값을 반환하는 것입니다. 함수

case 문은 주어진 표현식이 목록의 다른 표현식 중 하나와 일치하는지 확인하고 그에 따라 분기합니다. 일반적으로 멀티플렉서를 구현하는 데 사용됩니다. if-else 구문은 확인해야 할 조건이 많고 멀티플렉서 대신 우선 순위 인코더로 합성되는 경우 적합하지 않을 수 있습니다. 구문 Verilog 케이스 명령문은 case로 시작합니다. 키워드이고 endcase로 끝남 예어. 괄호 안의 표현식은 정확히 한 번 평가되고 작성된 순서대로 대안 목록과 비교되며 대안이 주어진 표현식과 일치하는 명령문이 실행됩니다. 여러 문의 블록은 그룹화되

for 루프는 소프트웨어에서 가장 널리 사용되는 루프이지만 주로 복제하는 데 사용됩니다. Verilog의 하드웨어 로직. for 뒤에 숨겨진 아이디어 루프는 주어진 조건이 참인 한 루프 내에서 주어진 명령문 세트를 반복하는 것입니다. 이것은 while와 매우 유사합니다. 루프이지만 반복자를 사용할 수 있고 조건이 이 반복자의 값에 따라 달라지는 컨텍스트에서 더 많이 사용됩니다. 구문 for (<initial_condition>; <condition>; <step_assignment>) be

verilog