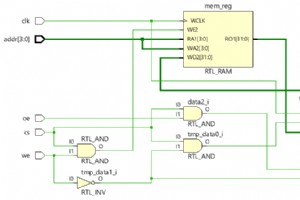

디자인 module single_port_sync_ram # (parameter ADDR_WIDTH = 4, parameter DATA_WIDTH = 32, parameter DEPTH = 16 ) ( input clk, input [ADDR_WIDTH-1:0] addr, inout [DATA_WIDTH-1:0] data, input cs, input we, input oe ); reg [

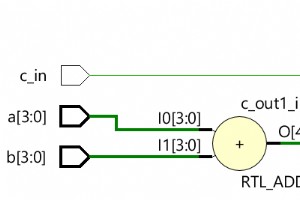

가산기는 두 숫자의 덧셈을 수행하는 디지털 구성 요소입니다. 프로세서의 ALU 내부의 주요 구성 요소이며 주소, 테이블 인덱스, 버퍼 포인터 및 추가가 필요한 다른 많은 위치를 증가시키는 데 사용됩니다. 전가산기는 다른 입력 이진수와 함께 캐리 입력을 추가하여 합계 및 캐리 출력을 생성합니다. 진실의 표 A 나 신 사냥꾼 합 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1 디자인 아래는 4비트 폭인

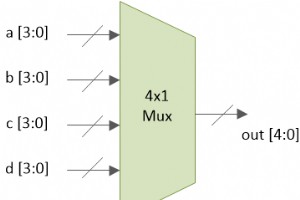

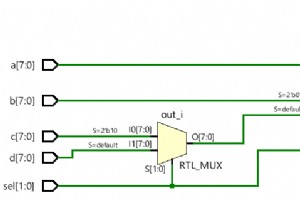

먹스 또는 멀티플렉서란 무엇입니까? 멀티플렉서 또는 mux 요컨대 선택 신호를 기반으로 N 입력 중 하나에서 출력으로 데이터를 전송하는 디지털 요소입니다. 아래에 표시된 경우는 N이 4인 경우입니다. 예를 들어, 4비트 멀티플렉서는 선택 신호를 사용하여 각 입력을 출력으로 전송할 수 있는 4비트 각각의 N 입력을 갖습니다. sel은 2비트 입력이며 4개의 값을 가질 수 있습니다. 선택 라인의 각 값은 입력 중 하나를 출력 핀 아웃으로 보낼 수 있도록 합니다. sel a b c d out

디자인 module pr_en ( input [7:0] a, input [7:0] b, input [7:0] c, input [7:0] d, input [1:0] sel, output reg [7:0] out); always @ (a or b or c or d or sel) begin if (sel == 2b00) out <= a; else if

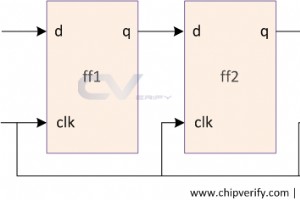

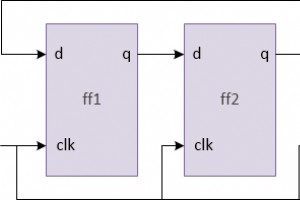

디지털 전자 제품에서 시프트 레지스터 출력 핀이 q인 플립플롭의 캐스케이드입니다. 한 플롭의 데이터 입력 핀(d)이 다음 플롭에 연결됩니다. 모든 플롭이 동일한 클럭에서 작동하기 때문에 시프트 레지스터에 저장된 비트 어레이는 한 위치만큼 이동합니다. 예를 들어, 5비트 오른쪽 시프트 레지스터의 초기 값이 10110이고 시프트 레지스터에 대한 입력이 0에 연결되어 있으면 다음 패턴은 01011이 되고 다음 패턴은 00101이 됩니다. 디자인 이 시프트 레지스터 디자인에는 5개의 입력과 1개의 n비트 출력이 있으며 디자인은 par

디자인 module gray_ctr # (parameter N = 4) ( input clk, input rstn, output reg [N-1:0] out); reg [N-1:0] q; always @ (posedge clk) begin if (!rstn) begin q <= 0; out <= 0; end else begin q <= q + 1; `ifdef FOR_LOOP for (int i =

디자인 module modN_ctr # (parameter N = 10, parameter WIDTH = 4) ( input clk, input rstn, output reg[WIDTH-1:0] out); always @ (posedge clk) begin if (!rstn) begin out <= 0; end else begin if (out == N-1) out <= 0; else out <

디자인 module johnson_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= ~out[0]; for (int i = 0; i < WIDTH-1; i=i+1) b

디자인 module ring_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= out[0]; for (int i = 0; i < WIDTH-1; i=i+1) begi

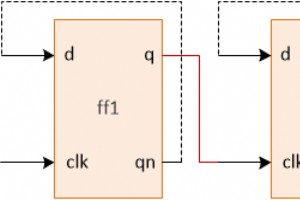

리플 counter는 첫 번째 플롭을 제외한 모든 플롭이 이전 플롭의 출력에 의해 클럭되는 비동기식 카운터입니다. 디자인 module dff ( input d, input clk, input rstn, output reg q, output qn); always @ (posedge clk or negedge rstn) if (!rstn) q <= 0; else

4비트 카운터는 4b0000에서 4h1111로 증가하기 시작한 다음 다시 4b0000으로 롤오버됩니다. 실행 중인 시계가 제공되고 재설정이 높게 유지되는 한 계속 계산됩니다. 롤오버는 최종 추가의 가장 중요한 비트가 폐기될 때 발생합니다. 카운터가 최대값이 4b1111이고 한 번 더 카운트 요청을 받으면 카운터는 5b10000에 도달하려고 시도하지만 4비트만 지원할 수 있으므로 MSB는 폐기되어 0이 됩니다. 0000 0001 0010 ... 1110 1111 rolls over 0000 0001

플립플롭은 클록의 양수 또는 음수 에지 입력에서 데이터를 캡처합니다. 주목해야 할 중요한 점은 다음 클럭 에지까지 클럭 에지 이후 데이터에 어떤 일이 발생하든지 출력에 반영되지 않는다는 것입니다. 래치 반면에 인에이블 핀이 어서트되어 있는 한 출력은 클록 에지에서 캡처하지 않고 입력을 따릅니다. 디자인 이 예에서는 3개의 입력과 1개의 출력이 있는 래치를 만들 것입니다. 입력 d 0 또는 1이 될 수 있는 데이터를 나타냅니다. rstn 액티브 로우 리셋 및 en을 나타냅니다. 입력 데이터를 출력에 래치하는 데 사용되는 활성화를 나

디자인 module tff ( input clk, input rstn, input t, output reg q); always @ (posedge clk) begin if (!rstn) q <= 0; else if (t) q <= ~q; else q <= q; end endmodule 테스트 벤치 module tb; reg clk; reg rstn;

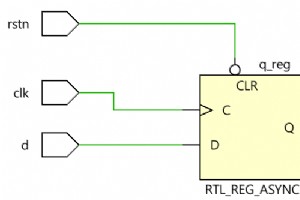

D 플립플롭 입력 핀 d 뒤에 오는 순차 요소입니다. 시계의 주어진 가장자리에서. 디자인 #1:비동기 액티브 로우 리셋 사용 module dff ( input d, input rstn, input clk, output reg q); always @ (posedge clk or negedge rstn) if (!rstn) q <= 0; else q <= d; endmodule

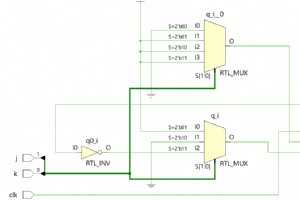

디자인 module jk_ff ( input j, input k, input clk, output q); reg q; always @ (posedge clk) case ({j,k}) 2b00 : q <= q; 2b01 : q <= 0; 2b10 : q <= 1; 2b11 : q <= ~q; endcase endmodule 하드웨어 도

매우 간단한 예를 사용하여 시작하는 것이 항상 가장 좋으며 Hello World ! 이외의 용도에 가장 적합한 것은 없습니다. // Single line comments start with double forward slash // // Verilog code is always written inside modules, and each module represents a digital block with some functionality module tb; // Initial block is another constr

Verilog에는 파일을 열고, 값을 파일로 출력하고, 파일에서 값을 읽고, 다른 변수로 로드하고, 파일을 닫을 수 있는 시스템 작업 및 기능이 있습니다. 파일 열기 및 닫기 module tb; // Declare a variable to store the file handler integer fd; initial begin // Open a new file by the name my_file.txt // with write permissions, and store the file // handler

기본 타임스케일 Verilog 모듈에는 모듈 이전에 정의된 시간 척도가 있어야 하지만 시뮬레이터는 기본 시간 척도를 삽입할 수 있습니다. Verilog의 정교한 계층 구조의 모든 범위에 적용되는 실제 시간 척도는 시스템 작업 $printtimescale을 사용하여 인쇄할 수 있습니다. 범위를 인수로 허용합니다. module tb; initial begin // Print timescale of this module $printtimescale(tb); // $printtimescale($root); endendmodu

Verilog timescale 지시문은 시뮬레이션을 위한 시간 단위와 정밀도를 지정합니다. Verilog $timeformat 시스템 기능은 %t를 지정합니다. $display과 같은 표시 문의 형식 지정자 보고 스타일 및 $strobe . 구문 $timeformat(<unit_number>, <precision>, <suffix_string>, <minimum field width>); 단위_번호 모든 `timescale 중에서 가장 작은 시간 정밀도입니다. 소스 코

Verilog 수학 함수는 상수 표현식 대신 사용할 수 있으며 정수 그리고 진짜 수학. 정수 수학 함수 함수 $clog2 log2의 상한선을 반환합니다. 주어진 인수의. 이것은 일반적으로 주어진 크기의 메모리를 처리하는 데 필요한 최소 너비를 계산하는 데 사용됩니다. 예를 들어 디자인에 7개의 병렬 가산기가 있는 경우 7개의 가산기를 모두 나타내는 데 필요한 최소 비트 수는 $clog2입니다. 7 중 3을 산출합니다. module des #(parameter NUM_UNITS = 7) // Use of

verilog